# **Programmable Duty Cycle Controller**

### **DESCRIPTION**

The Si9118/Si9119 are a BiC/DMOS current-mode pulse width modulation (PWM) controller ICs for high-frequency dc/dc converters. Single-ended topologies (forward and flyback) can be implemented at frequencies up to 1 MHz. The controller operates in constant frequency mode during the full load and automatically switches to pulse skipping mode under light load to maintain high efficiency throughout the full load range. The maximum duty cycle is easily programmed with a resistor divider for optimum control.

The push-pull output driver provides high-speed switching to external MOSPOWER devices large enough to supply 50 W of output power. Shoot-through current for internal push-pull stage is almost eliminated to minimize guiescent supply current.

The push-pull output driver provides high-speed switching to external MOSPOWER devices large enough to supply 50 W of output power. Shoot-through current for internal push-pull stage is almost eliminated to minimize quiescent supply current.

The high-voltage DMOS transistor permits direct operation from bus voltages of up to 200 V. Other features include a 1.5 % accurate voltage reference, 2.7 MHz bandwidth error amplifier, standby mode, soft-start and undervoltage lockout circuits.

The Si9118/Si9119 are available in both standard and lead (Pb)-free packages.

### **FEATURES**

- 10 to 200 V Input Range

- **Current-Mode Control**

- Internal Start-Up Circuit

- **Buffer Slope Compensation Voltage**

- Soft-Start

- 2.7 MHz Error Amp

- 500 mA Output Drive Current

- Light Load Frequency Fold-Back

- Low Quiescent Current

- Programmable Maximum Duty Cycle, with 80 % as Default

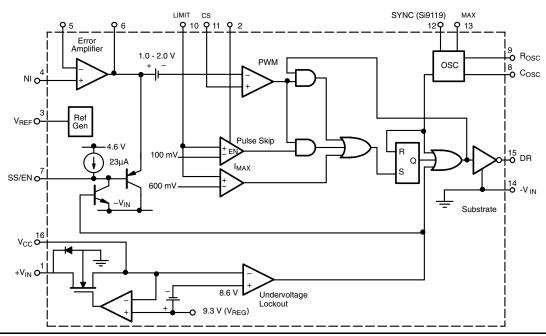

### **FUNCTIONAL BLOCK DIAGRAM**

Document Number: 70815 S11-0975-Rev. E, 16-May-11

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> = 25 °C, unless otherwise noted)       |        |                                |      |  |  |

|---------------------------------------------------------------------------------|--------|--------------------------------|------|--|--|

| Parameter                                                                       | Symbol | Limit                          | Unit |  |  |

| Voltage Reference V <sub>CC</sub> to V <sub>IN</sub>                            |        | 18                             |      |  |  |

| +V <sub>IN</sub> ( Note: V <sub>CC</sub> < + V <sub>IN</sub> + 0.3 V)           |        | 200                            | ] ,  |  |  |

| Logic Input (SYNC)                                                              |        | - 0.3 to V <sub>cc</sub> + 0.3 | - V  |  |  |

| Linear Input (FB, I <sub>CS</sub> , I <sub>LIMIT</sub> , SS/EN)                 |        | - 0.3 to V <sub>cc</sub> + 0.3 | 1    |  |  |

| HV Pre-Regulator Input Current (continuous)                                     |        | 5                              | mA   |  |  |

| Storage Temperature                                                             |        | - 65 to 150                    | °C   |  |  |

| Operating Temperature                                                           |        | - 40 to 85                     |      |  |  |

| D <sub>MAX</sub>                                                                |        | 3.2                            | V    |  |  |

| Junction Temperature (T <sub>J</sub> )                                          |        | 150                            | °C   |  |  |

| Power Dissipation (Package) <sup>a</sup><br>16-Pin SOIC (Y Suffix) <sup>b</sup> |        | 900                            | mW   |  |  |

| Thermal Impedance (θ <sub>JA</sub> )<br>16-Pin SOIC                             |        | 140                            | °C/W |  |  |

### Notes:

- a. Device mounted with all leads soldered or welded to PC board. b. Derate 7.2 mW/°C above 25 °C.

- \* Exposure to Absolute Maximum rating conditions for extended periods may affect device reliability. Stresses above Absolute Maximum rating may cause permanent damage. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

| RECOMMENDED OPERATING RANGE                          |                          |      |  |  |

|------------------------------------------------------|--------------------------|------|--|--|

| Parameter                                            | Limit                    | Unit |  |  |

| Voltage Reference V <sub>cc</sub> to V <sub>IN</sub> | 10 to 16.5               |      |  |  |

| +V <sub>IN</sub>                                     | 10 to 200                | V    |  |  |

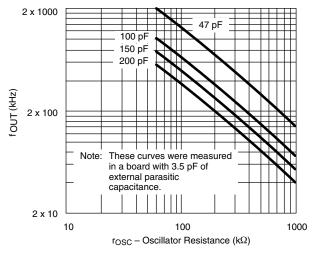

| fosc                                                 | 40 kHz to 1 MHz          |      |  |  |

| Rosc                                                 | 56 kΩ to 1 MΩ            |      |  |  |

| C <sub>OSC</sub>                                     | 47 to 200                | pF   |  |  |

| Linear Inputs                                        | 0 to V <sub>cc</sub> - 4 | V    |  |  |

| Digital Inputs                                       | 0 to V <sub>cc</sub>     | V    |  |  |

| SPECIFICATIONS        |                         |                                                                |                                            |      |       |      |      |  |

|-----------------------|-------------------------|----------------------------------------------------------------|--------------------------------------------|------|-------|------|------|--|

|                       |                         | Test Conditions  Limits  D Suffix - 40 to 85 °C                | Test Conditions Unless Otherwise Specified |      |       |      |      |  |

| Parameter             | Symbol                  | $- V_{IN} = 0 \text{ V}, \ V_{CC} = 10 \text{ V}$              | Temp.a                                     | Min. | Typ.b | Max. | Unit |  |

| Reference             |                         |                                                                |                                            |      |       |      |      |  |

|                       |                         | OSC Disabled, T <sub>A</sub> = 25 °C                           | Room                                       | 3.94 | 4.0   | 4.06 |      |  |

| Output Voltage        | $V_{REF}$               | OSC Disabled, Over Voltage and Temperature Ranges <sup>c</sup> | Full                                       | 3.88 | 4.0   | 4.12 | V    |  |

| Short Circuit Current | I <sub>SREF</sub>       | $V_{REF} = -V_{IN}$                                            |                                            |      | - 30  | - 5  | mA   |  |

| Load Regulation       | $\Delta V_R/\Delta I_R$ | I <sub>REF</sub> = 0 to - 1mA                                  |                                            |      | 10    | 40   | mV   |  |

| SPECIFICATIONS                                              |                               |                                                                                                                                      |        |                                         |                   |       |        |  |

|-------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------|-------------------|-------|--------|--|

|                                                             |                               | Test Conditions                                                                                                                      |        | <b>Limits</b><br>D Suffix - 40 to 85 °C |                   |       |        |  |

| Parameter                                                   | Symbol                        | Unless Otherwise Specified $- V_{IN} = 0 V, V_{CC} = 10 V$                                                                           | Temp.a | Min.                                    | Typ. <sup>b</sup> | Max.  | Unit   |  |

| Oscillator                                                  |                               |                                                                                                                                      |        |                                         |                   | •     |        |  |

| , d                                                         | fosc                          | $R_{OSC} = 374 \text{ k}\Omega, C_{OSC} = 200 \text{ pF}$                                                                            | =      | 90                                      | 100               | 110   | 1,11-  |  |

| Initial Accuracy <sup>d</sup>                               | f <sub>OSC</sub> <sup>c</sup> | $R_{OSC} = 70 \text{ k}\Omega, C_{OSC} = 200 \text{ pF}$                                                                             |        | 450                                     | 500               | 550   | kHz    |  |

| Voltage Stability <sup>c</sup>                              | Δf/f                          | $R_{OSC} = 70 \text{ k}\Omega, C_{OSC} = 200 \text{ pF}$<br>$\Delta f/f = [f(16.5 \text{ V}) - f(9.5 \text{ V})] / f(9.5 \text{ V})$ |        |                                         | 1                 | 2     | %      |  |

| Temperature Coefficient <sup>c</sup>                        | OSC TC                        | - $40 \le T_A \le 85$ °C, $f_{OSC} = 100$ kH                                                                                         | łz     |                                         | 200               | 500   | ppm/°C |  |

| Sync High Pulse Width (Si9119)                              |                               |                                                                                                                                      |        | 200                                     |                   |       |        |  |

| Sync Low Pulse Width (Si9119)                               |                               |                                                                                                                                      |        | 200                                     |                   |       | ns     |  |

| Sync Rise/Fall Time (Si9119)                                |                               |                                                                                                                                      |        |                                         |                   | 200   |        |  |

| Sync Logic Low (Si9119)                                     | V <sub>IL</sub>               |                                                                                                                                      |        |                                         |                   | 0.8   | V      |  |

| Sync Logic High (Si9119)                                    | V <sub>IH</sub>               |                                                                                                                                      |        | 4                                       |                   |       | V      |  |

| Sync Range <sup>c</sup> (Si9119)                            | f <sub>EXT</sub>              |                                                                                                                                      |        | 1.05 x f <sub>OSC</sub>                 |                   |       | kHz    |  |

| PWM/PSM                                                     | l                             |                                                                                                                                      |        |                                         |                   | l     | L      |  |

| PWM/PSM Logic High                                          | V <sub>IH</sub>               |                                                                                                                                      |        | 4                                       |                   |       | .,,    |  |

| PWM/PSM Logic Low                                           | V <sub>IL</sub>               |                                                                                                                                      |        |                                         |                   | 0.8   | V      |  |

| D <sub>MAX</sub>                                            |                               |                                                                                                                                      |        |                                         |                   | l     |        |  |

| Accuracy                                                    |                               | f <sub>OSC</sub> = 100 kHz with 1 % Resisto                                                                                          | or     |                                         | ± 10              |       | %      |  |

| Error Amplifier (OSC Disabled)                              |                               |                                                                                                                                      |        |                                         |                   | •     | '      |  |

| Input BIAS Current                                          | I <sub>FB</sub>               | $V_{FB} = 5 \text{ V}, \text{ NI} = V_{REF}$                                                                                         |        |                                         | < 1.0             | ± 200 | nA     |  |

| Input OFFSET Voltage                                        | V <sub>OS2</sub>              |                                                                                                                                      |        |                                         | ± 5               | ± 25  | mV     |  |

| Open Loop Voltage Gain <sup>c</sup>                         | A <sub>VOL</sub>              |                                                                                                                                      |        | 65                                      | 80                |       | dB     |  |

| Unity Gain Bandwidth <sup>c</sup>                           | BW                            |                                                                                                                                      |        | 1.8                                     | 2.7               |       | MHz    |  |

| Outrant Ourseast                                            |                               | Source (V <sub>FB</sub> = 3.5 V, NI = V <sub>REF</sub>                                                                               | ·)     | - 1.0                                   | - 2.7             |       | A      |  |

| Output Current                                              | l <sub>OUT</sub>              | Sink ( $V_{FB} = 4.5 \text{ V}$ , $NI = V_{REF}$ )                                                                                   |        | 1.0                                     | 2.4               |       | mA .   |  |

| Power Supply Rejection                                      | PSRR                          | 10 V ≤ V <sub>CC</sub> ≤ 16.5 V                                                                                                      |        | 50                                      | 80                |       | dB     |  |

| Pre-Regulator/Start-up                                      |                               |                                                                                                                                      |        |                                         |                   | •     |        |  |

| Input Voltage <sup>c</sup>                                  | +V <sub>IN</sub>              | I <sub>IN</sub> = 10 μA                                                                                                              | Room   | 200                                     |                   |       | V      |  |

| Input Leakage Current                                       | +I <sub>IN</sub>              | V <sub>CC</sub> ≥ 10 V                                                                                                               | Room   |                                         |                   | 10    | μΑ     |  |

| Pre-Regulator Start-Up Current                              | I <sub>START</sub>            | Pulse Width ≤ 300 μs, V <sub>CC</sub> = V <sub>ULVO</sub>                                                                            | Room   | 8                                       | 15                |       | mA     |  |

| V <sub>CC</sub> Pre-Regulator Turn-Off<br>Threshold Voltage | V <sub>REG</sub>              | I <sub>PRE_REGULATOR</sub> = 15 μA                                                                                                   | Room   | 8.7                                     | 9.3               | 9.8   |        |  |

| Undervoltage Lockout                                        | V <sub>UVLO</sub>             |                                                                                                                                      | Room   | 8.0                                     | 8.6               | 9.3   | ٧      |  |

| V <sub>REG</sub> - V <sub>UVLO</sub>                        | V <sub>DELTA</sub>            |                                                                                                                                      | Room   | 0.3                                     | 0.7               |       |        |  |

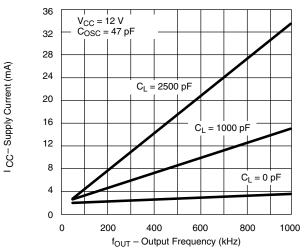

| Supply                                                      |                               |                                                                                                                                      | •      |                                         |                   | •     |        |  |

| Supply Current                                              | I <sub>CC</sub>               | C <sub>LOAD</sub> ≤ 50 pF, f <sub>OSC</sub> = 100 kHZ                                                                                | 7      |                                         | 1.9               | 3.0   | mA     |  |

| SPECIFICATIONS                             |                       |                                                    |                         |                                                |                   |            |      |

|--------------------------------------------|-----------------------|----------------------------------------------------|-------------------------|------------------------------------------------|-------------------|------------|------|

|                                            |                       | Test Conditions Unless Otherwise Specified         |                         | Limits<br>D Suffix - 40 to 85 °C               |                   |            |      |

| Parameter                                  | Symbol                | $-V_{IN} = 0 \text{ V}, V_{CC} = 10 \text{ V}$     | Temp.a                  | Min.                                           | Typ. <sup>b</sup> | Max.       | Unit |

| Protection                                 |                       |                                                    |                         |                                                |                   |            |      |

| Current Limit Treshold Voltage             | V <sub>I(Limit)</sub> | $V_{FB} = 0$ , $NI = V_{REF}$                      |                         | 0.5                                            | 0.6               | 0.7        | ٧    |

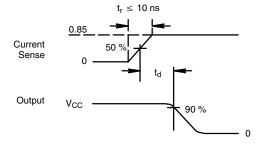

| Current Limit Delay to Output <sup>c</sup> | t <sub>d</sub>        | V <sub>SENSE</sub> 0.85 V, See Figure 1            |                         |                                                | 77                | 100        | ns   |

| Soft-Start Current                         | I <sub>SS</sub>       |                                                    |                         | - 12                                           | - 23              | - 30       | μΑ   |

| Output Inhibit Voltage                     | V <sub>SS(off)</sub>  | Soft-Start Voltage to Disable Driver Output        |                         | 0.5                                            | 1.26              |            | ٧    |

| Pulse Skipping Threshold<br>Voltage        | V <sub>PS</sub>       |                                                    |                         | 80                                             | 100               | 120        | mV   |

| Mosfet Driver                              |                       |                                                    |                         |                                                |                   |            |      |

| Output High Voltage                        | V <sub>OH</sub>       | I <sub>OUT</sub> = - 10 mA                         | Room<br>Full            | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.5 |                   |            | V    |

| Output Low Voltage                         | V <sub>OL</sub>       | I <sub>OUT</sub> = 10 mA                           | Room<br>Full            |                                                |                   | 0.3<br>0.5 | ľ    |

| Output Resistance <sup>c</sup>             | R <sub>OUT</sub>      | I <sub>OUT</sub> = 10 mA, Source or Sink Room Full |                         |                                                | 20<br>25          | 30<br>50   | Ω    |

| Rise Time <sup>c</sup>                     | t <sub>r</sub>        | C <sub>1</sub> = 500 pF                            |                         |                                                | 40                | 75         | ns   |

| Fall Time <sup>c</sup>                     | t <sub>r</sub>        | υ_ – 300 βι                                        | C <sub>L</sub> = 500 pr |                                                | 40                | 75         | 115  |

### Notes:

- a. Room = 25  $^{\circ}$ C, Full = as determined by the operating temperature suffix.

- b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- c. Guaranteed by design, not subject to production test.

- d.  $C_{STRAY} \le 5 \text{ pF on } C_{OSC}$

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **TIMING WAVEFORMS**

Figure 1.

## **TYPICAL CHARACTERISTICS** ( $T_A = 25 \, ^{\circ}C$ , unless noted)

### **Oscillator Frequency**

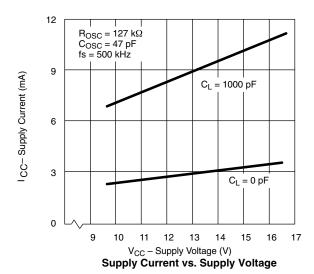

**Supply Current vs. Output Frequency**

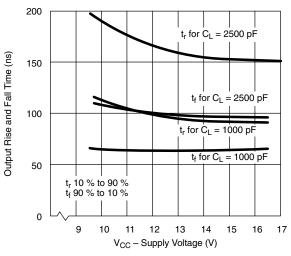

**Output Driver Rise and Fall Time**

1.05

R<sub>OSC</sub> = 56 kΩ

C<sub>OSC</sub> = 100 pF

0.95

0.85

8 9 10 11 12 13 14 15 16 17

V<sub>CC</sub> – Supply Voltage (V)

Switching Frequency vs. Supply Voltage

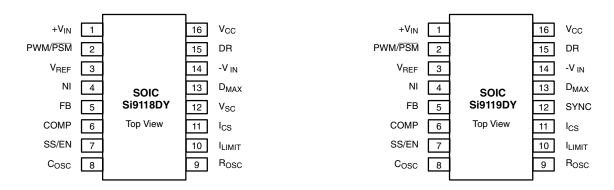

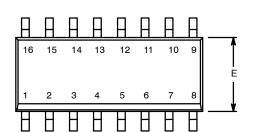

### PIN CONFIGURATIONS AND ORDERING INFORMATION

| ORDERING INFORMATION |                   |         |  |  |

|----------------------|-------------------|---------|--|--|

| Part Number          | Temperature Range | Package |  |  |

| Si9118DY-T1-E3       | - 40 to 85 °C     | SOIC-16 |  |  |

| PIN DESC   | RIPTION                 |                                                                                                                                                                                                                                 |

|------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | Symbol                  | Description                                                                                                                                                                                                                     |

| 1          | +V <sub>IN</sub>        | Input bus voltage ranging from 10 V to 200 V.                                                                                                                                                                                   |

| 2          | PWM/PSM                 | Connected to V <sub>REF</sub> forces the converter into PWM mode. Connected to -V <sub>IN</sub> forces the converter into PSM mode.                                                                                             |

| 3          | V <sub>REF</sub>        | 4 V reference voltage. Decouple with 0.1 μF ceramic capacitor.                                                                                                                                                                  |

| 4          | NI                      | Non-inverting input of an error amplifier.                                                                                                                                                                                      |

| 5          | FB                      | Inverting input of an error amplifier.                                                                                                                                                                                          |

| 6          | COMP                    | Error amplifier output for external compensation network.                                                                                                                                                                       |

| 7          | SS/EN                   | Programmable soft-start with external capacitor or externally controlled disable mode.                                                                                                                                          |

| 8          | C <sub>OSC</sub>        | External capacitor to determine the switching frequency.                                                                                                                                                                        |

| 9          | R <sub>OSC</sub>        | External resistor to determine the switching frequency.                                                                                                                                                                         |

| 10         | I <sub>LIMIT</sub>      | Pulse by pulse peak current limiting pin. When the current sense voltage exceeds the current limit threshold, the gate drive signal is terminated. I <sub>LIMIT</sub> is also used to sense the current in pulse skipping mode. |

| 11         | I <sub>CS</sub>         | Current sense input to control feedback response.                                                                                                                                                                               |

| 12         | SYNC or V <sub>SC</sub> | Si9118: slope compensation pin. Si9119: clock synchronization pin. Logic high to low transition from external signal synchronizes the internal clock frequency.                                                                 |

| 13         | D <sub>MAX</sub>        | Sets the maximum duty cycle. Internally, the maximum duty cycle is clamped to 80 %.                                                                                                                                             |

| 14         | -V <sub>IN</sub>        | Single point ground.                                                                                                                                                                                                            |

| 15         | D <sub>R</sub>          | Gate drive for the external MOSFET switch.                                                                                                                                                                                      |

| 16         | V <sub>CC</sub>         | Supply voltage for the IC after the startup transition.                                                                                                                                                                         |

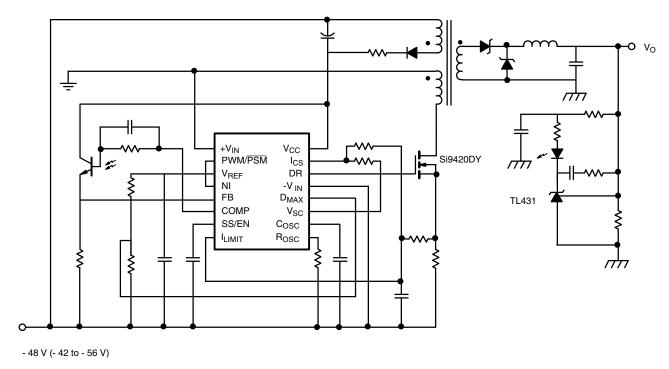

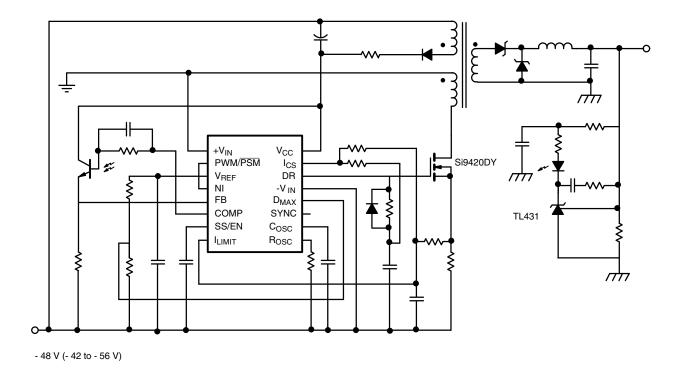

### **STANDARD APPLICATION CIRCUITS**

Figure 2. Si9118 15 W Forward Converter Schematic

Figure 3. Si9119 Forward Converter With External Slope Compensation

### **DETAILED OPERATIONAL DESCRIPTION**

Si9118/Si9119 are designed with internal depletion mode MOSFET capable of powering directly from the high input bus voltage. This feature eliminates the typical external start-up circuit saving valuable space and cost. But, most of all, this feature improves the converter efficiency during full load and has an even greater impact on light load. With an input bus voltage applied to the +V<sub>IN</sub> pin, the V<sub>CC</sub> voltage is regulated to 9.3 V. The UVLO circuit prevents the controller output driver section from turning on, until V<sub>CC</sub> voltage exceeds 8.7 V. In order to maximize converter efficiency, the designer should provide an external bootstrap winding to override the internal V<sub>CC</sub> regulator. If external VCC voltage is greater than 9.3 V, the internal depletion mode MOSFET regulator is disabled and power is derived from the external V<sub>CC</sub> supply. The V<sub>CC</sub> supply provides power to the internal circuity as well as providing supply voltage to the gate drive circuit.

### Soft-Start/Enable

The soft-start time is externally programmable with capacitor connected to the SS/EN pin. A constant current source provides the current to the SS/EN pin to generate a linear start-up time versus the capacitance value. The SS/EN pin clamps the error amplifier output voltage, limiting the rate of increase in duty cycle. By controlling the rate of rise in duty cycle gradually, the output voltage rises gradually preventing the output voltage from overshooting. The SS/EN pin can also be used to enable or disable the output driver section with an external logic signal.

### **Synchronization**

The synchronization to external clock is easily accomplished by connecting the external clock into the SYNC pin (Si9119 only). The logic high to low transition synchronizes the clock. The external clock frequency must be at least 5 % faster than the internal clock frequency.

### Reference Voltage

The reference voltage for the Si9118/Si9119 are set at 4.0 V. The reference voltage is not connected to the non-inverting inputs of the error amplifier, therefore, the minimum output voltage is not limited to reference voltage. The V<sub>RFF</sub> pin requires a 0.1 μF decoupling capacitor.

### **Error Amplifier**

The error amplifier gain-bandwidth product is critical parameter which determines the transient response of converter. The transient response is function of both small and large signal responses. The small signal

response is determined by the feedback compensation network while the large signal response is determined by the inductor di/dt slew rate. Besides the inductance value, the error amplifier gain-bandwidth determine the converter response time. In order to minimize the response time, Si9118/Si9119 is designed with a 2.7 MHz error amplifier gain-bandwidth product to provide the widest converter bandwidth possible.

### **PWM Mode**

The converter operates in PWM mode if the PWM/ PSM pin is connected to V<sub>RFF</sub> pin or logic high. As the load current and line voltage vary, the Si9118/Si9119 maintain constant switching frequency until they reach minimum duty cycle. Once the output voltage regulation is exceeded with minimum duty cycle, the switching frequency will continue to decrease until regulation is achieved. The switching frequency is controlled by the external Rosc and Cosc as shown by the typical oscillator frequency curve. In PWM mode, output ripple noise is constant reducing EMI concerns as well as simplifying the filter to minimize the system noise.

### **Pulse Skipping Mode**

If the  $PWM/\overline{PSM}$  pin is connected to  $-V_{IN}$  pin (logic low), the converter can operate in either PWM or PSM mode depending on the load current. The converter automatically transitions from PWM to PSM or vise versa to maintain output voltage regulation. In PSM mode, the MOSFET switch is turned on until the peak current sensed voltage reaches 100 mV and the output voltage meets or exceeds its regulation voltage. The converter is operating in pulse skipping mode because each pulse delivers excess energy into the output capacitor forcing the output voltage to exceed its regulation voltage. By forcing the output voltage to exceed the regulation voltage, succeeding pulses are skipped until the output voltage drops below the regulation point. Therefore, switching frequency will continue to reduce during PSM control as the demand for output current decreases. The pulse skipping mode cuts down the switching losses, the dominant power consumed during low output current, thereby maintaining high efficiency throughout the entire load range. With PWM/PSM pin in logic low state, the converter transitions back into PWM mode, if the peak current sensed voltage of 100 mV does not generate the required output voltage. In the region between pulse skipping mode and PWM mode, the controller may transition between the two modes, delivering spurts of pulses. This may cause the current waveform to look irregular, but this will not overly affect the ripple voltage. Even in this transitional mode, efficiency remains high.

### **DETAILED OPERATIONAL DESCRIPTION (CONT'D)**

### **Programmable Duty Cycle Control**

The maximum duty cycle limit is controlled by the voltage on  $D_{MAX}$  pin. A  $D_{MAX}$  voltage of 3.2 V 80 % duty cycle while 0.0 V generates 0 % duty cycle. The 80 % duty cycle is maximum default condition at 1 MHz switching frequency. The D<sub>MAX</sub> voltage can be easily generated using resistor divider from the reference voltage. The maximum duty cycle limitation will be different when the converter is synchronized by an external frequency. If the internal free running frequency is much slower than the external SYNC signal (SYNC signal causes the internal clock to reset before the Cosc voltage ramps to 3.2 V), duty cycle is determined by the one shot discharge time of the oscillator capacitor (100 ns). Therefore, with 1 MHz SYNC signal, maximum duty cycle of 90 % can be achieved (100 ns is 10 % of 1 MHz). If the internal free running frequency is very close to the external SYNC frequency (SYNC signal causes the internal clock to reset somewhere between 3.2 V to 4 V), duty cycle is determined by the ratio of Cosc voltage at the SYNC point and the 3.2 V. At this condition, the maximum duty cycle can be greater than 90 %. Therefore, D<sub>MAX</sub> voltage must be modified in order to maintain desired maximum duty cycle.

### Slope Compensation

Slope compensation is necessary for duty cycles greater than 50 % to stabilize the inner current loop and maintain overall loop stability. In order to simplify the slope compensation circuitry, the Si9118 provides the buffered oscillator ramp signal, V<sub>SC</sub> to be used for external slope compensation. V<sub>SC</sub> is only available when DR is high. The V<sub>SC</sub> signal super-imposed with actual current sense signal should be used by the PWM comparator to determine the duty cycle. The summation of this signal should be fed into I<sub>CS</sub> pin. For optimum performance, proper slope compensation is required. The amount of slope compensation is determined by the resistors connected to the I<sub>CS</sub> pin. The amplitude of the V<sub>SC</sub> signal is same as the C<sub>OSC</sub> pin voltage (≈ 4 V). For designs which use with SYNC pin, instead of V<sub>SC</sub> pin, the converter can still operate at duty cycles greater than 50 % by generating an external slope compensation ramp using a

simple RC circuit from the MOSFET driver output pin as shown on the application circuit.

### **Over Current Protection**

Si9118/Si9119 are designed with a pulse-to-pulse peak

current limiting protection circuit to protect itself, and the load in case of a failure. The voltage across the sense resistor is monitored continuously and if the voltage reaches its trigger level, the duty cycle is terminated. This limits the maximum current delivered to the load. In order to improve the accuracy of over current protection from traditional controllers, Si9118/ Si9119 are designed with separate  $I_{LIMIT}$  and  $I_{CS}$  pins. Voltage on the I<sub>LIMIT</sub> pin does not sum in the traditional slope compensation voltage, which adds error into the detection level. I<sub>CS</sub> pin is used to sum the current sense signal and the slope compensation for loop stability.

### **Output Driver Stage**

The DR pin is designed to drive a low-side N-Channel MOSFET. The driver stage is sized to sink and source peak currents up to 500 mA with  $V_{CC}$  = 12 V. This provides ample drive capability for 50 W of output power.

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see www.vishay.com/ppq?70815.

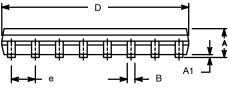

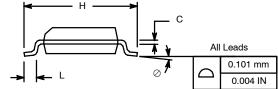

SOIC (NARROW): 16-LEAD (POWER IC ONLY)

JEDEC Part Number: MS-012

|                | MILLIM                       | IETERS | INCHES    |       |  |  |  |

|----------------|------------------------------|--------|-----------|-------|--|--|--|

| Dim            | Min                          | Max    | Min       | Max   |  |  |  |

| Α              | 1.35                         | 1.75   | 0.053     | 0.069 |  |  |  |

| A <sub>1</sub> | 0.10                         | 0.20   | 0.004     | 0.008 |  |  |  |

| В              | 0.38                         | 0.51   | 0.015     | 0.020 |  |  |  |

| С              | 0.18                         | 0.23   | 0.007     | 0.009 |  |  |  |

| D              | 9.80                         | 10.00  | 0.385     | 0.393 |  |  |  |

| E              | 3.80                         | 4.00   | 0.149     | 0.157 |  |  |  |

| е              | 1.27                         | BSC    | 0.050 BSC |       |  |  |  |

| Н              | 5.80                         | 6.20   | 0.228     | 0.244 |  |  |  |

| L              | 0.50                         | 0.93   | 0.020     | 0.037 |  |  |  |

| 0              | 0°                           | 8°     | 0°        | 8°    |  |  |  |

| ECN: S 4       | ECN: 9 40090 Poy A 02 Feb 04 |        |           |       |  |  |  |

ECN: S-40080—Rev. A, 02-Feb-04

DWG: 5912

www.vishay.com 28-Jan-04

# **Legal Disclaimer Notice**

Vishay

## **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.