SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

- Military Operating Temperature Range: - 55°C to 125°C

- Processed to MIL-PRF-38535

- Fast Instruction Cycle Time (30 ns and 40 ns)

- Source-Code Compatible With All C1x and C2x Devices

- RAM-Based Operation

- 9K × 16-Bit Single-Cycle On-Chip **Program/Data RAM**

- 1056 × 16-Bit Dual-Access On-Chip Data RAM

- 2K × 16-Bit On-Chip Boot ROM

- 224K × 16-Bit Maximum Addressable External Memory Space (64K Program, 64K Data, 64K I/O, and 32K Global)

- 32-Bit Arithmetic Logic Unit (ALU)

- 32-bit Accumulator (ACC)

- 32-Bit Accumulator Buffer (ACCB)

- 16-Bit Parallel Logic Unit (PLU)

- 16 × 16-Bit Multiplier, 32-Bit Product

- 11 Context-Switch Registers

- Two Buffers for Circular Addressing

- Full-Duplex Synchronous Serial Port

- Time-Division Multiplexed Serial Port (TDM)

- Timer With Control and Counter Registers

- 16 Software Programmable Wait-State Generators

- Divide-by-One Clock Option

- IEEE 1149.1<sup>†</sup> Boundary Scan Logic

- Operations Are Fully Static

- Enhanced Performance Implanted CMOS (EPIC<sup>™</sup>) Technology Fabricated by Texas Instruments

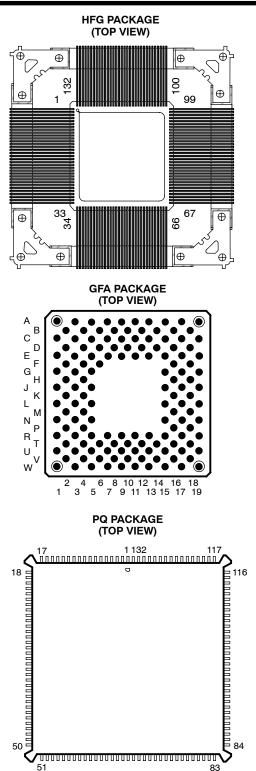

- Packaging

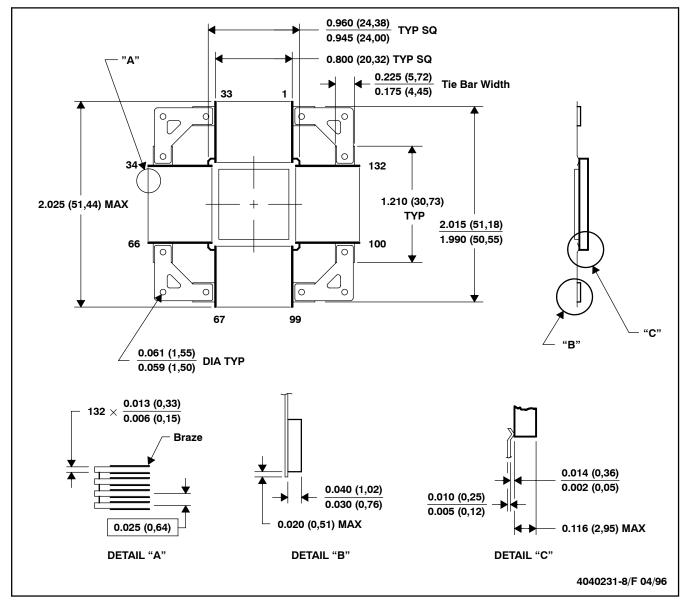

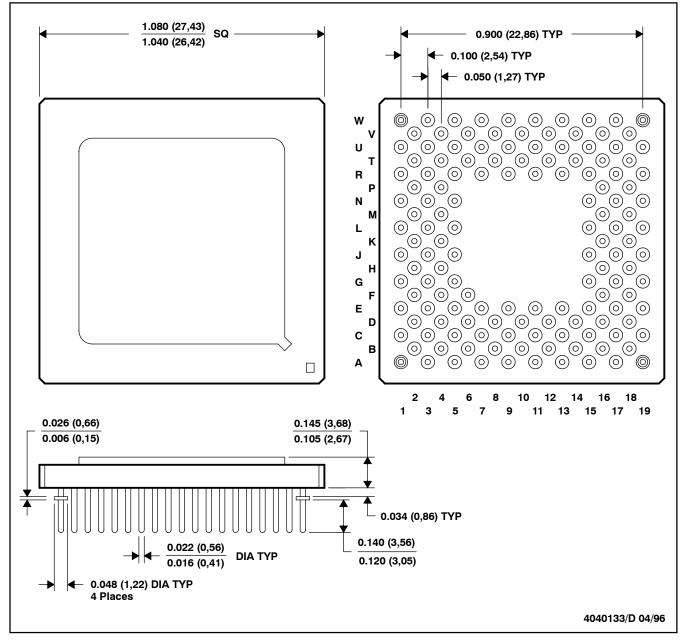

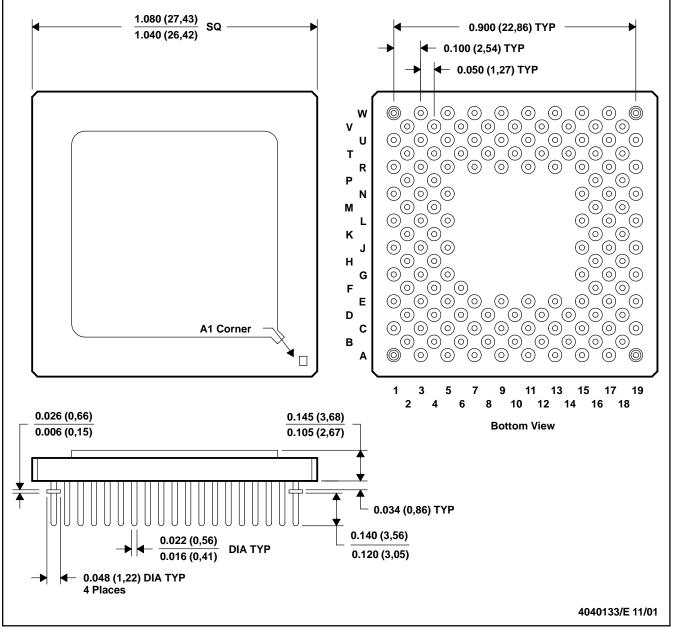

- 141-Pin Ceramic Grid Array (GFA Suffix)

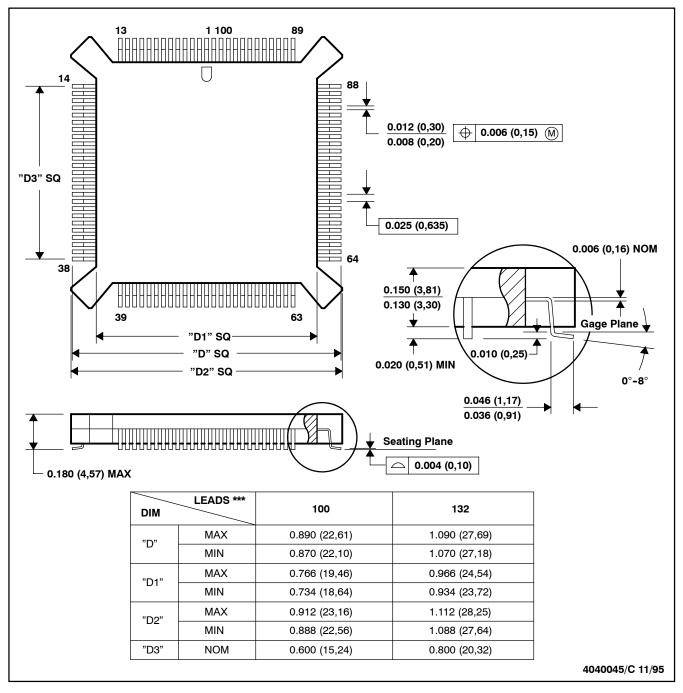

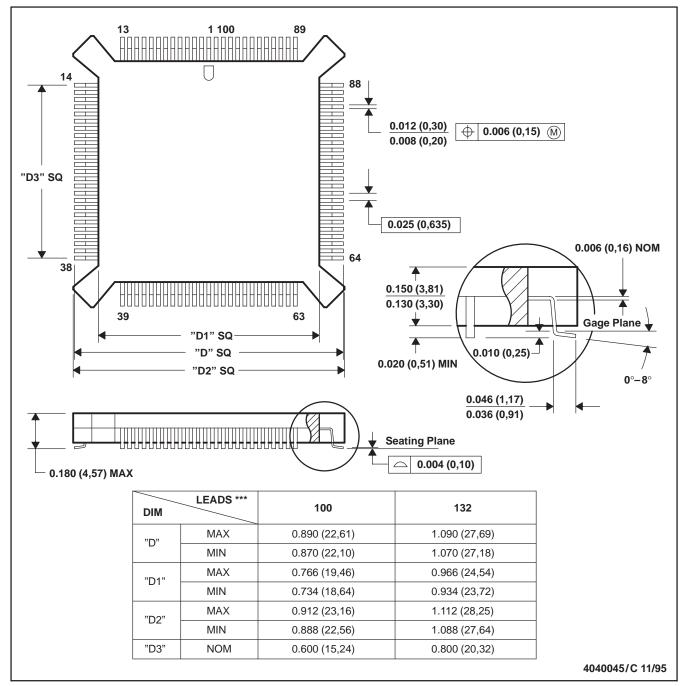

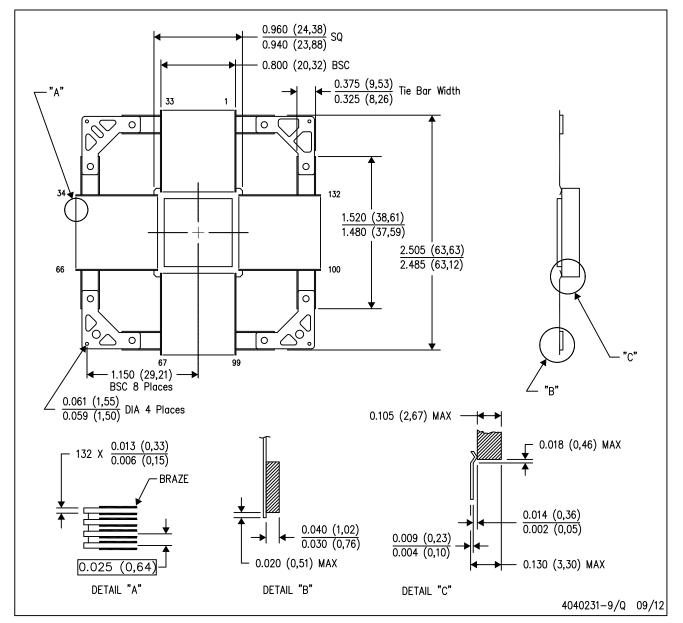

- 132-Lead Ceramic Quad Flat Package (HFG Suffix)

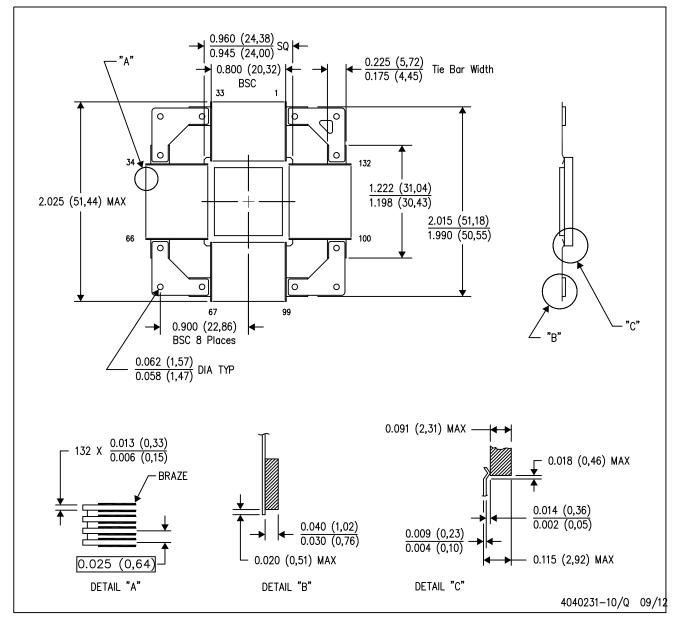

- 132-Lead Plastic Quad Flat Package (PQ Suffix)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

<sup>†</sup> IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture EPIC is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1998, Texas Instruments Incorporated On products compliant to MIL-STD-883, Class B, all parameters are tested unless otherwise noted. On all other products, production processing does not necessarily include testing of all parameters.

SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

#### description

The SMJ320C50 digital signal processor (DSP) is a high-performance, 16-bit, fixed-point processor manufactured in 0.72-µm double-level metal CMOS technology. The SMJ320C50 is the first DSP from TI designed as a fully static device. Full-static CMOS design contributes to low power consumption while maintaining high performance, making it ideal for applications such as battery-operated communications systems, satellite systems, and advanced control algorithms.

A number of enhancements to the basic SMJ320C2x architecture give the C50 a minimum 2× performance over the previous generation. A four-deep instruction pipeline, that incorporates delayed branching, delayed call to subroutine, and delayed return from subroutine, allows the C50 to perform instructions in fewer cycles. The addition of a parallel logic unit (PLU) gives the C50 a method for manipulating bits in data memory without using the accumulator and ALU. The C50 has additional shifting and scaling capability for proper alignment of multiplicands or storage of values to data memory.

The C50 achieves its low-power consumption through the IDLE2 instruction. IDLE2 removes the functional clock from the internal hardware of the C50, which puts it into a total-sleep mode that uses only 7  $\mu$ A. A low-logic level on an external interrupt with a duration of at least five clock cycles ends the IDLE2 mode.

The C50 is available with two clock speeds. The clock frequencies are 50 MHz, providing a 40-ns cycle time, and 66 MHz, providing a 30-ns cycle time. The available options are listed in Table 1.

| PART NUMBER                 | SPEED            | SPEED VOLTAGE PA<br>TOLERANCE |                           |

|-----------------------------|------------------|-------------------------------|---------------------------|

| SMJ320C50GFAM66             | 30-ns cycle time | ±5%                           | Pin grid array            |

| SMJ320C50HFGM66             | 30-ns cycle time | ±5%                           | Quad flat package         |

| SMJ320C50GFAM50             | 40 ns cycle time | ±5%                           | Pin grid array            |

| SMJ320C50HFGM50             | 40 ns cycle time | ±5%                           | Quad flat package         |

| SMQ320C50PQM66 <sup>†</sup> | 30 ns cycle time | ±5%                           | Plastic Quad flat package |

**Table 1. Available Options**

<sup>†</sup> When ordering, use DESC P/N 5962-9455804NZD

SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

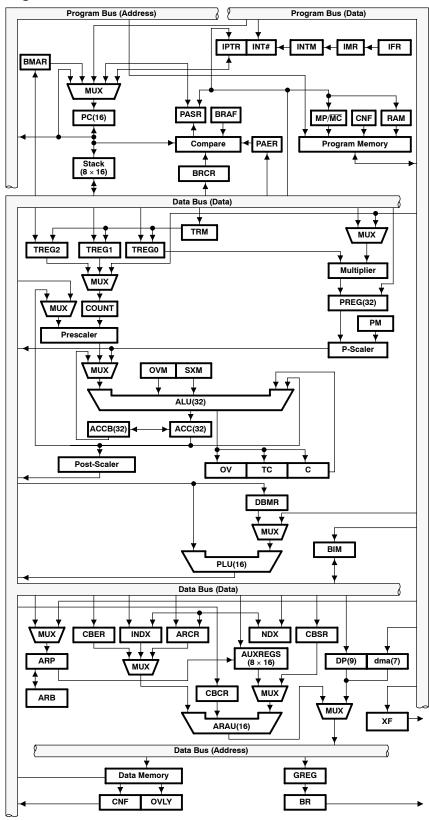

#### functional block diagram

SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

#### terminal assignments

| NAME            | PQ PKG | HFG PKG | GFA PKG | NAME            | PQ PKG | HFG PKG | GFA PKG |

|-----------------|--------|---------|---------|-----------------|--------|---------|---------|

| NC <sup>†</sup> | 18     | 1       |         | A2              | 57     | 40      | W3      |

| NC <sup>†</sup> | 19     | 2       |         | A3              | 58     | 41      | U7      |

| VSS3            | 20     | 3       | D8      | A4              | 59     | 42      | V6      |

| VSS4            | 21     | 4       | D10     | A5              | 60     | 43      | W5      |

| NC <sup>†</sup> | 22     | 5       |         | A6              | 61     | 44      | U9      |

| D7              | 23     | 6       | E3      | A7              | 62     | 45      | V8      |

| D6              | 24     | 7       | D2      | A8              | 63     | 46      | W7      |

| D5              | 25     | 8       | C1      | A9              | 64     | 47      | W9      |

| D4              | 26     | 9       | G3      | VDD7            | 65     | 48      | E9      |

| D3              | 27     | 10      | F2      | VDD8            | 66     | 49      | E11     |

| D2              | 28     | 11      | E1      | TDI             | 67     | 50      | V10     |

| D1              | 29     | 12      | J3      | VSS9            | 68     | 51      | K4      |

| D0(LSB)         | 30     | 13      | H2      | VSS10           | 69     | 52      | M4      |

| TMS             | 31     | 14      | G1      | NC <sup>†</sup> | 70     | 53      |         |

| VDD3            | 32     | 15      | C3      | CLKMD1          | 71     | 54      | W11     |

| VDD4            | 33     | 16      | D4      | A10             | 72     | 55      | W13     |

| TCK             | 34     | 17      | J1      | A11             | 73     | 56      | V12     |

| VSS5            | 35     | 18      | D12     | A12             | 74     | 57      | U11     |

| VSS6            | 36     | 19      | F4      | A13             | 75     | 58      | W15     |

| NC <sup>†</sup> | 37     | 20      |         | A14             | 76     | 59      | V14     |

| INT1            | 38     | 21      | L1      | A15(MSB)        | 77     | 60      | U13     |

| INT2            | 39     | 22      | N1      | NC <sup>†</sup> | 78     | 61      |         |

| INT3            | 40     | 23      | M2      | NC <sup>†</sup> | 79     | 62      |         |

| INT4            | 41     | 24      | L3      | VDD9            | 80     | 63      | E13     |

| NMI             | 42     | 25      | R1      | VDD10           | 81     | 64      | G5      |

| DR              | 43     | 26      | P2      | RD              | 82     | 65      | V16     |

| TDR             | 44     | 27      | N3      | WE              | 83     | 66      | U15     |

| FSR             | 45     | 28      | T2      | NC <sup>†</sup> | 84     | 67      |         |

| CLKR            | 46     | 29      | R3      | NC <sup>†</sup> | 85     | 68      |         |

| VDD5            | 47     | 30      | E5      | VSS11           | 86     | 69      | P4      |

| VDD6            | 48     | 31      | E7      | VSS12           | 87     | 70      | T4      |

| NC <sup>†</sup> | 49     | 32      |         | NC <sup>†</sup> | 88     | 71      |         |

| NC <sup>†</sup> | 50     | 33      |         | DS              | 89     | 72      | R17     |

| NC <sup>†</sup> | 51     | 34      |         | IS              | 90     | 73      | T18     |

| NC <sup>†</sup> | 52     | 35      |         | PS              | 91     | 74      | U19     |

| VSS7            | 53     | 36      | H4      | R/W             | 92     | 75      | N17     |

| VSS8            | 54     | 37      | K2      | STRB            | 93     | 76      | P18     |

| A0              | 55     | 38      | U5      | BR              | 94     | 77      | R19     |

| A1              | 56     | 39      | V4      | CLKIN2          | 95     | 78      | L17     |

<sup>†</sup> NC = No internal connection

GFA Package additional connections:

V<sub>DD</sub>: R11, E15, G15, J15, L15, N15, R13, R15, T16, U17, V18, W17, W19 V<sub>SS</sub>: T14, U1, U3, V2, W1, C17, C19, D14, D16, D18, F16, H16, K16, M16, P16

SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

#### terminal assignments (continued)

| NAME            | PQ PKG | HFG PKG | GFA PKG | NAME            | PQ PKG | HFG PKG | GFA PKG |

|-----------------|--------|---------|---------|-----------------|--------|---------|---------|

| X2/CLKIN        | 96     | 79      | M18     | TCLKX           | 123    | 106     | B16     |

| X1              | 97     | 80      | N19     | CLKX            | 124    | 107     | A17     |

| VDD11           | 98     | 81      | J5      | TFSR/TADD       | 125    | 108     | C13     |

| VDD12           | 99     | 82      | L5      | TCLKR           | 126    | 109     | B14     |

| TDO             | 100    | 83      | L19     | RS              | 127    | 110     | A15     |

| VSS13           | 101    | 84      | T6      | READY           | 128    | 111     | C11     |

| VSS14           | 102    | 85      | T8      | HOLD            | 129    | 112     | B12     |

| CLKMD2          | 103    | 86      | K18     | BIO             | 130    | 113     | A13     |

| FSX             | 104    | 87      | J19     | VDD15           | 131    | 114     | R7      |

| TFSX/TFRM       | 105    | 88      | G19     | VDD16           | 132    | 115     | R9      |

| DX              | 106    | 89      | H18     | IAQ             | 1      | 116     | A11     |

| TDX             | 107    | 90      | J17     | TRST            | 2      | 117     | A9      |

| HOLDA           | 108    | 91      | E19     | VSS1            | 3      | 118     | B10     |

| XF              | 109    | 92      | F18     | VSS2            | 4      | 119     | D6      |

| CLKOUT1         | 110    | 93      | G17     | MP/MC           | 5      | 120     | A7      |

| NC <sup>†</sup> | 111    | 94      |         | D15(MSB)        | 6      | 121     | B8      |

| IACK            | 112    | 95      | E17     | D14             | 7      | 122     | C9      |

| VDD13           | 113    | 96      | N5      | D13             | 8      | 123     | A5      |

| VDD14           | 114    | 97      | R5      | D12             | 9      | 124     | B6      |

| NC <sup>†</sup> | 115    | 98      |         | D11             | 10     | 125     | C7      |

| NC <sup>†</sup> | 116    | 99      |         | D10             | 11     | 126     | A3      |

| NC <sup>†</sup> | 117    | 100     |         | D9              | 12     | 127     | B4      |

| EMU0            | 118    | 101     | B18     | D8              | 13     | 128     | C5      |

| EMU1/OFF        | 119    | 102     | A19     | VDD1            | 14     | 129     | A1      |

| VSS15           | 120    | 103     | T10     | VDD2            | 15     | 130     | B2      |

| VSS16           | 121    | 104     | T12     | NC <sup>†</sup> | 16     | 131     |         |

| TOUT            | 122    | 105     | C15     | NC <sup>†</sup> | 17     | 132     |         |

<sup>†</sup> NC = No internal connection

GFA Package additional connections:

V<sub>DD</sub>: R11, E15, G15, J15, L15, N15, R13, R15, T16, U17, V18, W17, W19

V<sub>SS</sub>: T14, U1, U3, V2, W1, C17, C19, D14, D16, D18, F16, H16, K16, M16, P16

SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

#### **Terminal Functions**

| TERMINAL                                                                                                                   |                          | DECODIDITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                       | <b>TYPE</b> <sup>†</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                            |                          | ADDRESS AND DATA BUSES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A15 (MSB)<br>A14<br>A13<br>A12<br>A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 (LSB)             | I/O/Z                    | Parallel address bus. Multiplexed to address external data, program memory, or I/O. A0-A15 are in the high-impedance state in hold mode and when OFF is active (low). These signals are used as inputs for external DMA access of the on-chip single-access RAM. They become inputs while HOLDA is active (low) if BR is driven low externally.                                                                                                                                                              |

| D15 (MSB)<br>D14<br>D13<br>D12<br>D11<br>D10<br>D9<br>D8<br>D7<br>D6<br>D5<br>D4<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0 (LSB) | I/O/Z                    | Parallel data bus. Multiplexed to transfer data between the core CPU and external data, program memory, or I/O devices. D0-D15 are in the high-impedance state when not outputting data, when RS or HOLD is asserted, or when OFF is active (low). These signals also are used in external DMA access of the on-chip single-access RAM.                                                                                                                                                                      |

|                                                                                                                            |                          | MEMORY CONTROL SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DS<br>PS<br>IS                                                                                                             | O/Z                      | Data, program, and I/O space select signals. Always high unless asserted for communicating to a particular external space. DS, PS, and IS are in the high-impedance state in hold mode or when OFF is active (low).                                                                                                                                                                                                                                                                                          |

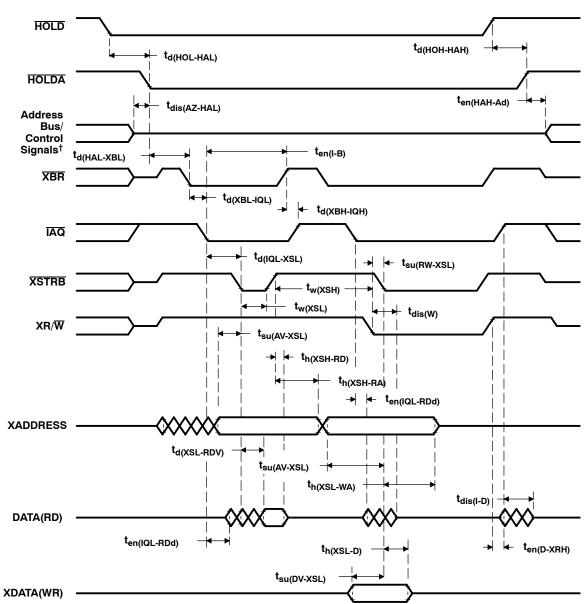

| READY                                                                                                                      | I                        | Data ready input. Indicates that an external device is prepared for the bus transaction to be completed. If the device is not ready (READY is low), the processor waits one cycle and checks READY again. READY also indicates a bus grant to an external device after a BR (bus request) signal.                                                                                                                                                                                                            |

| R/₩                                                                                                                        | I/O/Z                    | Read/write. R/ $\overline{W}$ indicates transfer direction during communication to an external device and is normally in read mode (high) unless asserted for performing a write operation. R/ $\overline{W}$ is in the high-impedance state in hold mode or when $\overline{OFF}$ is active (low). Used in external DMA access of the 9K RAM cell, this signal indicates the direction of the data bus for DMA reads (high) and writes (low) when $\overline{HOLDA}$ and $\overline{IAQ}$ are active (low). |

| STRB                                                                                                                       | I/O/Z                    | Strobe. Always high unless asserted to indicate an external bus cycle, STRB is in the high-impedance state in the hold mode or when OFF is active (low). Used in external DMA access of the on-chip single-access RAM and while HOLDA and IAQ are active (low), STRB is used to select the memory access.                                                                                                                                                                                                    |

| RD                                                                                                                         | O/Z                      | Read select. RD indicates an active external read cycle and can connect directly to the output enable (OE) of external devices. This signal is active on all external program, data, and I/O reads. RD is in the high-impedance state in hold mode or when OFF is active (low).                                                                                                                                                                                                                              |

| I = Input. Q =                                                                                                             | Output Z =               | High-Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

NOTE: All input pins that are unused should be connected to V<sub>DD</sub> or an external pullup resistor. The BR pin has an internal pullup for performing DMA to the on-chip RAM. For emulation, TRST has an internal pulldown, and TMS, TCK, and TDI have internal pullups. EMU0 and EMU1 require external pullups to support emulation.

SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

## **Terminal Functions (Continued)**

| TERMI                        | NAL                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME                         | TYPE <sup>†</sup>                                                                                                                                                                                                                                                                                                                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                              |                                                                                                                                                                                                                                                                                                                                                           | MEMORY CONTROL SIGNALS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| WE                           | O/Z                                                                                                                                                                                                                                                                                                                                                       | Write enable. The falling edge indicates that the device is driving the external data bus (D15-D0). Data can be latched by an external device on the rising edge of WE. This signal is active on all external program, data, and I/O writes. WE is in the high-impedance state in hold mode or when $\overline{OFF}$ is active (low).                                                                                                                                                         |  |  |  |  |  |

|                              |                                                                                                                                                                                                                                                                                                                                                           | MULTIPROCESSING SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| HOLD                         | Ι                                                                                                                                                                                                                                                                                                                                                         | Hold. HOLD is asserted to request control of the address, data, and control lines. When acknowledged by the C50, these lines go to the high-impedance state.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| HOLDA                        | O/Z                                                                                                                                                                                                                                                                                                                                                       | Hold acknowledge. HOLDA indicates to the external circuitry that the processor is in a hold state and that the address, data, and memory control lines are in the high-impedance state so that they are available to the external circuitry for access to local memory. This signal also goes to the high-impedance state when OFF is active (low).                                                                                                                                           |  |  |  |  |  |

| BR                           | I/O/Z                                                                                                                                                                                                                                                                                                                                                     | Bus request. BR is asserted during access of external global data memory space. READY is asserted when the global data memory is available for the bus transaction. BR can be used to extend the data memory address space by up to 32K words. BR goes to the high-impedance state when OFF is active low. BR is used in external DMA access of the on-chip single-access RAM. While HOLDA is active (low), BR is externally driven (low) to request access to the on-chip single-access RAM. |  |  |  |  |  |

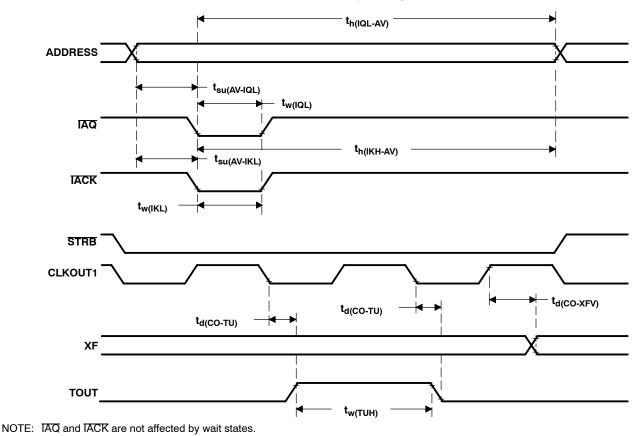

| IAQ                          | AQ O/Z Instruction acquisition. Asserted (active) when there is an instruction address on the address b high-impedance state when OFF is active (low). IAQ is also used in external DMA access single-access RAM. While HOLDA is active (low), IAQ acknowledges the BR request for access single-access RAM and stops indicating instruction acquisition. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| BIO                          | Branch control. BIO samples as the BIO condition and, if it is low, causes the device to execute the instruction. BIO must be active during the fetch of the conditional instruction.                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| XF                           | O/Z                                                                                                                                                                                                                                                                                                                                                       | External flag (latched software-programmable signal). Set high or low by a specific instruction or by loading status register 1 (ST1). Used for signaling other processors in multiprocessor configurations or as a general-purpose output. XF goes to the high-impedance state when OFF is active (low) and is set high at reset.                                                                                                                                                            |  |  |  |  |  |

| IACK                         | O/Z                                                                                                                                                                                                                                                                                                                                                       | Interrupt acknowledge. Indicates receipt of an interrupt and that the program counter is fetching the interrupt vector location designated by A15-A0. IACK goes to the high-impedance state when OFF is active (low).                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                              |                                                                                                                                                                                                                                                                                                                                                           | INITIALIZATION, INTERRUPT, AND RESET OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| INT4<br>INT3<br>INT2<br>INT1 | I                                                                                                                                                                                                                                                                                                                                                         | External interrupts. INT1-INT4 are prioritized and maskable by the interrupt mask register (IMR) and interrupt mode bit (INTM, bit 9 of status register 0). These signals can be polled and reset by using the interrupt flag register.                                                                                                                                                                                                                                                       |  |  |  |  |  |

| NMI                          | I                                                                                                                                                                                                                                                                                                                                                         | Nonmaskable interrupt. <u>NMI</u> is the external interrupt that cannot be masked via INTM or IMR. When <u>NMI</u> is activated, the processor traps to the appropriate vector location.                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| RS                           | I                                                                                                                                                                                                                                                                                                                                                         | Reset. RS causes the device to terminate execution and forces the program counter to zero. When RS is brought to a high level, execution begins at location zero of program memory.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| MP/MC                        | I                                                                                                                                                                                                                                                                                                                                                         | Microprocessor/microcomputer select. If active (low) at reset (microcomputer mode), the signal causes the internal program ROM to be mapped into program memory space. In the microprocessor mode, all program memory is mapped externally. This signal is sampled only during reset, and the mode that is set at reset can be overridden via the software control bit MP/MC in the PMST register.                                                                                            |  |  |  |  |  |

|                              |                                                                                                                                                                                                                                                                                                                                                           | OSCILLATOR/TIMER SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| CLKOUT1                      | O/Z                                                                                                                                                                                                                                                                                                                                                       | Master clock (or CLKIN2 frequency). CLKOUT1 cycles at the machine-cycle rate of the CPU. The internal machine cycle is bounded by the rising edges of this signal. This signal goes to the high-impedance state when OFF is active (low).                                                                                                                                                                                                                                                     |  |  |  |  |  |

<sup>†</sup> I = Input, O = Output, Z = High-Impedance

SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

## **Terminal Functions (Continued)**

| <b>TYPE</b> <sup>†</sup> | DESCHIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                          | OSCILLATOR/TIMER SIGNALS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| I                        | CLKMD1   CLKMD2   Clock mode     0   0   External clock with divide-by-two option. Input clock is provided to X2/CLKIN1. Internal oscillator and PLL are disabled.     0   1   Reserved for test purposes     1   0   External divide-by-one option. Input clock is provided to CLKIN2. Internal oscillator is disabled and internal PLL is enabled.     1   1   Internal or external divide-by-two option. Input clock is provided to X2/CLKIN1. Internal oscillator is enabled and internal PLL is disabled. |  |  |  |  |

| I                        | put to the internal oscillator from the crystal. If the internal oscillator is not being used, a clock can be input to the evice on X2/CLKIN. The internal machine cycle is half this clock rate.                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 0                        | utput from the internal oscillator for the crystal. If the internal oscillator is not used, X1 must be left unconnected.<br>his signal does not go to the high-impedance state when OFF is active (low).                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Ι                        | ivide-by-one input clock for driving the internal machine rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 0                        | imer output. TOUT signals a pulse when the on-chip timer counts down past zero. The pulse is a CLKOUT1 cycle ide.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                          | SUPPLY PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Ι                        | ower supply for data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| I                        | ower supply for address bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Ι                        | ower supply for inputs and internal logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Ι                        | ower supply for address bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Ι                        | ower supply for memory control signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Ι                        | ower supply for inputs and internal logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| I                        | ower supply for memory control signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| I                        | round for memory control signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Ι                        | round for data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| I                        | round for address bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Ι                        | round for memory control signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Ι                        | round for inputs and internal logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                          | I In   I D   I D   I D   I D   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I P   I G   I G                                                                                                                                                                                                                                                                                                     |  |  |  |  |

<sup>†</sup> I = Input, O = Output, Z = High-Impedance

SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

## **Terminal Functions (Continued)**

| TERMINAL              |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                  | <b>TYPE</b> <sup>†</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       |                          | SERIAL PORT SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

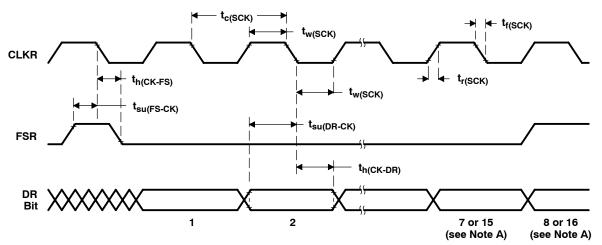

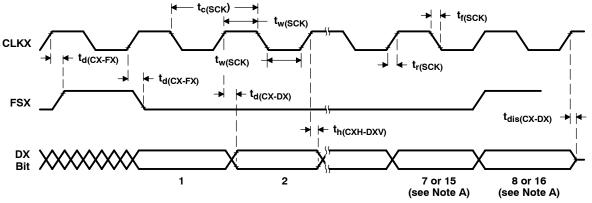

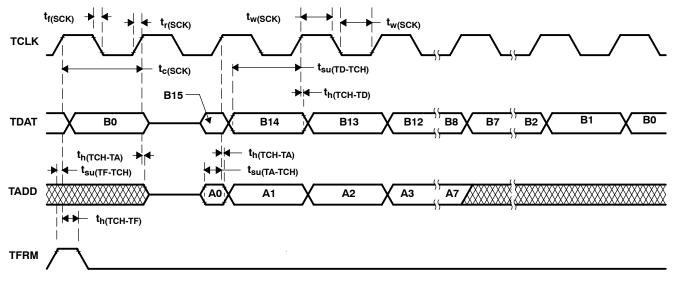

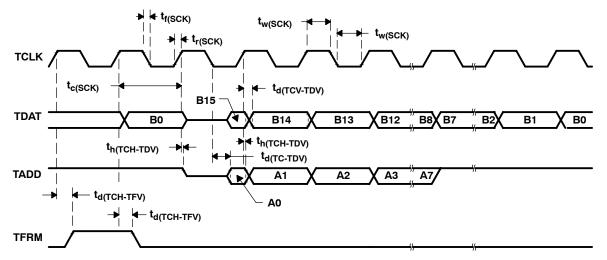

| CLKR<br>TCLKR         | I                        | Receive clock. External clock signal for clocking data from DR (data receive) or TDR (TDM data receive) into the RSR (serial port receive shift register). Must be present during serial port transfers. If the serial port is not being used, these signals can be sampled as an input via the IN0 bit of the serial port control (SPC) or TDR serial port control (TSPC) registers.                                                                                                                                  |

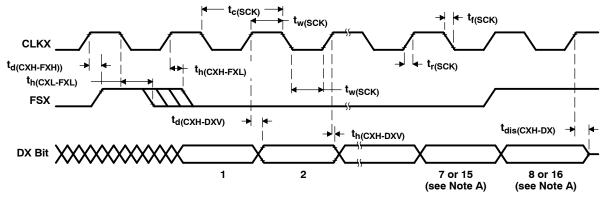

| CLKX<br>TCLKX         | I/O/Z                    | Transmit clock. Clock signal for clocking data from the DR or TDR to the DX (data transmit) or TDX (TDM data transmit pins). CLKX can be an input if the MCM bit in the serial port control register is set to 0. It can also be driven by the device at 1/4 the CLKOUT1 frequency when the MCM bit is set to 1. If the serial port is not being used, this pin can be sampled as an input via the IN1 bit of the SPC or TSPC register. This signal goes into the high-impedance state when OFF is active (low).       |

| DR<br>TDR             | I                        | Serial data receive. Serial data is received in the RSR (serial port receive shift register) via DR or TDR.                                                                                                                                                                                                                                                                                                                                                                                                            |

| DX<br>TDX             | O/Z                      | Serial port transmit. Serial data transmitted from XSR (serial port transmit shift register) via DX or TDX. This signal is in the high-impedance state when not transmitting and when OFF is active (low).                                                                                                                                                                                                                                                                                                             |

| FSR<br>TFSR/TADD      | I<br>I/O/Z               | Frame synchronization pulse for receive. The falling edge of FSR or TFSR initiates the data receive process, which begins the clocking of the RSR. TFSR becomes an input/output (TADD) pin when the serial port is operating in the TDM mode (TDM bit = 1). In TDM mode, this pin is used to input/output the address of the port. This signal goes into the high-impedance state when OFF is active (low).                                                                                                            |

| FSX<br>TFSX/TFRM      | I/O/Z                    | Frame synchronization pulse for transmit. The falling edge of FSX/TFSX initiates the data transmit process, which begins the clocking of the XSR. Following reset, the default operating condition of FSX/TFSX is an input. This pin may be selected by software to be an output when the TXM bit in the serial control register is set to 1. This signal goes to the high-impedance state when OFF is active (low). When operating in TDM mode (TDM bit = 1), TFSX becomes TFRM, the TDM frame-synchronization pulse. |

|                       |                          | TEST SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ТСК                   | I                        | Boundary scan test clock. This is normally a free-running clock with a 50% duty cycle. The changes of TAP (test access port) input signals (TMS and TDI) are clocked into the TAP controller, instruction register, or selected test data register on the rising edge of TCK. Changes at the TAP output signal (TDO) occur on the falling edge of TCK.                                                                                                                                                                 |

| TDI                   | I                        | Boundary scan test data input. TDI is clocked into the selected register (instruction or data) on a rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                |

| TDO                   | O/Z                      | Boundary scan test data output. The contents of the selected register (instruction or data) is shifted out of TDO on the falling edge of TCK. TDO is in the high-impedance state except when scanning of data is in progress. This signal also goes to the high-impedance state when OFF is active (low).                                                                                                                                                                                                              |

| TMS                   | I                        | Boundary scan test mode select. This serial control input is clocked into the test access port (TAP) controller on the rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                             |

| TRST                  | I                        | Boundary scan test reset. Asserting this signal gives the JTAG scan system control of the operations of the device. If this signal is not connected or is driven low, the device operates in its functional mode and the boundary scan signals are ignored.                                                                                                                                                                                                                                                            |

| EMU0                  | I/O/Z                    | Emulator 0. When TRST is driven low, EMU0 must be high for activation of the OFF condition (see EMU1/OFF). When TRST is driven high, EMU0 is used as an interrupt to or from the emulator system and is defined as input/output put via boundary scan.                                                                                                                                                                                                                                                                 |

| EMU1/OFF              | I/O/Z                    | Emulator 1/OFF. When TRST is driven high, EMU1/OFF is used as an interrupt to or from the emulator system and is defined as input/output via boundary scan. When TRST is driven low, EMU1/OFF is configured as OFF. When the OFF signal is active (low), all output drivers are in the high-impedance state. OFF is used exclusively for testing and emulation purposes (not for multiprocessing applications). For the OFF condition, the following conditions apply:<br>• TRST = Low<br>• EMU0 = High                |

| '                     |                          | • EMU1/OFF = Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RESERVED <sup>‡</sup> | N/C                      | Reserved. This pin must be left unconnected.<br>High-Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

<sup>†</sup> I = Input, O = Output, Z = High-Impedance <sup>‡</sup> Quad flat pack only

SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

| absolute maximum ra | tinas over or | perating case | temperature range | (unless otherwise noted) <sup>†</sup> |

|---------------------|---------------|---------------|-------------------|---------------------------------------|

|                     |               | oorading oado | tomporatare range | (uniced caller meeting)               |

| Supply voltage range, V <sub>DD</sub> (see Note 1) | - 0.3 V to 7 V |

|----------------------------------------------------|----------------|

| Input voltage range                                | - 0.3 V to 7 V |

| Output voltage range                               | - 0.3 V to 7 V |

| Operating case temperature range, T <sub>C</sub>   | 55°C to 125°C  |

| Storage temperature range, T <sub>stg</sub>        | 65°C to 150°C  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to V<sub>SS</sub>.

#### recommended operating conditions

|                 |                                |                          | MIN   | NOM | MAX                   | UNIT |

|-----------------|--------------------------------|--------------------------|-------|-----|-----------------------|------|

| $V_{DD}$        | / <sub>DD</sub> Supply voltage |                          |       |     | 5.25                  | V    |

| $V_{\text{SS}}$ | Supply voltage                 |                          |       | 0   |                       | V    |

|                 |                                | CLKIN, CLKIN2            | 3.0   |     | V <sub>DD + 0.3</sub> | V    |

| $V_{iH}$        | High-level input voltage       | CLKX, CLKR, TCLKX, TCLKR | 2.5   |     | V <sub>DD + 0.3</sub> | V    |

|                 |                                | All others               | 2.2   |     | V <sub>DD + 0.3</sub> | V    |

| $V_{\text{IL}}$ | Low-level input voltage        |                          | - 0.3 |     | 0.6                   | V    |

| I <sub>OH</sub> | High-level output current      |                          |       |     | - 300 <sup>‡</sup>    | μA   |

| I <sub>OL</sub> | DL Low-level output current    |                          |       |     | 2                     | mA   |

| Т <sub>С</sub>  |                                |                          |       |     | 125                   | °C   |

<sup>‡</sup> This I<sub>OH</sub> can be exceeded when using a 1-KΩ pulldown resistor on the TDM serial port TADD output; however, this output still meets V<sub>OH</sub> specifications under these conditions.

NOTE 2: T<sub>C</sub> MAX at maximum rated operating conditions at any point on case. T<sub>C</sub> MIN at initial (time zero) power up.

## electrical characteristics over recommended ranges of supply voltage and operating case temperature (unless otherwise noted)

|                  | PARAMETER                              |                                       | TEST COND               | ITIONS§                   |                         | MIN   | TYP <sup>¶</sup> | MAX | UNIT |

|------------------|----------------------------------------|---------------------------------------|-------------------------|---------------------------|-------------------------|-------|------------------|-----|------|

| V <sub>OH</sub>  | High-level output voltage <sup>#</sup> | I <sub>OH</sub> = MAX                 |                         |                           |                         | 2.4   | 3                |     | V    |

| V <sub>OL</sub>  | Low-level output voltage <sup>¶</sup>  | I <sub>OL</sub> = MAX                 |                         |                           |                         |       | 0.3              | 0.6 | V    |

|                  | High-impedance output                  | BR (with internal p                   | oullup)                 |                           |                         | - 500 |                  | 30  | •    |

| I <sub>OZ</sub>  | current (V <sub>DD</sub> = MAX)        | All others                            |                         |                           |                         | - 30  |                  | 30  | μA   |

|                  |                                        | TRST (with interna                    | al pulldown)            |                           |                         | - 30  | II               | 800 |      |

|                  | Input current                          | TMS, TCK, TDI (with internal pullups) |                         |                           | - 500                   | II    | 30               | μA  |      |

| II.              | $(V_I = V_{SS} \text{ to } V_{DD})$    | X2/CLKIN                              |                         |                           |                         | - 50  | II               | 50  |      |

|                  |                                        | All other inputs                      |                         |                           |                         | - 30  | II               | 30  | μA   |

| IDDC             | Supply current, core CPU               | Operating,                            | T <sub>A</sub> = 25°C,  | V <sub>DD</sub> = 5.25 V, | f <sub>x</sub> = 50 MHz |       | 60               | 225 | mA   |

| I <sub>DDP</sub> | Supply current, pins                   | Operating,                            | T <sub>A</sub> = 25°C,  | V <sub>DD</sub> = 5.25 V, | f <sub>x</sub> = 50 MHz |       | 40               | 225 | mA   |

|                  |                                        | IDLE instruction,                     | T <sub>C</sub> = 125°C, | V <sub>DD</sub> = 5.25 V, | f <sub>x</sub> = 50 MHz |       |                  | 30  | mA   |

| IDD              | Supply current, standby                | IDLE2 instruction,                    | Clocks shut off,        | T <sub>C</sub> =125°C,    | V <sub>DD</sub> =5.25 V |       |                  | 7   | μA   |

| Ci               | Input capacitance                      |                                       |                         |                           |                         |       | 15               | 40  | pF   |

| Co               | Output capacitance                     |                                       |                         |                           |                         |       | 15               | 40  | pF   |

§ For conditions shown as MIN/MAX, use the appropriate value specified under recommended operating conditions.

<sup>¶</sup> All typical or nominal values are at  $V_{DD}$  = 5 V,  $T_A$  (ambient air temperature)= 25°C.

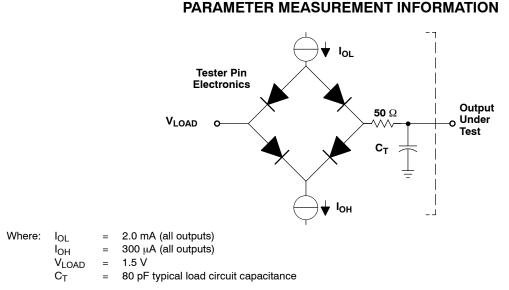

<sup>#</sup> All input and output voltage levels are TTL-compatible. Figure 1 shows the test load circuit; Figure 2 and Figure 3 show the voltage reference levels.

|| These values are not specified pending detailed characterization.

SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

#### Figure 1. Test Load Circuit

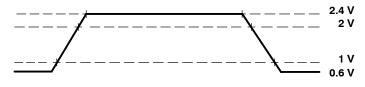

#### signal transition levels

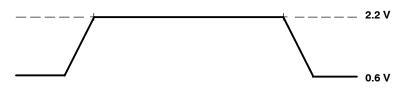

Transistor-to-transistor logic (TTL) output levels are driven to a minimum logic-high level of 2.4 V and to a maximum logic-low level of 0.6 V. Figure 2 shows the TTL-level outputs.

Figure 2. TTL-Level Outputs

TTL-output transition times are specified as follows:

- For a *high-to-low transition*, the level at which the output is said to be no longer high is 2 V, and the level at which the output is said to be low is 1 V.

- For a *low-to-high transition*, the level at which the output is said to be no longer low is 1 V, and the level at which the output is said to be high is 2 V.

Figure 3 shows the TTL-level inputs.

Figure 3. TTL-Level Inputs

TTL-compatible input transition times are specified as follows:

- For a *high-to-low transition* on an input signal, the level at which the input is said to be no longer high is 2 V, and the level at which the input is said to be low is 0.8 V.

- For a low to high transisiton on an input signal, the level at which the input is said to be no longer low is 0.8 V, and the level at which the input is said to be high is 2 V.

SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

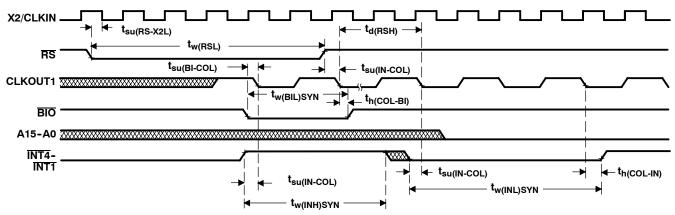

#### **CLOCK CHARACTERISTICS AND TIMING**

The C50 can use either its internal oscillator or an external frequency source for a clock. The clock mode is determined by the CLKMD1 and CLKMD2 pins. Table 2 outlines the selection of the clock mode by these pins.

| CLKMD1 | CLKMD2 | CLOCK SOURCE                                                                                  |  |  |  |

|--------|--------|-----------------------------------------------------------------------------------------------|--|--|--|

| 1      | 0      | External divide-by-one clock option                                                           |  |  |  |

| 0      | 1      | Reserved for test purposes                                                                    |  |  |  |

| 1      | 1      | External divide-by-two option or internal divide-by-two clock option with an external crystal |  |  |  |

| 0      | 0      | External divide-by-two option with the internal oscillator disabled                           |  |  |  |

#### Table 2. Clock Mode Selection

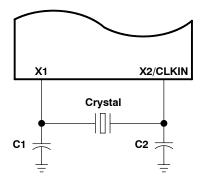

#### internal divide-by-two clock option with external crystal

The internal oscillator is enabled by connecting a crystal across X1 and X2/CLKIN. The frequency of CLKOUT1 is one-half the crystal's oscillating frequency. The crystal should be in either fundamental or overtone operation and parallel resonant, with an effective series resistance of  $30 \Omega$  and a power dissipation of 1 mW; it should be specified at a load capacitance of 20 pF. Overtone crystals require an additional tuned LC circuit. Figure 4 shows an external crystal (fundamental frequency) connected to the on-chip oscillator.

#### recommended operating conditions for internal divide-by-two clock option

|                |                       | '3  | 20C50-5 | 0   | '3: | '320C50-66 |     |      |

|----------------|-----------------------|-----|---------|-----|-----|------------|-----|------|

|                |                       | MIN | NOM     | MAX | MIN | NOM        | MAX | UNIT |

| f <sub>x</sub> | Input clock frequency | 0†  |         | 50  | 0†  |            | 66  | MHz  |

| C1, C2         | Load capacitance      |     | 10      |     |     | 10         |     | pF   |

<sup>+</sup> This device uses a fully static design and, therefore, can operate with t<sub>c(CI)</sub> approaching ∞. The device is characterized at frequencies approaching 0 Hz but is tested at a minimum of 3.3 MHz to meet device test time requirements.

Figure 4. Internal Clock Option

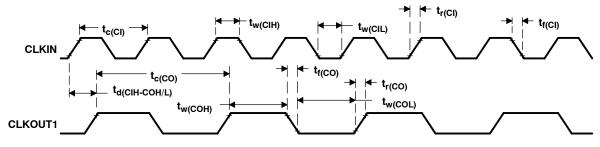

#### external divide-by-two clock option

An external frequency source can be used by injecting the frequency directly into X2/CLKIN with X1 left unconnected, CLKMD1 set high, and CLKMD2 set high. The external frequency is divided by two to generate the internal machine cycle. The external frequency injected must conform to specifications listed in the timing requirements table.

switching characteristics over recommended operating conditions [H = 0.5 t<sub>c(CO)</sub>]

|                           | PARAMETER                                     |       | 320C50-5            | 0     | '3    | 20C50-66            | 6     |      |

|---------------------------|-----------------------------------------------|-------|---------------------|-------|-------|---------------------|-------|------|

|                           |                                               |       | TYP                 | MAX   | MIN   | TYP                 | MAX   | UNIT |

| t <sub>c(CO)</sub>        | Cycle time, CLKOUT1                           | 40    | 2t <sub>c(CI)</sub> | †     | 30    | 2t <sub>c(CI)</sub> | †     | ns   |

| t <sub>d(CIH-COH/L)</sub> | Delay time, X2/CLKIN high to CLKOUT1 high/low | 3     | 11                  | 20    | 3     | 11                  | 20    | ns   |

| t <sub>f(CO)</sub>        | Fall time, CLKOUT1                            |       | 5                   |       |       | 5                   |       | ns   |

| t <sub>r(CO)</sub>        | Rise time, CLKOUT1                            |       | 5                   |       |       | 5                   |       | ns   |

| t <sub>w(COL)</sub>       | Pulse duration, CLKOUT1 low                   | H - 3 | Н                   | H + 2 | H - 3 | Н                   | H + 2 | ns   |

| t <sub>w(COH)</sub>       | Pulse duration, CLKOUT1 high                  | H - 3 | Н                   | H + 2 | H - 3 | Н                   | H + 2 | ns   |

<sup>†</sup> This device uses a fully static design and, therefore, can operate with t<sub>c(CI)</sub> approaching ∞. The device is characterized at frequencies approaching 0 Hz, but is tested at a minimum of 6.7 MHz to meet device test time requirements.

#### timing requirements

|                     |                               | '320C50-50 |     | '320C50-66 |     |      |

|---------------------|-------------------------------|------------|-----|------------|-----|------|

|                     |                               | MIN        | MAX | MIN        | MAX | UNIT |

| t <sub>c(CI)</sub>  | Cycle time, X2/CLKIN          | 20         | †   | 15         | †   | ns   |

| t <sub>f(CI)</sub>  | Fall time, X2/CLKIN           |            | 5*  |            | 5*  | ns   |

| t <sub>r(CI)</sub>  | Rise time, X2/CLKIN           |            | 5*  |            | 5*  | ns   |

| t <sub>w(CIL)</sub> | Pulse duration, X2/CLKIN low  | 8          | †   | 7          | †   | ns   |

| t <sub>w(CIH)</sub> | Pulse duration, X2/CLKIN high | 8          | †   | 7          | †   | ns   |

<sup>+</sup> This device uses a fully static design and, therefore, can operate with t<sub>c(CI)</sub> approaching ∞. The device is characterized at frequencies approaching 0 Hz, but is tested at a minimum of 6.7 MHz to meet device test time requirements.

\* This parameter is not production tested.

Figure 5. External Divide-by-Two Clock Timing

SGUS020B - JUNE 1996 - REVISED SEPTEMBER 2001

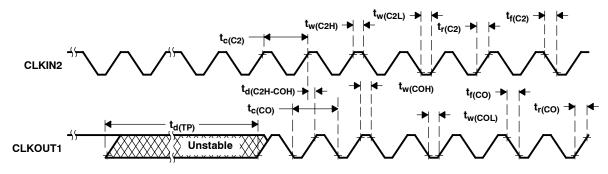

#### external divide-by-one clock option

An external frequency source can be used by injecting the frequency directly into CLKIN2 with X1 left unconnected and X2 connected to  $V_{DD}$ . This external frequency is divided by one to generate the internal machine cycle. The divide-by-one option is used when CLKMD1 is strapped high and CLKMD2 is strapped low. The external frequency injected must conform to specifications listed in the timing requirements table (see Figure 6 for more details).

#### switching characteristics over recommended operating conditions [H = 0.5 t<sub>c(CO)</sub>]

|                         |                                                                        |        | '320C50-           | 50                      |        | '320C50-           | 66                      |      |

|-------------------------|------------------------------------------------------------------------|--------|--------------------|-------------------------|--------|--------------------|-------------------------|------|

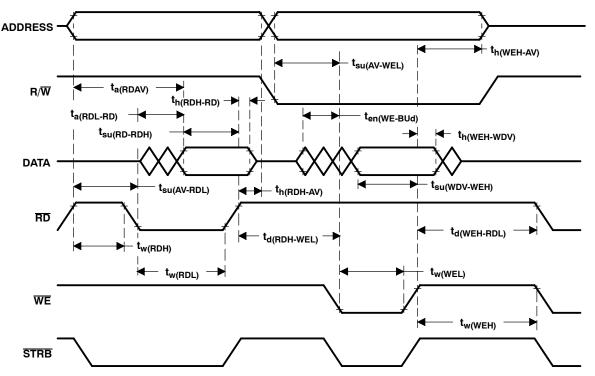

| PARAMETER               |                                                                        | MIN    | TYP                | MAX                     | MIN    | TYP                | MAX                     | UNIT |