# Ultra Low Power Boost Charger with Battery Management and Autonomous Power Multiplexor for Primary Battery in Energy Harvester Applications

Check for Samples: bq25505

#### **FEATURES**

- Ultra Low Power With High Efficiency DC/DC Boost Charger

- Cold-Start Voltage: V<sub>IN</sub> ≥ 330 mV

- Continuous Energy Harvesting From Input Sources as low as 120 mV

- Ultra Low Quiescent Current of 325 nA

- Input Voltage Regulation Prevents

Collapsing High Impedance Input Sources

- Ship Mode with < 5 nA From Battery</li>

- Energy Storage

- Energy can be Stored to Re-Chargeable Liion Batteries, Thin-film Batteries, Super-Capacitors, or Conventional Capacitors

- Battery Charging and Protection

- Internally Set Undervoltage Level

- User Programmable Overvoltage Level

- Battery Good Output Flag

- Programmable Threshold and Hysteresis

- Warn Attached Microcontrollers of Pending Loss of Power

- Can be Used to Enable/Disable System

Loads

- Programmable Maximum Power Point Tracking (MPPT)

- Integrated MPPT for optimal energy extraction from a variety of energy harvesters

- Gate Drivers for Primary (Non-rechargeable) and Secondary (rechargeable) Storage Element Multiplexing

- Autonomous switching based on VBAT\_OK

- Break-before-make prevents system rail droop

#### **APPLICATIONS**

- Energy Harvesting

- Solar Charger

- Thermal Electric Generator (TEG) Harvesting

- Wireless Sensor Networks (WSN)

- Industrial Monitoring

- Environmental Monitoring

- Bridge and Structural Health Monitoring (SHM)

- Smart Building Controls

- Portable and Wearable Health Devices

- Entertainment System Remote Controls

# **DESCRIPTION**

The bq25505 is the first of a new family of intelligent integrated energy harvesting Nano-Power management solutions that are well suited for meeting the special needs of ultra low power applications. The product is specifically designed to efficiently acquire and manage the microwatts ( $\mu$ W) to miliwatts (mW) of power generated from a variety of DC sources like photovoltaic (solar) or thermal electric generators (TEGs). The bq25505 is a highly efficient boost charger targeted toward products and systems, such as wireless sensor networks (WSN) which have stringent power and operational demands. The design of the bq25505 starts with a DCDC boost charger that requires only microwatts of power to begin operating.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **DESCRIPTION (CONTINUED)**

Once started, the boost charger can effectively extract power from low voltage output harvesters such as TEGs or single or dual cell solar panels. The boost charger can be started with VIN as low as 330 mV, and once started, can continue to harvest energy down to  $V_{IN} = 120$  mV.

The bq25505 implements a programmable maximum power point tracking (MPPT) sampling network to optimize the transfer of power into the device. Sampling of the VIN\_DC open circuit voltage is programmed using external resistors, and that sample voltage is held with an external capacitor. For example solar cells that operate at maximum power point (MPP) of 80% of their open circuit voltage, the resistor divider can be set to 80% of the VIN\_DC voltage and the network will control the VIN\_DC to operate near that sampled reference voltage. Alternatively, an external reference voltage can be provide by a MCU to produce a more complex MPPT algorithm.

The bq25505 was designed with the flexibility to support a variety of energy storage elements. The availability of the sources from which harvesters extract their energy can often be sporadic or time-varying. Systems will typically need some type of energy storage element, such as a re-chargeable battery, super capacitor, or conventional capacitor. The storage element will make certain constant power is available when needed for the systems. The storage element also allows the system to handle any peak currents that can not directly come from the input source. To prevent damage to the storage element, both maximum and minimum voltages are monitored against the internally programmed undervoltage (UV) and user programmable overvoltage (OV) levels.

To further assist users in the strict management of their energy budgets, the bq25505 toggles the battery good flag to signal an attached microprocessor when the voltage on an energy storage battery or capacitor has dropped below a pre-set critical level. This should trigger the shedding of load currents to prevent the system from entering an undervoltage condition. The OV and battery good thresholds are programmed independently.

In addition to the boost charging front end, bq25505 provides the system with an autonomous power multiplexor gate drive. The gate drivers allow two storage elements to be multiplexed autonomously in order to provide a single power rail to the system load. This multiplexor is based off the VBAT\_OK threshold which is resistor programmable by the user. This allows the user to set the level when the system is powered by the energy harvester storage element, e.g. rechargable battery or super capacitor or a primary non-rechargeable battery (e.g. two AA batteries). This type of hybrid system architecture allows for the run-time of a typical battery powered systems to be extended based on the amount of energy available from the harvester. If there is not sufficient energy to run the system due to extended "dark time", the primary battery is autonomously switched to the main system rail within 8 µsec in order to provide uninterrupted operation.

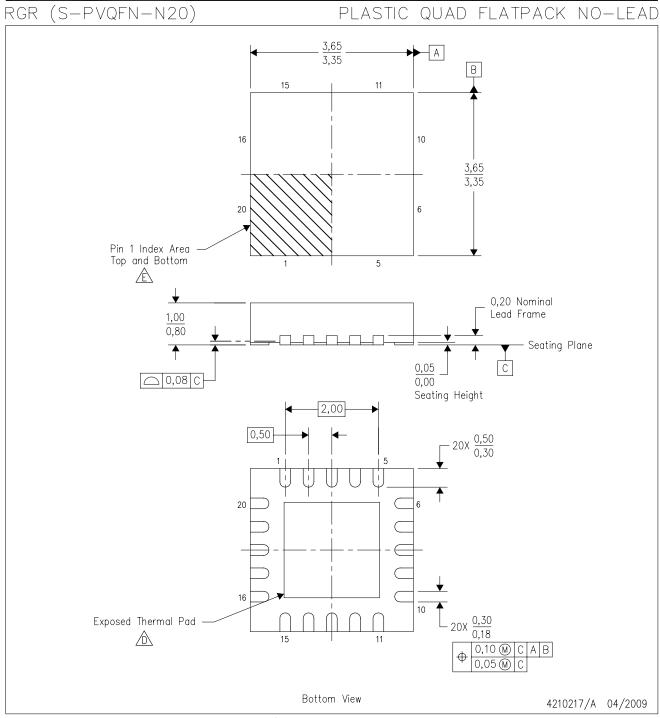

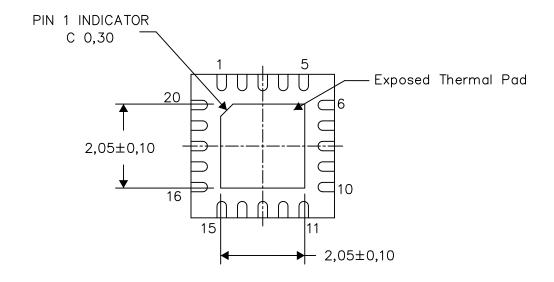

All the capabilities of bq25505 are packed into a small foot-print 20-lead 3.5 mm x 3.5 mm QFN package.

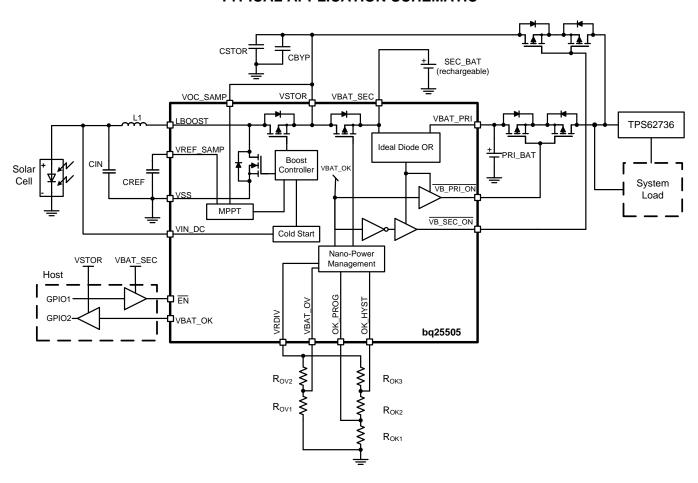

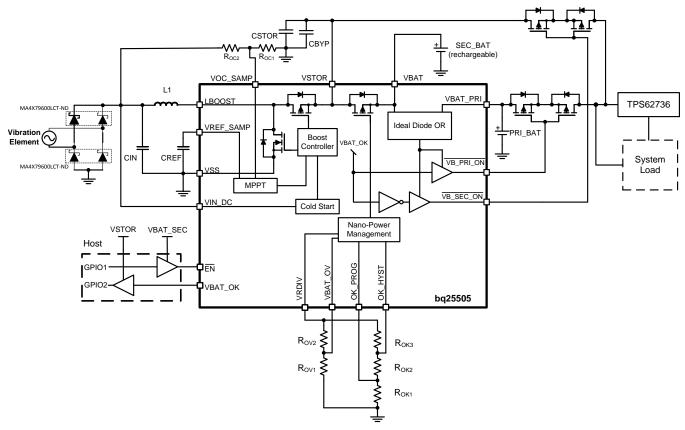

# TYPICAL APPLICATION SCHEMATIC

For Ordering Information, see the Package Option Addendum at the end of the data sheet.

# **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                                                      |                                                                                                                                              | VAL  | UE  | LINUT |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|

|                                                      |                                                                                                                                              | MIN  | MAX | UNIT  |

| Input voltage                                        | VIN_DC, VOC_SAMP, VREF_SAMP, VBAT_OV, VB_PRI_ON, VB_SEC_ON, VBAT_PRI, VBAT_SEC, VRDIV, OK_HYST, OK_PROG, VBAT_OK, VSTOR, LBST <sup>(2)</sup> | -0.3 | 5.5 | V     |

| Peak Input Power, PIN_PK                             |                                                                                                                                              |      | 400 | mW    |

| Operating junction temperature range, T <sub>J</sub> |                                                                                                                                              | -40  | 125 | °C    |

| Storage temperature range,                           | -65                                                                                                                                          | 150  | °C  |       |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to V<sub>SS</sub>/ground terminal.

# THERMAL INFORMATION

|                  | THERMAL METRIC <sup>(1)(2)</sup>             | bq25505       | LIMITO |

|------------------|----------------------------------------------|---------------|--------|

|                  | THERMAL METRIC (**/**)                       | RGR (20 PINS) | UNITS  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 34.6          |        |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 49.0          |        |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 12.5          | °C/W   |

| $\Psi_{JT}$      | Junction-to-top characterization parameter   | 0.5           | *C/VV  |

| $\Psi_{JB}$      | Junction-to-board characterization parameter | 12.6          |        |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 1.0           |        |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# RECOMMENDED OPERATING CONDITIONS

|                                     |                                                             | MIN  | NOM | MAX | UNIT |

|-------------------------------------|-------------------------------------------------------------|------|-----|-----|------|

| VIN(DC)                             | DC input voltage into VIN_DC <sup>(1)</sup>                 | 0.12 |     | 4.0 | V    |

| VBAT_SEC,<br>VBAT_PRI               | Battery voltage range (2)                                   | 2.0  |     | 5.5 | V    |

| CIN                                 | Input capacitance                                           | 4.7  |     |     | μF   |

| CSTOR                               | Storage capacitance                                         | 4.7  |     |     | μF   |

| CBAT                                | Battery pin capacitance or equivalent battery capacity      | 100  |     |     | μF   |

| CREF                                | Sampled reference storage capacitance                       | 9    | 10  | 11  | nF   |

| R <sub>OC1</sub> + R <sub>OC2</sub> | Total resistance for setting for MPPT reference.            | 18   | 20  | 22  | МΩ   |

| $R_{OK 1} + R_{OK 2} + R_{OK3}$     | Total resistance for setting the VBAT_OK threshold voltage. | 11   | 13  | 15  | МΩ   |

| $R_{OV1} + R_{OV2}$                 | Total resistance for setting VBAT_OV threshold voltage.     | 11   | 13  | 15  | ΜΩ   |

| L1                                  | Input inductance                                            | 22   |     |     | μΗ   |

| T <sub>A</sub>                      | Operating free air ambient temperature                      | -40  |     | 85  | °C   |

| $T_J$                               | Operating junction temperature                              | -40  |     | 105 | °C   |

<sup>(1)</sup> Maximum input power ≤ 400 mW. Cold start has been completed

(2) VBAT\_OV setting must be higher than VIN\_DC

<sup>(2)</sup> For thermal estimates of this device based on PCB copper area, see the TI PCB Thermal Calculator.

# **ELECTRICAL CHARACTERISTICS**

Over recommended temperature range, typical values are at  $T_A$  = 25°C. Unless otherwise noted, specifications apply for conditions of VSTOR = 4.2 V. External components, CIN = 4.7  $\mu$ F, L1 = 22  $\mu$ H, CSTOR= 4.7  $\mu$ F

|                           | PARAMETER                                                                                                        | TEST CONDITIONS                                                                                                                                                                                                                       | MIN   | TYP  | MAX  | UNIT |

|---------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------|

| BOOST CHARGER             | 1                                                                                                                |                                                                                                                                                                                                                                       |       |      |      |      |

| VIN(DC)                   | DC input voltage into VIN_DC                                                                                     | Cold-start completed                                                                                                                                                                                                                  | 120   |      | 4000 | mV   |

| I-CHG(CBC_LIM)            | Cycle-by-cycle current limit of charger                                                                          | 0.5V < V <sub>IN</sub> < 4.0 V; VSTOR = 4.2 V                                                                                                                                                                                         |       | 230  | 285  | mA   |

| PIN                       | Input power range for normal charging                                                                            | VBAT_OV > VSTOR > VSTOR_CHGEN                                                                                                                                                                                                         | 0.005 |      | 400  | mW   |

| VIN(CS)                   | Minimum input voltage for cold start circuit to start charging VSTOR                                             | VBAT_SEC < VBAT_UV;<br>VSTOR = 0 V; 0°C < T <sub>A</sub> <<br>85°C                                                                                                                                                                    |       | 330  | 400  | mV   |

| VSTOR_CHGEN               | Voltage on VSTOR when cold start operation ends and normal charger operation commences                           |                                                                                                                                                                                                                                       | 1.6   | 1.73 | 1.9  | V    |

| PIN(CS)                   | Minimum cold-start input power for VSTOR to reach VSTOR <sub>(CHGEN)</sub> and allow normal charging to commence | VSTOR < VSTOR <sub>(CHGEN)</sub>                                                                                                                                                                                                      |       | 5    |      | μW   |

| t <sub>BAT_HOT_PLUG</sub> | Time for which switch between VSTOR and VBAT_SEC closes when battery is hot plugged into VBAT_SEC                | Battery resistance = 300 $\Omega$ , Battery voltage = 3.3V                                                                                                                                                                            |       | 50   |      | ms   |

| QUIESCENT and L           | EAKAGE CURRENTS                                                                                                  |                                                                                                                                                                                                                                       |       |      |      |      |

| Iα                        | EN = GND - Full operating mode                                                                                   | VIN_DC = 0V; VSTOR = 2.1V;<br>T <sub>J</sub> = 25°C                                                                                                                                                                                   |       | 325  | 400  | nA   |

|                           |                                                                                                                  | VIN_DC = 0V; VSTOR = 2.1V;<br>-40°C < T <sub>J</sub> < 85°C                                                                                                                                                                           |       |      | 700  |      |

|                           | EN = VBAT_SEC - Ship mode                                                                                        | VBAT_SEC = VBAT_PRI = 2.1 V; T <sub>J</sub> = 25°C; VSTOR = VIN_DC = 0 V                                                                                                                                                              |       | 1    | 5    |      |

|                           |                                                                                                                  | VBAT_SEC = VBAT_PRI = 2.1 V; -40°C < T <sub>J</sub> < 85°C;<br>VSTOR = VIN_DC = 0 V                                                                                                                                                   |       |      | 20   |      |

| I-BATPRI(LEAK)            | EN = VBAT_SEC - Ship mode                                                                                        | VBAT_PRI = VBAT_SEC =<br>2.1 V; T <sub>J</sub> = 25°C; VIN_DC = 0<br>V; VSTOR floating                                                                                                                                                |       | 1    | 5    | nA   |

|                           |                                                                                                                  | $\label{eq:VBAT_PRI} \begin{array}{l} \text{VBAT\_PRI} = \text{VBAT\_SEC} = \\ 2.1 \text{ V; } -40^{\circ}\text{C} < \text{T}_{\text{J}} < 85^{\circ}\text{C;} \\ \text{VIN\_DC} = 0 \text{ V; VSTOR} \\ \text{floating} \end{array}$ |       |      | 20   | nA   |

| MOSFET RESISTA            | NCES                                                                                                             |                                                                                                                                                                                                                                       |       |      |      |      |

| RDS(ON)-BAT               | ON resistance of switch between VBAT_SEC and VSTOR                                                               | VBAT_SEC = 4.2 V                                                                                                                                                                                                                      |       | 0.95 | 1.50 | Ω    |

| RDS(ON)_CHG               | Charger low side switch ON resistance                                                                            | VBAT_SEC = 4.2 V                                                                                                                                                                                                                      |       | 0.70 | 0.90 | Ω    |

|                           | Charger high side switch ON resistance                                                                           |                                                                                                                                                                                                                                       |       | 2.30 | 3.00 | Ω    |

|                           | Charger low side switch ON resistance                                                                            | VBAT_SEC = 2.1 V                                                                                                                                                                                                                      |       | 0.80 | 1.00 | Ω    |

|                           | Charger high side switch ON resistance                                                                           |                                                                                                                                                                                                                                       |       | 3.70 | 4.80 | Ω    |

| $f_{\text{SW}}$           | Maximum charger switching frequency                                                                              |                                                                                                                                                                                                                                       |       | 1.0  |      | MHz  |

| $T_{TEMP\_SD}$            | Junction temperature when charging is discontinued                                                               | VBAT_OV > VSTOR > 1.8V                                                                                                                                                                                                                |       | 125  |      | С    |

Copyright © 2013, Texas Instruments Incorporated

# **ELECTRICAL CHARACTERISTICS (continued)**

Over recommended temperature range, typical values are at  $T_A$  = 25°C. Unless otherwise noted, specifications apply for conditions of VSTOR = 4.2 V. External components, CIN = 4.7  $\mu$ F, L1 = 22  $\mu$ H, CSTOR= 4.7  $\mu$ F

|                   | PARAMETER                                                                           | TEST CONDITIONS                         | MIN                | TYP  | MAX                      | UNIT |

|-------------------|-------------------------------------------------------------------------------------|-----------------------------------------|--------------------|------|--------------------------|------|

| BATTERY MANAGE    | MENT                                                                                |                                         |                    |      |                          |      |

| VBAT_OV           | Programmable voltage range for overvoltage threshold                                | VBAT_SEC increasing                     | 2.2                |      | 5.5                      | V    |

| VBAT_OV_HYST      | Battery over-voltage hysteresis (internal)                                          | VBAT_SEC decreasing;<br>VBAT_OV = 5.25V |                    | 24   | 45                       | mV   |

| VBAT_UV           | Under-voltage threshold                                                             | VBAT_SEC decreasing                     | 1.91               | 1.95 | 2.0                      | V    |

| VBAT_UV_HYST      | Battery under-voltage hysteresis (internal)                                         | VBAT_SEC increasing                     |                    | 15   | 32                       | mV   |

| VBAT_OK_HYST      | Programmable voltage range of digital signal indicating VSTOR (=VBAT_SEC) is OK     | VBAT_SEC increasing                     | VBAT_UV            |      | VBAT_<br>OV              | V    |

| VBAT_OK_PROG      | Programmable voltage range of digital signal indicating VSTOR (=VBAT_SEC) is OK     | VBAT_SEC decreasing                     | VBAT_UV            |      | VBAT_<br>OK_HYST<br>- 50 | mV   |

| VBAT_ACCURACY     | Overall Accuracy for threshold values VBAT_OV, VBAT_OK                              | Selected resistors are 0.1% tolerance   | -2                 |      | 2                        | %    |

| VBAT_OK(H)        | VBAT_OK (High) threshold voltage                                                    | Load = 10 μA                            |                    |      | VSTOR -<br>200           | mV   |

| VBAT_OK(L)        | VBAT_OK (Low) threshold voltage                                                     | Load = 10 µA                            |                    |      | 100                      | mV   |

| ENABLE THRESHO    | LDS                                                                                 |                                         | •                  |      |                          |      |

| EN(H)             | Voltage for EN high setting. Relative to VBAT_SEC.                                  | VBAT_SEC = 4.2V                         | VBAT_SE<br>C - 0.2 |      |                          | V    |

| EN(L)             | Voltage for EN low setting                                                          | VBAT_SEC = 4.2V                         |                    |      | 0.3                      | V    |

| BIAS and MPPT CO  | NTROL STAGE                                                                         |                                         |                    |      |                          |      |

| VOC_SAMPLE        | Time period between two MPPT samples                                                |                                         |                    | 16   |                          | S    |

| VOC_STLG          | Settling time for MPPT sample measurement of VIN_DC open circuit voltage            | Device not switching                    |                    | 256  |                          | ms   |

| VIN_REG           | Regulation of VIN_DC during charging                                                | 0.5 V < VIN < 4 V; IIN(DC) = 10 mA      |                    |      | 10%                      |      |

| MPPT_80           | Voltage on VOC_SAMP to set MPPT threshold to 0.80 of open circuit voltage of VIN_DC |                                         | VSTOR –<br>0.015   |      |                          | V    |

| MPPT_50           | Voltage on VOC_SAMP to set MPPT threshold to 0.50 of open circuit voltage of VIN_DC |                                         |                    |      | 15                       | mV   |

| VBIAS             | Internal reference for the programmable voltage thresholds                          | VSTOR ≥ VSTOR_CHGEN                     | 1.205              | 1.21 | 1.217                    | V    |

| MULTIPLEXOR       |                                                                                     | ,                                       | •                  |      |                          |      |

| t <sub>DEAD</sub> | Dead time between VB_SEC_ON and VB_PRI_ON                                           |                                         |                    | 5    | 8 <sup>(1)</sup>         | us   |

<sup>(1)</sup> Specified by design.

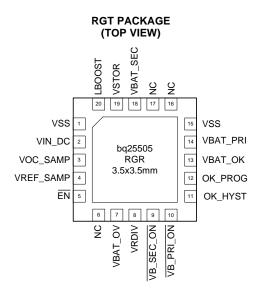

# **DEVICE INFORMATION**

Figure 1. bq25505 3.5mm x 3.5mm QFN-20 Package

# **PIN FUNCTIONS**

| PIN |           | VO TVDE  | DESCRIPTION                                                                                                                                                                                                   |  |  |  |  |

|-----|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NO. | NAME      | I/O TYPE | DESCRIPTION                                                                                                                                                                                                   |  |  |  |  |

| 1   | VSS       | Input    | General ground connection for the device                                                                                                                                                                      |  |  |  |  |

| 2   | VIN_DC    | Input    | DC voltage input from energy harvesters. Connect at least a 4.7 µF capacitor as close as possible between this pin and pin 1.                                                                                 |  |  |  |  |

| 3   | VOC_SAMP  | Input    | Sampling pin for MPPT network. Connect to VSTOR to sample at 80% of input soure open circuit voltage. Connect to GND for 50% or connect to the mid-point of external resistor divider between VIN_DC and GND. |  |  |  |  |

| 4   | VREF_SAMP | Input    | Sample and hold circuit output for the reference set by the MPPT per VOC_SAMP. Connect a 0.01 µF capacitor from this pin to GND.                                                                              |  |  |  |  |

| 5   | EN        | Input    | Active low digital programming input for enabling/disabling the IC. Connect to GND to enable the IC.                                                                                                          |  |  |  |  |

| 6   | NC        | Input    | Connect to VSS via the IC's PowerPad.                                                                                                                                                                         |  |  |  |  |

| 7   | VBAT_OV   |          | Connect to the mid-point of external resistor divider between VRDIV and GND for setting the VBAT_SEC overvoltage threshold.                                                                                   |  |  |  |  |

| 8   | VRDIV     | Output   | Connect high side of resistor divider networks to this biasing voltage.                                                                                                                                       |  |  |  |  |

| 9   | VB_SEC_ON | Output   | Active low push-pull driver for the secondary (rechargeable) energy storage PMOS FET.                                                                                                                         |  |  |  |  |

| 10  | VB_PRI_ON | Output   | Active low push-pull driver for the primary (non-rechargeable) energy storage PMOS FET.                                                                                                                       |  |  |  |  |

| 11  | OK_HYST   | Input    | Connect to the mid-point of external resistor divider between VRDIV and GND for setting the VBAT_OK hysteresis threshold.                                                                                     |  |  |  |  |

| 12  | OK_PROG   | Input    | Connect to the mid-point of external resistor divider between VRDIV and GND for setting the VBAT_OK threshold.                                                                                                |  |  |  |  |

| 13  | VBAT_OK   | Output   | Digital output for battery good indicator. Internally referenced to the VSTOR voltage.                                                                                                                        |  |  |  |  |

| 14  | VBAT_PRI  | Input    | Primary (non-rechargeable) energy storage element HiZ sense input.                                                                                                                                            |  |  |  |  |

| 15  | VSS       | Supply   | Signal ground connection for the device.                                                                                                                                                                      |  |  |  |  |

| 16  | NC        | Input    | Connect to ground using the IC's PowerPad.                                                                                                                                                                    |  |  |  |  |

| 17  | NC        | Input    | Connect to ground using the IC's PowerPad.                                                                                                                                                                    |  |  |  |  |

| 18  | VBAT_SEC  | I/O      | Connect a secondary (rechargeable) storage element with at least 100uF of equivalent capacitance to this pin.                                                                                                 |  |  |  |  |

| 19  | VSTOR     | Output   | Connection for the output of the boost converter/charger. Connect at least a 4.7 $\mu$ F capacitor in parallel with a 0.1 $\mu$ F capacitor as close as possible to between this pin and pin 1 (VSS).         |  |  |  |  |

# **PIN FUNCTIONS (continued)**

| PIN<br>NO. NAME |        | UO TYPE  | DESCRIPTION                                                                                                               |

|-----------------|--------|----------|---------------------------------------------------------------------------------------------------------------------------|

|                 |        | I/O TYPE | DESCRIPTION                                                                                                               |

| 20              | LBOOST | Input    | Inductor connection for the boost converter switching node. Connect a 22 µH inductor between this pin and pin 2 (VIN_DC). |

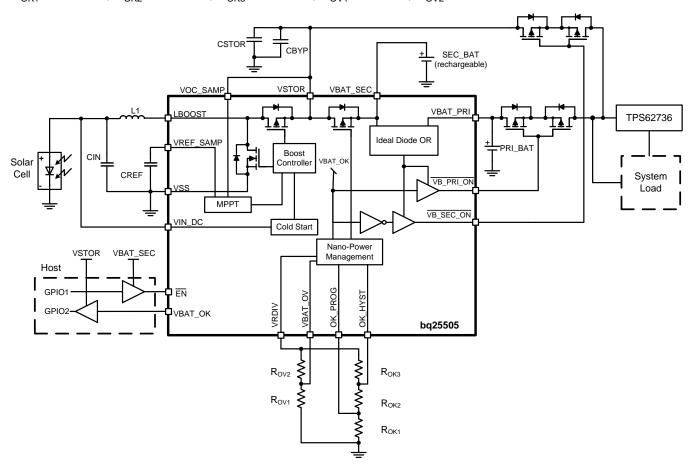

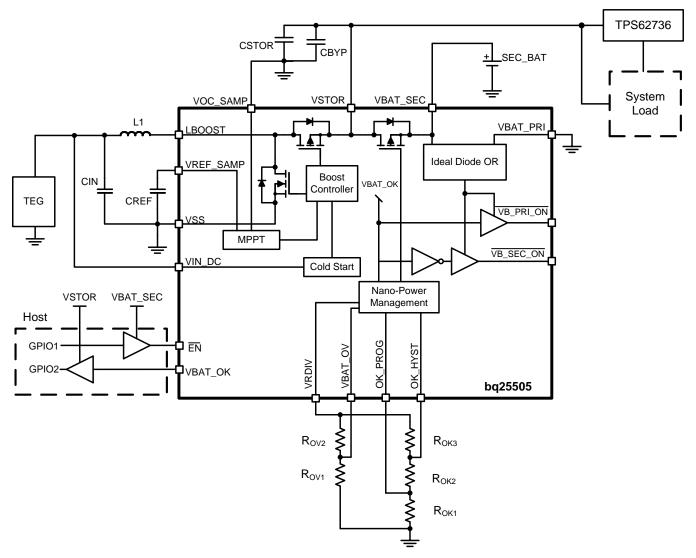

### TYPICAL APPLICATION CIRCUITS

$VBAT\_OV = 3.11 \ V, \ VBAT\_OK = 2.39 \ V, \ VBAT\_OK\_HYST = 2.80 \ V, \ MPPT \ (V_{OC}) = 80\%$   $L1 = 22 \ \mu H, \ CIN = CSTOR = 4.7 \ \mu F, \ CBYP=0.1 \ \mu F, \ CREF = 10 \ nF$   $R_{OK1} = 5.62 \ M\Omega, \ R_{OK2} = 5.49 \ M\Omega, \ R_{OK3} = 1.87 \ M\Omega, \ R_{OV1} = 7.5 \ M\Omega, \ R_{OV2} = 5.36 \ M\Omega$

Figure 2. Typical Solar Application Circuit with Primary and Secondary Batteries

$VBAT\_OV = 4.18V, \ VBAT\_OK = 3.5 \ V, \ VBAT\_OK\_HYST = 3.7 \ V, \ MPPT \ (V_{OC}) = 50\%$   $L1 = 22 \ \mu H, \ CIN = CSTOR = 4.7 \ \mu F, \ CBYP=0.1 \ \mu F, \ CREF = 10 \ nF$   $R_{OK1} = 4.22 \ M\Omega, \ R_{OK2} = 8.06 \ M\Omega, \ R_{OK3} = 0.698 \ M\Omega, \ R_{OV1} = 6.04 \ M\Omega, \ R_{OV2} = 7.87 \ M\Omega$

Figure 3. Typical TEG Application Circuit without a Primary Battery

$VBAT\_OV = 3.31 \ V, \ VBAT\_OK = 2.82 \ V, \ VBAT\_OK\_HYST = 3.12 \ V, \ MPPT \ (V_{OC}) = 40\%$   $L1 = 22 \ \mu H, \ CIN = CSTOR = 4.7 \ \mu F, \ CBYP=0.1 \ \mu F, \ CREF = 10 \ nF$   $R_{OK1} = 4.99 \ M\Omega, \ R_{OK2} = 6.65 \ M\Omega, \ R_{OK3} = 1.24 \ M\Omega, \ R_{OV1} = 6.98 \ M\Omega, \ R_{OV2} = 5.76 \ M\Omega$   $R_{OC1} = 8.06 \ M\Omega, \ R_{OC2} = 12 \ M\Omega$

Figure 4. Typical Piezoelectric Application Circuit with Primary and Secondary Batteries

Copyright © 2013, Texas Instruments Incorporated

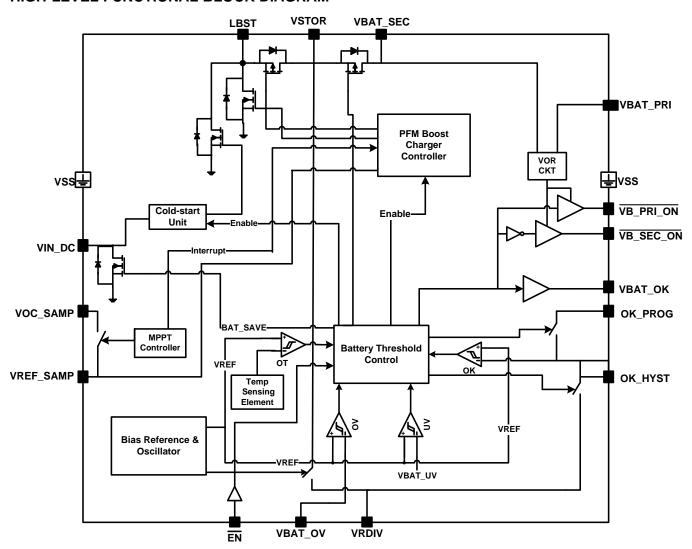

# HIGH-LEVEL FUNCTIONAL BLOCK DIAGRAM

Figure 5. High-Level Functional Diagram

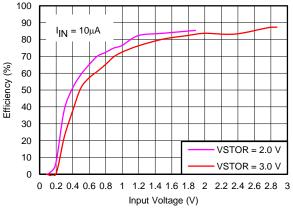

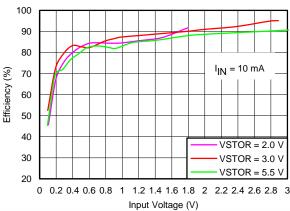

# TYPICAL CHARACTERISTICS

# **Table of Graphs**

|                                                                      | Table of Graphs                                                                             |                                                          |           |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------|

| Unless otherwise noted, graphs                                       | were taken using with CIN = 4.7µF, L1 = Coilcraft 2<br>4.7µF, VBAT_OV=4.2V                  | 22µH LPS4018, CSTOR =                                    | FIGURE    |

|                                                                      |                                                                                             | IN= 10 μA                                                | Figure 6  |

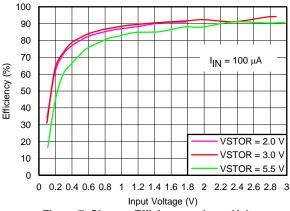

|                                                                      | vs. Input Voltage                                                                           | IN= 100 μA                                               | Figure 7  |

|                                                                      |                                                                                             | IIN = 10 mA                                              | Figure 8  |

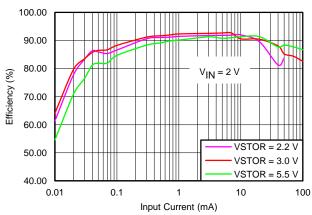

| Charger Efficiency (η) <sup>(1)</sup>                                |                                                                                             | VIN = 2.0 V                                              | Figure 9  |

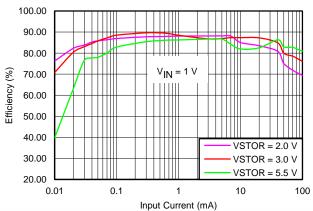

|                                                                      | va lanut Current                                                                            | VIN = 1.0 V                                              | Figure 10 |

|                                                                      | vs. Input Current                                                                           | VIN = 0.5 V                                              | Figure 11 |

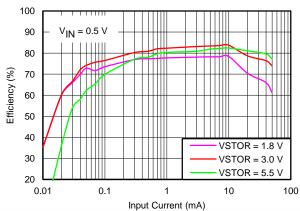

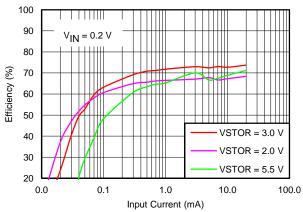

|                                                                      |                                                                                             | VIN = 0.2 V                                              | Figure 12 |

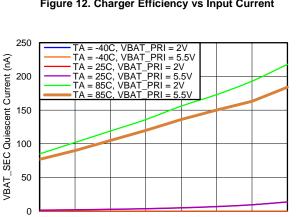

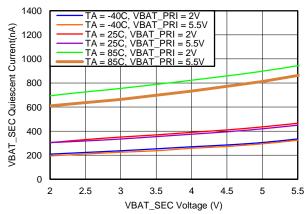

| VBAT_SEC Quiescent Current                                           | vs. VBAT_SEC Voltage                                                                        | EN = VBAT_SEC (Active Mode)                              | Figure 13 |

|                                                                      | ·                                                                                           | EN = GND (Ship Mode)                                     | Figure 14 |

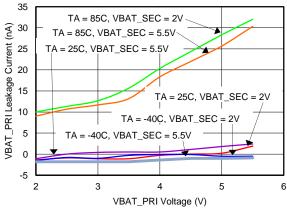

| VBAT_PRI Leakage Current                                             | vs. VBAT_PRI Voltage                                                                        | EN = VBAT_SEC (Ship Mode)                                | Figure 15 |

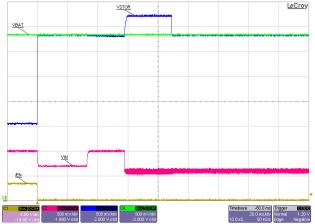

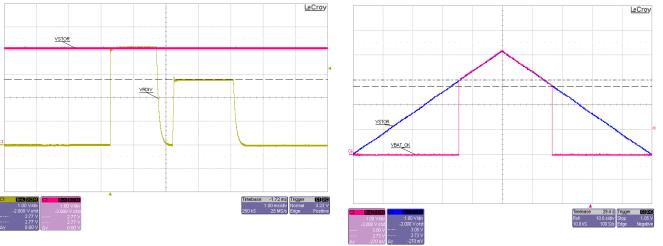

| Startup by Taking EN Low (from Ship mode)                            | VBAT = 3.4-V charged Li coin cell; VIN_DC = 1.0 V power supply; MPPT=50%; ZIN = $100\Omega$ |                                                          | Figure 16 |

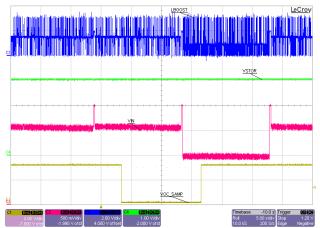

| MPPT Operation                                                       | VBAT = 3.2-V charged Li coin cell; VIN_DC = 2.0 V power supply; ZIN = $100\Omega$           | VOC_SAMP = VSTOR to GND to VSTOR                         | Figure 17 |

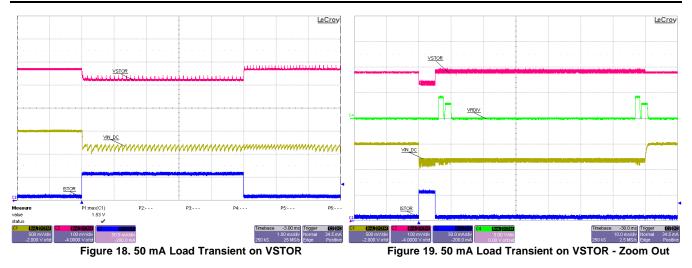

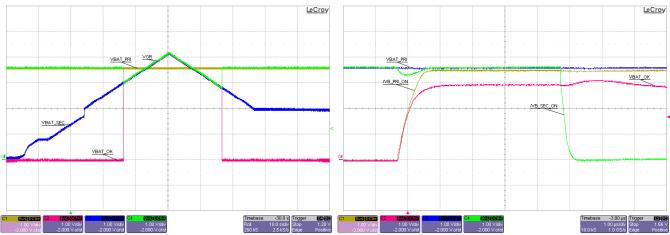

| 50mA Load Transient on VSTOR                                         | VBAT = 4.2V charged 0.5 F; VIN_DC = 1.5 V                                                   | R(VSTOR) = open to 84 $\Omega$ to open                   | Figure 18 |

| 50mA Load Transient on VSTOR with Sampling                           | power supply; MPPT=80%; ZIN = 75Ω                                                           | R(VSTOR) = open to 84 $\Omega$ to open                   | Figure 19 |

| Charger Operational Waveform<br>During 50mA Load Transient           |                                                                                             | R(VSTOR) = 84 Ω                                          | Figure 20 |

| VRDIV Waveform over Two Periods                                      | VCTOD 4 OV                                                                                  |                                                          | Figure 21 |

| VRDIV Waveform                                                       | VSTOR = 4.2V                                                                                |                                                          | Figure 22 |

| VBAT_OK Operation                                                    | VSTOR ramped from 0 V to 4.2 V to 0 V with function generator                               |                                                          | Figure 23 |

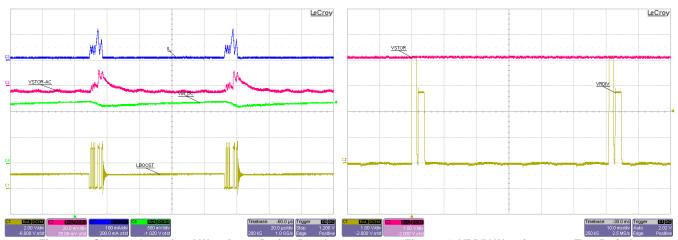

| Multiplexor Output (VOR) as<br>VBAT_SEC Crosses VBAT_OK<br>Threshold | VSTOR ramped from 0 V to 4.2 V to 0 V with function generator; VBAT_PRI = 3.6V power supply | VBAT_SEC = 0.5 F super capacitor; $1k\Omega$ load on VOR | Figure 24 |

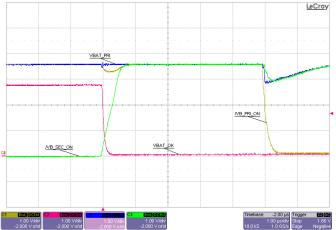

| Multiplexor Signals When VBAT_SEC > VBAT_OK Threshold                | VB_PRI_ON goes high; VB_SEC_ON goes low                                                     |                                                          | Figure 25 |

| Multiplexor Signals When VBAT_SEC < VBAT_OK Threshold                | VB_PRI_ON goes low; VB_SEC_ON goes low                                                      |                                                          | Figure 26 |

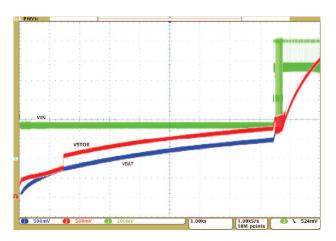

| Charging a Super Cap on VBAT                                         | VIN_DC = sourcemeter with compliance = 1.2 V and ISC = 1.0 mA                               | VBAT_SEC = 120 mF super capacitor                        | Figure 27 |

<sup>(1)</sup> See SLUA691 for an explanation on how to take these measurements. Because the MPPT feature cannot be disabled on the bq25505, these measurements need to be taken in the middle of the 16 s sampling period.

Figure 6. Charger Efficiency vs Input Voltage

Figure 8. Charger Efficiency vs Input Voltage

Figure 10. Charger Efficiency vs Input Current

Figure 7. Charger Efficiency vs Input Voltage

Figure 9. Charger Efficiency vs Input Current

Figure 11. Charger Efficiency vs Input Current

2

2.5

3

Figure 12. Charger Efficiency vs Input Current

VBAT\_SEC Voltage (V) Figure 14. Quiescent Current vs VBAT\_SEC Voltage: Ship Mode

4

3.5

5

4.5

5.5

Figure 16. Startup by Taking EN Low (from Ship mode)

Figure 13. Quiescent Current vs VBAT\_SEC Voltage: Active Mode

Figure 15. VBAT\_PRI Leakage Current vs VBAT\_PRI Voltage

Figure 17. MPPT Operation

Figure 20. Charger Operational Waveforms During 50 mA Load Transient

Figure 21. VRDIV Waveform over Two Periods

Figure 22. VRDIV Waveform

Figure 23. VBAT\_OK Operation

Figure 24. Multiplexor Output (VOR) as VBAT\_SEC Crosses VBAT\_OK Threshold

Figure 25. MUX Signals When VBAT\_SEC > VBAT\_OK Threshold

Figure 26. MUX Signals When VBAT\_SEC < VBAT\_OK threshold

Figure 27. Charging a Super Cap on VBAT\_SEC

#### **DETAILED DESCRIPTION**

# **Boost Charger Overview**

The bq25505 is based on an ultra low quiescent current, efficient synchronous boost charger. The boost converter is intended to be powered from a high impedance DC source, such as a solar panel, TEG or piezoelectric module; therefore, it regulates its input voltage (VIN\_DC) in order to prevent the input source from collapsing. The boost converter monitors its output voltage (VSTOR) and stops switching when VSTOR reaches a resistor programmable threshold level. The boost charger is based on a switching regulator architecture which maximizes efficiency while minimizing start-up and operation power. It uses pulse frequency modulation (PFM) to maintain efficiency, even under light load conditions. In addition, the boost charger implements battery protection features so that either rechargeable batteries or capacitors can be used as energy storage elements at the rechargeable storage element output (VBAT\_SEC). Figure 5 is a high-level functional block diagram which highlights most of the major functional blocks inside the bq25505.

#### **Enable Controls**

There is one enable pin implemented in bq25505 in order to maximize the flexibility of control for the system. When taken high, the EN pin shuts down the IC completely including the boost converter and battery management circuitry. It also turns off the PFET that connects VBAT\_SEC to VSTOR. This can be described as ship mode, because it will put the IC in the lowest leakage state and provide a long storage period without discharging the battery on VBAT\_SEC. If there is no need to control EN, it is recommended that this pin be tied to VSS, or system ground.

# **Startup Operation**

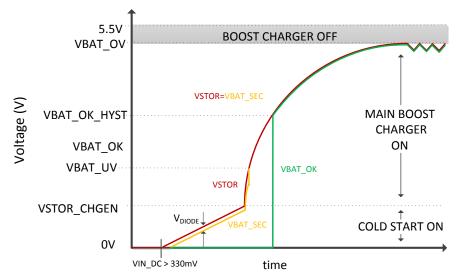

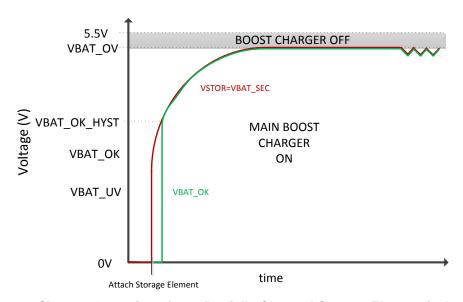

The bq25505 has two circuits for boosting the input voltage, a low-power cold-start circuit, drawing power exclusively from VIN\_DC when ≥ VIN(CS), and the high efficiency main boost charger, with the bias rails drawing power from VSTOR when ≥ VSTOR\_CHGEN and the power stage drawing power from VIN\_DC when ≥ VIN(DC) minimum. When EN = 0 and VSTOR ≤ VSTOR CHGEN, there are two options for charging the VSTOR capacitor, CSTOR, to VSTOR CHGEN for the main boost converter to turn on. The first option, shown in Figure 28, is to allow the cold start circuit to charge VSTOR to VSTOR\_CHGEN. Due to the body diode of the PFET connecting VSTOR and VBAT\_SEC, the cold start circuit must charge both the capacitor on CSTOR and the storage element connected to VBAT\_SEC up to VSTOR\_CHGEN. When a rechargeable battery with an open protector is attached, the charge time is typically short due to the minimum charge needed to close the FET. When large, discharged super capacitors are attached, the charge time can be signficant. The second option, shown in Figure 29, is to connect a storage element, charged above VSTOR\_CHGEN, to VBAT\_SEC. Assuming the voltages on VSTOR and VBAT\_SEC are both below 100mV, when a charged storage element is attached (i.e. hot-plugged) to VBAT\_SEC, the IC turns on the internal PFET between the VSTOR and VBAT\_SEC pins for t<sub>BAT HOT PLUG</sub> in order to charge CSTOR to VSTOR\_CHGEN. If a system load tied to VSTOR prevents the storage element from charging VSTOR within t<sub>BAT HOT PLUG</sub>, it is recommended to add an external PFET between the system load and VSTOR. An inverted VBAT\_OK signal can be used to drive the gate of this system-isolating PFET. Once the VSTOR pin voltage reaches the internal under voltage threshold (VBAT\_UV), the internal PFET stays on and the main boost charger begins to charge the storage element if there is sufficient power available at the VIN\_DC pin, as explained below. If VSTOR does not reach VBAT\_UV within 50ms, then the PFET turns off and the cold-start boost converter turns on, also as explained below.

#### Boost Charger Cold-Start Operation (VSTOR < VSTOR CHGEN and VIN DC > VIN(CS))

If the attached storage element does not charge CSTOR above VSTOR\_CHGEN, VIN\_DC ≥ VIN(CS), the cold-start circuit turns on. The cold-start circuit is essentially an unregulated boost converter with lower efficiency compared to the main boost converter. The energy harvester must supply sufficient power for the IC to exit cold start. See the Energy Harvester Selection applications section for guidance.

When the CSTOR voltage reaches VSTOR\_CHGEN, the main boost charger starts up. The VSTOR voltage from the main boost charger is compared against the battery undervoltage threshold (VBAT\_UV). When the VBAT\_UV threshold is reached, the PMOS switch between VSTOR and VBAT\_SEC turns on, which allows the energy storage element attached to VBAT\_SEC to charge up. Cold start is not as efficient as the main boost regulator. If sufficient input power is not available, it is possible that the cold start circuit continuously runs and the VSTOR output does not increase above VSTOR\_CHGEN for the main boost conveter to start up. The battery management thresholds are explained later is this section. See the Energy Harvester Selection applications section for guidance on minimum input power requirements.

## Main Boost Charger Operation (VSTOR > VSTOR\_CHGEN and VIN\_DC > VIN(DC) )

The main boost charger charges the storage element attached to VBAT\_SEC with the energy available from the high impedance input source. For the first 32 ms (typical) after the main converter is turned ON (assuming EN is low), the charger is disabled to let the input rise to its open-circuit voltage. This sample period is required to get the reference voltage which will be used for the remainder of the charger operation till the next MPPT sampling cycle turns ON. The boost charger employs pulse frequency modulation (PFM) mode of control to regulate the voltage at VIN\_DC close to the desired reference voltage. The reference voltage is set by the MPPT control scheme as described in the next section. Input voltage regulation is obtained by transferring charge from the input to VSTOR only when the input voltage is higher than the voltage on pin VREF\_SAMP. The current through the inductor is controlled through internal current sense circuitry. The peak current in the inductor is dithered internally to pre-determined levels in order to maintain high efficiency of the converter across a wide input current range. The converter transfers up to a maximum of 100 mA average input current (230mA typical peak inductor current). The boost charger is disabled when the voltage on VSTOR reaches the user set VBAT\_OV threshold to protect the battery connected at VBAT\_SEC from overcharging. In order for the battery to charge to VBAT\_OV, the input power must exceed the power needed for the load on VSTOR. See the Energy Harvester Selection applications section for guidance on minimum input power requirements.

## **Maximum Power Point Tracking**

Maximum power point tracking (MPPT) is implemented in order to maximize the power extracted from an energy harvester source. MPPT is performed by periodically sampling a ratio of the open-circuit voltage of the energy harvester and using that as the reference voltage (VREF\_SAMP) to the boost converter. Internally, the boost converter indirectly modulates the impedance of the energy transfer circuitry by regulating the input voltage (VIN\_DC) to the sampled reference voltage (VREF\_SAMP). A new reference voltage is obtained every 16 s (typical) by periodically disabling the charger for 256 ms (typical) and sampling a ratio of the open-circuit voltage. For solar harvesters, the maximum power point is typically 70%-80% and for thermoelectric harvesters, the MPPT is typically 50%. Tying VOC\_SAMP to VSTOR internally sets the MPPT regulation point to 80%. Tying VOC\_SAMP to GND internally sets the MPPT regulation point to 50%. If input source does have either 80% or 50% of VOC as its MPP point, the exact ratio for MPPT can be optimized to meet the needs of the input source being used by connecting external resistors  $R_{\rm OC1}$  and  $R_{\rm OC2}$  between VRDIV and GND with mid-point at VOC\_SAMP.

The reference voltage is set by the following expression:

$$VREF\_SAMP = VIN\_DC(OpenCircuit) \left( \frac{R_{OC1}}{R_{OC1} + R_{OC2}} \right)$$

(1)

# **Storage Element / Battery Management**

In this section the battery management functionality of the bq25505 integrated circuit (IC) is presented. The IC has internal circuitry to manage the voltage across the storage element and to optimize the charging of the storage element. For successfully extracting energy from the source, two different threshold voltages must be programmed using external resistors, namely battery good threshold (VBAT\_OK) and over voltage (OV) threshold. The two user programmable threshold voltages and the internally set undervoltage threshold determine the IC's region of operation. Figure 28 and Figure 29 show plots of the voltage at the VSTOR pin and the various threshold voltages for two use cases 1) when a depleted battery on VBAT\_SEC is attached and the charger enters cold start and 2) when a battery at VBAT\_SEC charged above VBAT\_UV is attached. For the best operation of the system, the VBAT\_OK should be used to determine when a load can be applied or removed. A detailed description of the three voltage thresholds and the procedure for designing the external resistors for setting the three voltage thresholds are described next.

Figure 28. Charger Operation after a Depleted Storage Element is Attached

Figure 29. Charger Operation after a Partially Charged Storage Element is Attached

When no input source is attached, the VSTOR node should be discharged to ground before attaching a storage element. Hot-plugging a storage element that is charged (e.g., the battery protector PFET is closed) and with the VSTOR node above ground results in the PFET between VSTOR and VBAT\_SEC remaining off until an input source is attached. In addition, if a system load attached to VSTOR has fast transients that could pull VSTOR below VBAT\_UV, the internal PFET switch will turn off in order to recharge the CSTOR capacitor to VSTOR\_CHGEN. See the application section for guidance on sizing the VSTOR and/or VBAT\_SEC capacitance to account for transients. If the voltage applied at VIN\_DC is greater than VSTOR or VBAT\_SEC then current may flow until the voltage at the input is reduced or the voltage at VSTOR and VBAT\_SEC rise. This is considered an abnormal condition and the boost charger does not operate.

# **Battery Undervoltage Protection**

To prevent rechargeable batteries from being deeply discharged and damaged, and to prevent completely depleting charge from a capacitive storage element, the IC has an internally set undervoltage (VBAT\_UV) threshold plus an internal hysteresis voltage (VBAT\_UV\_HYST). The VBAT\_UV threshold voltage when the battery voltage is decreasing is internally set to 1.95V (typical). The undervoltage threshold when battery voltage is increasing is given by VBAT\_UV plus VBAT\_UV\_HYST. For most applications, the system load should be

connected to the VSTOR pin while the storage element should be connected to the VBAT\_SEC pin. Once the VSTOR pin voltage goes above the VBAT\_UV\_HYST threshold, the VSTOR pin and the VBAT\_SEC pins are shorted. The switch remains closed until the VSTOR pin voltage falls below VBAT\_UV. The VBAT\_UV threshold should be considered a fail safe to the system; therefore the system load should be removed or reduced based on the VBAT\_OK threshold which should be set above the VBAT\_UV threshold.

## **Battery Overvoltage Protection**

To prevent rechargeable batteries from being exposed to excessive charging voltages and to prevent over charging a capacitive storage element, the over-voltage (VBAT\_OV) threshold level must be set using external resistors. This is also the voltage value to which the charger will regulate the VSTOR/VBAT\_SEC pin when the input has sufficient power. The VBAT\_OV threshold when the battery voltage is rising is given by Equation 2:

$$VBAT_OV = \frac{3}{2}VBIAS\left(1 + \frac{R_{OV2}}{R_{OV1}}\right)$$

(2)

The sum of the resistors is recommended to be no higher than 13 M $\Omega$  that is,  $R_{OV1}+R_{OV2}=13$  M $\Omega$ . The overvoltage threshold when battery voltage is decreasing is given by OV\_HYST. It is internally set to the over voltage threshold minus an internal hysteresis voltage denoted by VBAT\_OV\_HYST. Once the voltage at the battery exceeds VBAT\_OV threshold, the boost converter is disabled. The charger starts again once the battery voltage falls below the VBAT\_OV\_HYST level. When there is excessive input energy, the VBAT pin voltage will ripple between the VBAT\_OV and the VBAT\_OV\_HYST levels. SLUC484 provides help on sizing and selecting the resistors.

#### **CAUTION**

If VIN\_DC is higher than VSTOR and VSTOR is higher than VBAT\_OV, the input VIN\_DC is pulled to ground through a small resistance to stop further charging of the attached battery or capacitor. It is critical that if this case is expected, the impedance of the source attached to VIN\_DC be higher than 20  $\Omega$  and not a low impedance source.

#### Battery Voltage in Operating Range (VBAT\_OK Output)

The IC allows the user to set a programmable voltage independent of the overvoltage and undervoltage settings to indicate whether the VSTOR voltage (and therefore the VBAT\_SEC voltage when the PFET between the two pins is turned on) is at an acceptable level. When the battery voltage is decreasing the threshold is set by Equation 3:

$$VBAT_OK_PROG = VBIAS \left(1 + \frac{R_{OK2}}{R_{OK1}}\right)$$

(3)

When the battery voltage is increasing, the threshold is set by Equation 4:

VBAT\_OK\_HYST = VBIAS

$$\left(1 + \frac{R_{OK2} + R_{OK3}}{R_{OK1}}\right)$$

(4)

The sum of the resistors is recommended to be no higher than approximately i.e.,  $R_{OK1} + R_{OK2} + R_{OK3} = 13 \text{ M}\Omega$ . The logic high level of this signal is equal to the VSTOR voltage and the logic low level is ground. The logic high level has ~20 K $\Omega$  internally in series to limit the available current to prevent MCU damage until it is fully powered. The VBAT\_OK\_PROG threshold must be greater than or equal to the UV threshold. For the best operation of the system, the VBAT\_OK should be setup to drive an external PFET between VSTOR and the system load in order to determine when the load can be applied or removed to optimize the storage element capacity. SLUC484 provides help on sizing and selecting the resistors.

## **Push-Pull Multiplexor Drivers**

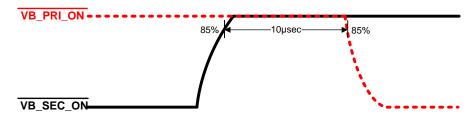

There are two push-pull drivers intended to mulitplex between a primary non-rechargeable connected at VBAT\_PRI and secondary storage element connected on VBAT\_SEC based on the VBAT\_OK signal. When the VBAT\_OK signal goes high, indicating that the secondary rechargeable battery at VBAT\_SEC is above the VBAT\_OK\_HYST threshold, the VB\_PRI\_ON output goes high followed by the VB\_SEC\_ON signal going low in order to connect VBAT\_SEC to the system output (referred to as the VOR node). When VBAT\_OK goes low, indicating that the secondary rechargeable battery at VBAT\_SEC is below the VBAT\_OK threshold, the VB\_SEC\_ON output goes high followed by the VB\_PRI\_ON signal going low in order to connect VBAT\_PRI to the system. The drivers are designed to support up to 2 nF of gate capacitance and to drive a PMOS FET. The switching characteristics follow a break-before-make model, wherein during a transition, the drivers both go high for a typical dead time of 5 us before one of the signals goes low. The figure below shows the FET gate voltages for the transition from the secondary battery being connected to the system to the primary battery being connected.

Figure 30. Break-Before-Make Operation of VB PRI ON and VB SEC ON

#### Steady State Operation and Cycle by Cycle Behavior

Steady state operation for the boost charger is shown in Figure 20. These plots highlight the inductor current waveform, the VSTOR voltage ripple, and the LBOOST switching nodes. The charger uses hysteretic control and pulse frequency modulation (PFM) switching in order to maintain high efficiency at light load. As long as the VIN\_DC voltage is above the MPPT regulation set point (i.e. voltage at VREF\_SAMP), the boost charger's low-side power FET turns on and draws current until it reaches its respective peak current limit. These switching bursts continue until VSTOR reaches the VBAT\_OV threshold. This cycle-by-cycle minor switching frequency is a function of each converter's inductor value, peak current limit and voltage levels on each side of each inductor. Once the VSTOR capacitor, CSTOR, droops below a minimum value, the hysteretic switching repeats.

### **Nano-Power Management and Efficiency**

The high efficiency of the bq25505 charger is achieved via the proprietary Nano-Power management circuitry and algorithm. This feature essentially samples and holds all references (except for VBAT\_UV) in order to reduce the average quiescent current. That is, the internal circuitry is only active for a short period of time and then off for the remaining period of time at the lowest feasible duty cycle. A portion of this feature can be observed in Figure 21 where the VRDIV node is monitored. Here the VRDIV node provides a connection to the VSTOR voltage (first pulse) and then generates the reference levels for the VBAT\_OV and VBAT\_OK resistor dividers for a short period of time. The divided down values at each pin are sampled and held for comparison against VBIAS as part of the hysteretic control. Since this biases a resistor string, the current through these resistors is only active when the Nano-Power management circuitry makes the connection—hence reducing the overall quiescent current due to the resistors. This process repeats every 64 ms.

The bq25505's boost charger efficiency is shown for various input power levels in Figure 6 through Figure 12. All data points were captured by averaging the overall input current. This must be done due to the periodic biasing scheme implemented via the Nano-Power management circuitry. In order to properly measure the resulting input current when calculating the output to input efficiency, the input current efficiency data was gathered using a source meter set to average over at least 50 samples.

#### **Thermal Shutdown**

Rechargeable Li-ion batteries need protection from damage due to operation at elevated temperatures. The application should provide this battery protection and ensure that the ambient temperature is never elevated greater than the expected operational range of 85°C.

The bq25505 uses an integrated temperature sensor to monitor the junction temperature of the device. The temperature threshold for thermal protection is set to 125°C. Once the temperature threshold is exceeded, the boost converter/charger is disabled and charging ceases. Once the temperature of the device drops below this threshold, the boost converter and or charger can resume operation. To avoid unstable operation near the overtemp threshold, a built-in hysteresis of approximately 5°C has been implemented. Care should be taken to not over discharge the battery in this condition since the boost converter/charger is disabled. However, if the supply voltage drops to the VBAT\_UV setting, then the switch between VBAT\_SEC and VSTOR will open and protect the battery even if the device is in thermal shutdown.

#### APPLICATION INFORMATION

# **Energy Harvester Selection**

The energy harvesting source (e.g., solar panel, TEG, vibration element) must provide a minimum level of power for the IC to operate as designed. The IC's minimum input power required to exit cold start can be estimated as:

$$PIN > [(I-STR\_ELM\_LEAK_{@1.8V} \times 1.8V) + (1.8V^2 / RSTOR(CS))] / 0.05$$

where I-STR\_ELM\_LEAK @1.8V is the storage element leakage current at 1.8V and

RSTOR(CS) is the equivalent resitive load on VSTOR during cold start and 0.05 is an estimate of the worst case efficiency of the cold start circuit.

Once the IC is out of cold start and the system load has been activated (e.g., using the VBAT\_OK signal), the energy harvesting element must provide the main boost charger with at least enough power to meet the average system load. Assuming RSTOR(AVG) represents the average resistive load on VSTOR, the simplified equation below gives an estimate of the IC's minimum input power needed during system operation:

PIN X

$$\eta_{EST}$$

> PLOAD = (VBAT\_OV<sup>2</sup> / RSTOR(AVG) + VBAT\_OV \* I-STR\_ELM\_LEAK<sub>@VBAT\_OV</sub>)

where n<sub>EST</sub> can be derived from the datasheet efficiency curves for the given input voltage and current and VBAT OV. The simplified equation above assumes that, while the harvester is still providing power, the system goes into low power or sleep mode long enough to charge the storage element so that it can power the system when the harvester eventually is down. Refer to SLUC461 for a design example that sizes the energy harvester.

# **Storage Element Selection**

In order for the charge management circuitry to protect the storage element from over-charging or discharging, the storage element must be connected to VBAT pin and the system load tied to the VSTOR pin. Many types of elements can be used, such as capacitors, super capacitors or various battery chemistries. A storage element with 100uF equivalent capacitance is required to filter the pulse currents of the PFM switching converter. The equivalent capacitance of a battery can be computed as computed as:

$$C_{EQ} = 2 \times mAHr_{BAT(CHRGD)} \times 3600 \text{ s/Hr} / V_{BAT(CHRGD)}$$

In order for the storage element to be able to charge VSTOR capacitor (CSTOR) within the  $t_{VB\ HOT\ PLUG}$  (50 ms typical) window at hot-plug; therefore preventing the IC from entering cold start, the time constant created by the storage element's series resistance (plus the resistance of the internal PFET switch) and equivalent capacitance must be less than t<sub>VB HOT PLUG</sub>. For example, a battery's resistance can be computed as:

$$R_{BAT} = V_{BAT} / I_{BAT(CONTINUOUS)}$$

from the battery specifications.

The storage element must be sized large enough to provide all of the system load during periods when the harvester is no longer providing power. The harvester is expected to provide at least enough power to fully charge the storage element while the system is in low power or sleep mode. Assuming no load on VSTOR (i.e., the system is in low power or sleep mode), the following equation estimates charge time from voltage VBAT1 to VBAT2 for given input power is:

PIN x

$$\eta_{EST}$$

X  $t_{CHRG} = 1/2$  X CEQ X (VBAT2<sup>2</sup> - VBAT1<sup>2</sup>)

Refer to SLUC461 for a design example that sizes the storage element.

Note that if there are large load transients or the storage element has significant impedance then it may be necessary to increase the CSTOR capacitor from the 4.7uF minimum or add additional capacitance to VBAT in order to prevent a droop in the VSTOR voltage. See below for guidance on sizing capacitors.

#### Inductor Selection

The boost charger needs an appropriately sized inductor for proper operation. The inductor's saturation current should be at least 25% higher than the expected peak inductor currents recommended below if system load transients on VSTOR are expected. Since this device uses hysteretic control, the boost charger is considered naturally stable systems (single order transfer function).

For the boost charger to operate properly, an inductor of appropriate value must be connected between LBOOST, pin 20, and VIN\_DC, pin 2. The boost converter internal control circuitry is designed to control the switching behavior with a nominal inductance of 22  $\mu$ H  $\pm$  20%. The inductor must have a peak current capability of > 300 mA with a low series resistance (DCR) to maintain high efficiency.

A list of inductors recommended for this device is shown in Table 1.

#### Table 1.

| Inductance (µH) | Dimensions (mm) | Part Number  | Manufacturer |  |  |

|-----------------|-----------------|--------------|--------------|--|--|

| 22              | 4.0x4.0x1.7     | LPS4018-223M | Coilcraft    |  |  |

| 22              | 3.8x3.8x1.65    | 744031220    | Wuerth       |  |  |

# **Capacitor Selection**

In general, all the capacitors need to be low leakage. Any leakage the capacitors have will reduce efficiency, increase the quiescent current and diminish the effectiveness of the IC for energy harvesting.

## **VREF SAMP Capacitance**

The MPPT operation depends on the sampled value of the open circuit voltage and the input regulation follows the voltage stored on the CREF capacitor. This capacitor is sensitive to leakage since the holding period is around 16 seconds. As the capacitor voltage drops due to any leakage, the input regulation voltage also drops preventing proper operation from extraction the maximum power from the input source. Therefore, it is recommended that the capacitor be an X7R or COG low leakage capacitor.

#### **VIN DC Capacitance**

Energy from the energy harvester input source is initially stored on a capacitor, CIN, connected to VIN\_DC, pin 2, and VSS, pin 1. For energy harvesters which have a source impedance which is dominated by a capacitive behavior, the value of the harvester capacitor should scaled according to the value of the output capacitance of the energy source, but a minimum value of 4.7 µF is recommended.

#### **VSTOR Capacitance**

Operation of the bq25505 requires two capacitors to be connected between VSTOR, pin 19, and VSS, pin 1. A high frequency bypass capacitor of at 0.01  $\mu$ F should be placed as close as possible between VSTOR and VSS. In addition, a low ESR capacitor of at least 4.7  $\mu$ F should be connected in parallel.

#### Additional Capacitance on VSTOR or VBAT SEC

If there are large, fast system load transients and/or the storage element has high resistance, then the CSTOR capacitors may momentarily discharge below the VBAT\_UV threshold in response to the transient. This causes the bq25505 to turn off the PFET switch between VSTOR and VBAT\_SEC and turn on the boost converter. The CSTOR capacitors may further discharge below the VSTOR\_CHGEN threshold and cause the bq25505 to enter Cold Start. For instance, some Li-ion batteries or thin-film batteries may not have the current capacity to meet the surge current requirements of an attached low power radio. To prevent VSTOR from drooping, either increasing the CSTOR capacitance or adding additional capacitance in parallel with the storage element is recommended. For example, if boost charger is configured to charge the storage element to 4.2 V and a 500 mA load transient of 50 µs duration infrequently occurs, then, solving I = C x dv/dt for CSTOR gives:

CSTOR ≥ 500 mA x 50

$$\mu$$

s/(4.2 V − 1.8 V) = 10.5  $\mu$ F (5)

Note that increasing CSTOR is the recommended solution but will cause the boost charger to operate in the less efficient cold start mode for a longer period at startup compared to using CSTOR = 4.7  $\mu$ F. If longer cold start run times are not acceptable, then place the additional capacitance in parallel with the storage element.

For a recommended list of standard components, see the EVM User's guide (SLUUAA8).

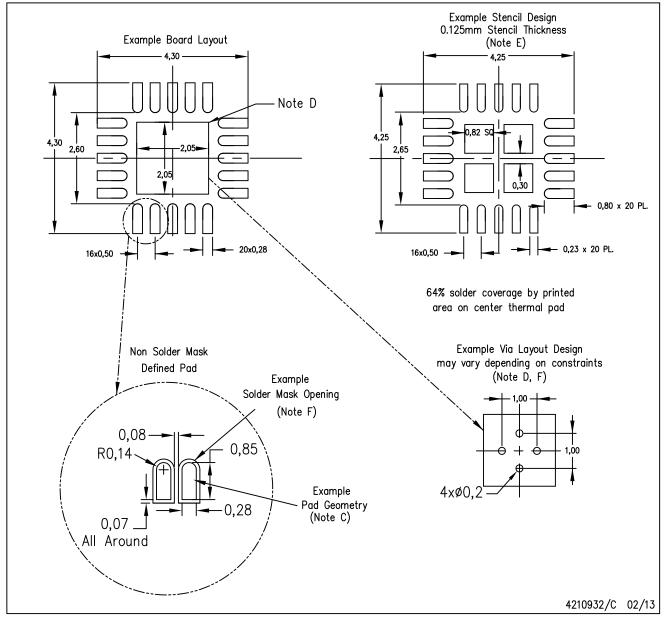

#### LAYOUT CONSIDERATIONS

As for all switching power supplies, the PCB layout is an important step in the design, especially at high peak currents and high switching frequencies. If the layout is not carefully done, the boost converter/charger and buck converter could show stability problems as well as EMI problems. Therefore, use wide and short traces for the main current path and for the power ground paths. The input and output capacitors as well as the inductors should be placed as close as possible to the IC. For the boost converter / charger, first priority are the output capacitors, including the 0.1 uF bypass capacitor (CBYP), followed by CSTOR, which should be placed as close as possible between VSTOR, pin 19, and VSS, pin 1. Next, the input capacitor, CIN, should be placed as close as possible between VIN\_DC, pin 2, and VSS, pin 1. Last in priority is the boost charger inductor, L1, which should be placed close to LBOOST, pin 20, and VIN\_DC, pin 2. It is best to use vias and bottom traces for connecting the inductors to their respective pins instead of the capacitors.

To minimize noise pickup by the high impedance voltage setting nodes (VBAT\_OV, OK\_PROG, OK\_HYST), the external resistors should be placed so that the traces connecting the midpoints of each divider to their respective pins are as short as possible. When laying out the non-power ground return paths (e.g. from resistors and CREF), it is recommended to use short traces as well, separated from the power ground traces and connected to VSS pin 15. This avoids ground shift problems, which can occur due to superimposition of power ground current and control ground current. The PowerPad should not be used as a power ground return path.

The remaining pins are either NC pins, that should be connected to the PowerPad as shown below, or digital signals with minimal layout restrictions. See the EVM user's guide for an example layout (SLUUAA8).

In order to maximize efficiency at light load, the use of voltage level setting resistors > 1 M $\Omega$  is recommended. In addition, the sample and hold circuit output capacitor on VREF\_SAMP must hold the voltage for 16 s. During board assembly, contaminants such as solder flux and even some board cleaning agents can leave residue that may form parasitic resistors across the physical resistors/capacitors and/or from one end of a resistor/capacitor to ground, especially in humid, fast airflow environments. This can result in the voltage regulation and threshold levels changing significantly from those expected per the installed components. Therefore, it is highly recommended that no ground planes be poured near the voltage setting resistors or the sample and hold capacitor. In addition, the boards must be carefully cleaned, possibly rotated at least once during cleaning, and then rinsed with de-ionized water until the ionic contamination of that water is well above 50 Mohm. If this is not feasible, then it is recommended that the sum of the voltage setting resistors be reduced to at least 5X below the measured ionic contamination.

# THERMAL CONSIDERATIONS

Implementation of integrated circuits in low-profile and fine-pitch surface-mount packages typically requires special attention to power dissipation. Many system-dependent issues such as thermal coupling, airflow, added heat sinks and convection surfaces, and the presence of other heat-generating components affect the power-dissipation limits of a given component.

Three basic approaches for enhancing thermal performance are listed below.

- Improving the power-dissipation capability of the PCB design

- Improving the thermal coupling of the component to the PCB

- · Introducing airflow in the system

For more details on how to use the thermal parameters in the Thermal Table, check the Thermal Characteristics Application Note (SZZA017) and the IC Package Thermal Metrics Application Note (SPRA953).

# **REVISION HISTORY**

| Cł | hanges from Original (August 2013) to Revision A | Page |

|----|--------------------------------------------------|------|

| •  | Changed from Product Preview to Production Data  | 1    |

# PACKAGE OPTION ADDENDUM

2-Oct-2013

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|----------------|---------|

| BQ25505RGRR      | ACTIVE | VQFN         | RGR                | 20   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR |              | BQ505          | Samples |

| BQ25505RGRT      | ACTIVE | VQFN         | RGR                | 20   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR |              | BQ505          | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 1-Oct-2013

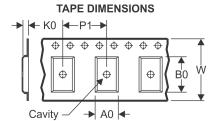

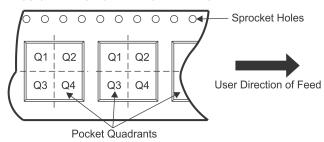

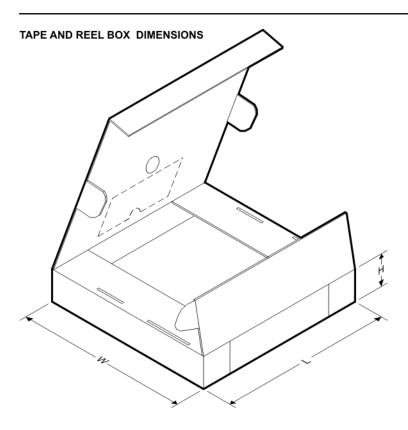

# TAPE AND REEL INFORMATION