# VG6640, VD6640

# Automotive 1.3 megapixel high-dynamic range image sensor

Datasheet - production data

#### **Features**

- · AEC-Q100 qualified

- 1.3 megapixel resolution sensor (1304 x 980) in 1/2.7 inch optical format

- High dynamic range (HDR) pixel architecture, up to 132 dB dynamic range

- Best in class FSI high pixel sensitivity with 3.75 µm pixel size

- 45 frames per second at full resolution,

60 frames per second at 720p resolution

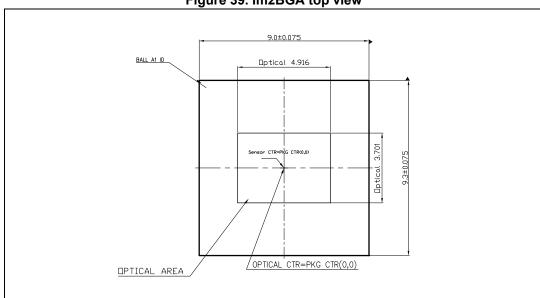

- Small physical size: 9.0 mm x 9.3 mm Im2BGA

- Synchronization for multiple cameras

- Highly configurable HDR image pre-processing

- Motion and Flicker tolerant HDR options including flicker flag to denote affected pixels

- Comprehensive inline pixel defect correction

- Fast+ I<sup>2</sup>C control interface

- MIPI CSI-2 (copyright© 2005-2010 MIPI Alliance, Inc. Standard for Camera Serial Interface 2 (CSI-2) version 1.01, limited to 1 Gbps per lane) version 1.01 serial and/or 12-bit parallel video data interface

- Automotive Safety Integrity Level (ASIL) data included as part of each frame

- Operating junction temperature: -40°C to +125°C

This is information on a product in full production.

## **Description**

This is a high performance, high dynamic range 1.3 megapixel image sensor. Designed for automotive, security and other demanding outdoor applications, the device offers supreme low light performance and numerous safety integrity features.

An embedded Bayer and monochrome data preprocessor integrates a wide range of image enhancement functions, designed to ensure high image quality.

An advanced synchronization facility allows stereo and multi-camera systems to work synchronously, minimizing system latency and motion temporal mismatch artifacts.

Table 1. Device summary

| Device | Color filter         | Package |  |

|--------|----------------------|---------|--|

| VG6640 | RGB Bayer            | Im2BGA  |  |

| VD6640 | RGB Bayer None (bare |         |  |

www.st.com

June 2018 DocID023597 Rev 11 1/126

Contents VG6640, VD6640

# **Contents**

| 1 | Ove  | rview .   |                                        | 9  |

|---|------|-----------|----------------------------------------|----|

|   | 1.1  | Interfa   | ices                                   | 10 |

|   | 1.2  | Power     | supplies                               | 10 |

|   | 1.3  | Clock     | and PLL                                | 10 |

|   | 1.4  | Image     | enhancement, status and test features  | 11 |

|   | 1.5  | Extern    | nal frame synchronization              | 11 |

|   | 1.6  |           | integrity                              |    |

|   | 1.7  |           | ence documents                         |    |

|   | 1.8  |           | e of disclaimer (MIPI)                 |    |

| 2 | Sign | ıal, ball | assignment, pad, and wafer description | 14 |

|   | 2.1  | Signal    | description                            | 14 |

| 3 | Fun  | ctional ( | description                            | 19 |

|   | 3.1  |           | g video block                          |    |

|   |      | 3.1.1     | Pixel array                            |    |

|   |      | 3.1.2     | X, Y address                           |    |

|   |      | 3.1.3     | Dual column ADCs                       |    |

|   |      | 3.1.4     | Dual SRAM                              | 21 |

|   |      | 3.1.5     | Power management                       | 22 |

|   |      | 3.1.6     | Multiple exposure HDR pixel            | 22 |

|   | 3.2  | Digital   | video block                            | 22 |

|   |      | 3.2.1     | Three sub-pipes for each pixel         | 23 |

|   |      | 3.2.2     | Statistics gathering                   | 24 |

|   |      | 3.2.3     | Pattern generator                      | 24 |

|   |      | 3.2.4     | HDR rescaling                          | 24 |

|   |      | 3.2.5     | Piecewise linear (PWL) compression     | 24 |

|   |      | 3.2.6     | Status and trailer lines               | 24 |

|   |      | 3.2.7     | ASIL lines                             | 25 |

|   | 3.3  | Device    | e operating modes                      | 25 |

|   |      | 3.3.1     | Power off state                        | 25 |

|   |      | 3.3.2     | Reset state                            | 25 |

|   |      | 3.3.3     | Standby state                          | 26 |

|   |      |           |                                        |    |

VG6640, VD6640 Contents

|   |       | 3.3.4    | Streaming state                                             | 26    |

|---|-------|----------|-------------------------------------------------------------|-------|

| 4 | Cont  | rol inte | rface                                                       | 27    |

|   | 4.1   | Registe  | er formats                                                  | 30    |

|   |       | 4.1.1    | Data alignment within registers                             | 30    |

|   |       | 4.1.2    | Valid register data types                                   |       |

|   | 4.2   | Registe  | er map                                                      | 32    |

|   |       | 4.2.1    | Status registers [0x0000 to 0x0013]                         | 32    |

|   |       | 4.2.2    | Frame format description registers [0x0040 to 0x0055]       | 33    |

|   |       | 4.2.3    | Setup registers [0x0100 to 0x0114]                          |       |

|   |       | 4.2.4    | Integration and gain status registers [0x0200 to 0x0229]    | 36    |

|   |       | 4.2.5    | Video timing registers [0x0300 to 0x0387]                   | 38    |

|   |       | 4.2.6    | System flag registers [0x211D to 0x2121]                    | 40    |

|   |       | 4.2.7    | User interface set 0 registers [0x2124 to 0x2286]           | 42    |

|   |       | 4.2.8    | User interface set 1 registers [0x2287 to 0x23E9]           | 49    |

|   |       | 4.2.9    | Temperature sensor registers [0x2429 to 0x242D]             | 56    |

|   |       | 4.2.10   | Dark cal control registers [0x244D - 0x2470]                | 56    |

|   |       | 4.2.11   | Test pattern registers [0x2475 to 0x2481]                   | 58    |

|   |       | 4.2.12   | Defect map register [0x2483]                                | 58    |

|   |       | 4.2.13   | Gain merge compensation control registers [0x248B - 0x2492] | 59    |

|   |       | 4.2.14   | Output interface control registers [0x249B - 0x24A3]        | 61    |

|   |       | 4.2.15   | Statistics control registers [0x24A6 - 0x24D3               | 62    |

|   |       | 4.2.16   | NVM buffer data registers [0x2A00 to 0x2BFF]                | 64    |

|   |       | 4.2.17   | I2C bus slave address register [0x41A8]                     | 65    |

| 5 | Video | data ii  | nterface                                                    | 66    |

|   | 5.1   | MIPI C   | SI-2 serial data link                                       | 66    |

|   |       | 5.1.1    | Features                                                    | 66    |

|   |       | 5.1.2    | Frame format                                                | 67    |

|   | 5.2   | Paralle  | I ITU data link                                             | 68    |

|   |       | 5.2.1    | Features                                                    | 68    |

|   |       | 5.2.2    | Frame format - hardware synchronization                     | 69    |

| 6 | Video | o timing | J                                                           | 71    |

|   | 6.1   | Progra   | mmable image size                                           | 71    |

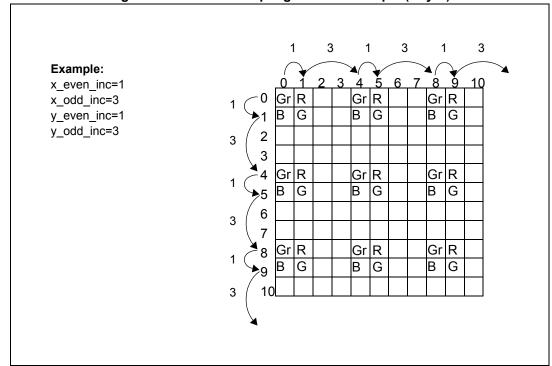

|   | 6.2   | _        | mpled readout mode                                          |       |

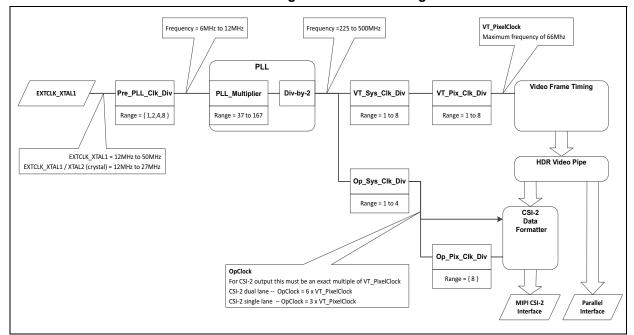

|   | 6.3   |          | al clock to pixel clock relationship                        |       |

|   |       |          | DocID023597 Rev 11                                          | 3/126 |

|    |       | 6.3.1 Spread spectrum                          | 75 |

|----|-------|------------------------------------------------|----|

|    | 6.4   | Variable line length and frame length          | 76 |

| 7  | Vide  | o system                                       | 7  |

|    | 7.1   | Image and video capabilities                   | 77 |

|    | 7.2   | Bayer pattern                                  | 77 |

|    | 7.3   | Exposure and gain control                      | 79 |

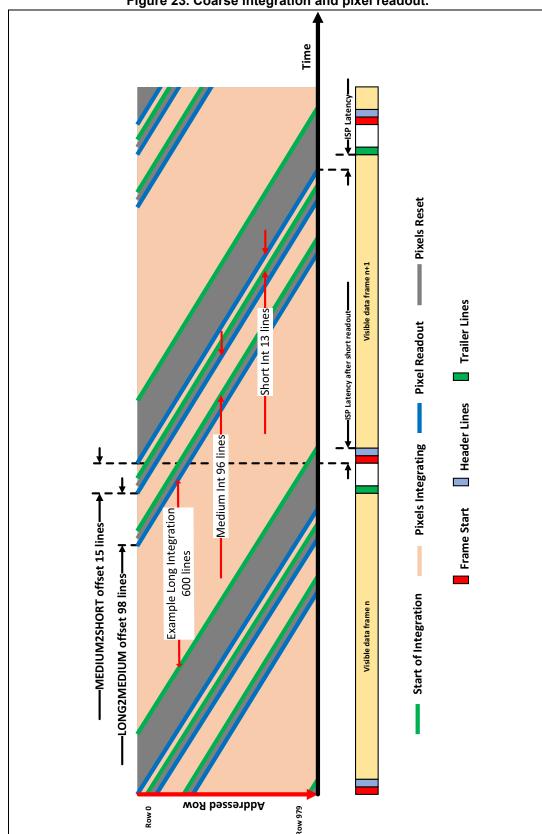

|    |       | 7.3.1 Coarse integration time                  | 79 |

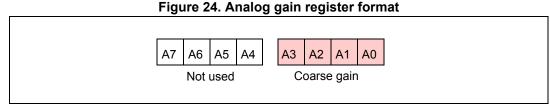

|    |       | 7.3.2 Analog gain model                        | 81 |

|    |       | 7.3.3 Digital gain                             | 82 |

|    |       | 7.3.4 Pixel gain                               | 32 |

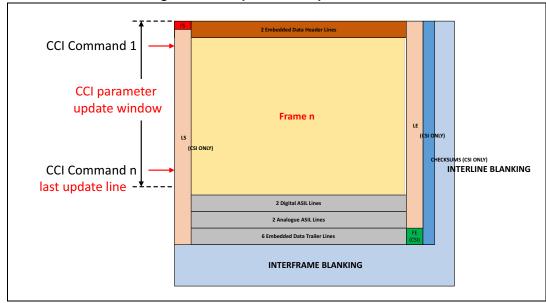

|    |       | 7.3.5 Integration and gain parameter re-timing | 33 |

|    |       | 7.3.6 Grouped register settings                | 33 |

| 8  | Test  | pattern generation                             | 35 |

|    | 8.1   | Standard mode patterns                         | 35 |

|    |       | 8.1.1 100% color bars pattern mode             | 86 |

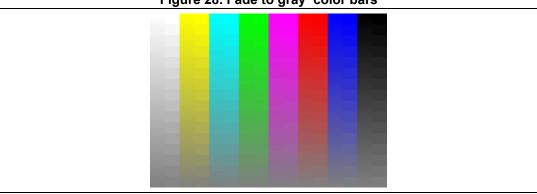

|    |       | 8.1.2 'Fade to gray' color bar mode            | 36 |

| 9  | Elect | rical characteristics 8                        | 37 |

|    | 9.1   | Parameter classification                       | 37 |

|    | 9.2   | Absolute maximum ratings                       | 37 |

|    | 9.3   | Operating conditions                           |    |

|    | 9.4   | Average current consumption 8                  |    |

|    | 9.5   | System clock                                   |    |

|    | 9.6   | Reset input                                    |    |

|    | 9.7   | Digital inputs                                 |    |

|    | 9.8   | Digital outputs                                |    |

|    | 9.9   | I <sup>2</sup> C interface - SDA, SCL          |    |

|    | 9.10  | CSI-2 interface                                |    |

|    | 9.10  | Parallel (ITU) interface                       |    |

|    | J. 11 | i araller (ii o) interiace                     | J  |

| 10 |       | ro-optical characteristics 9                   |    |

|    | 10.1  | Array characteristics                          | )7 |

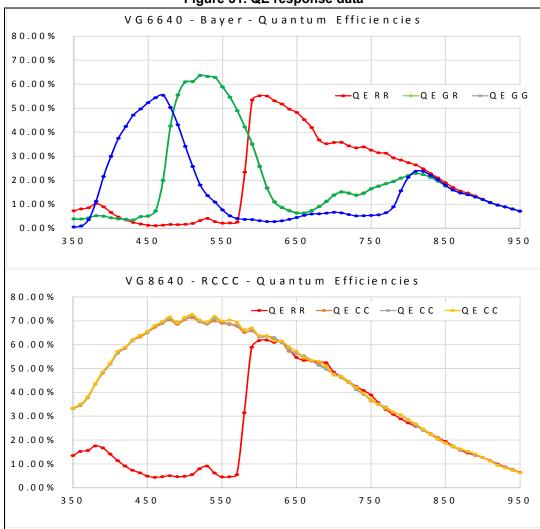

|    | 10.2  | Quantum efficiency                             | 98 |

|    |       |                                                |    |

| 11 | Appl | ication           |                                                 | 99  |

|----|------|-------------------|-------------------------------------------------|-----|

|    | 11.1 | Schem             | natics                                          | 99  |

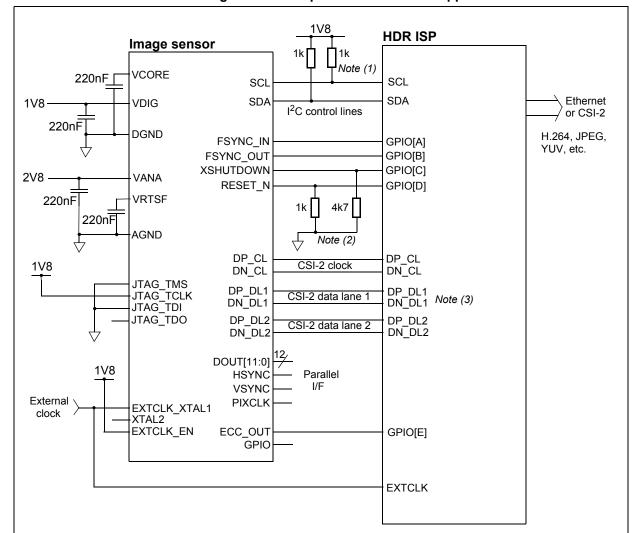

|    |      | 11.1.1            | Example ethernet camera application             | 99  |

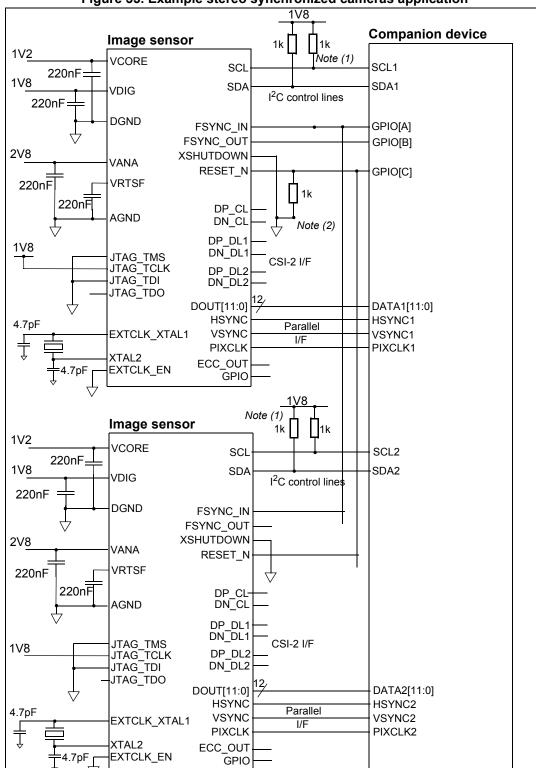

|    |      | 11.1.2            | Example stereo synchronized cameras application | 101 |

|    | 11.2 | PCB la            | yout guidelines                                 | 103 |

|    | 11.3 | Power             | management                                      | 104 |

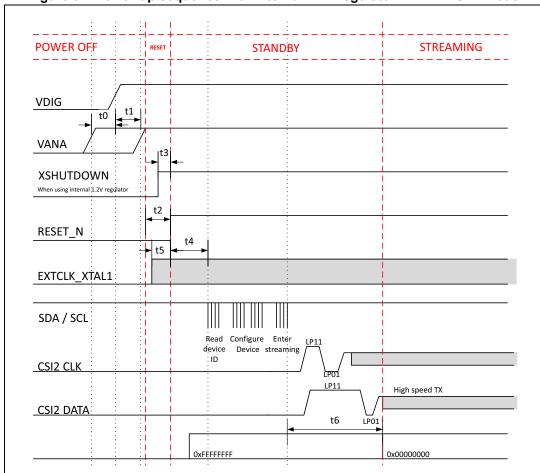

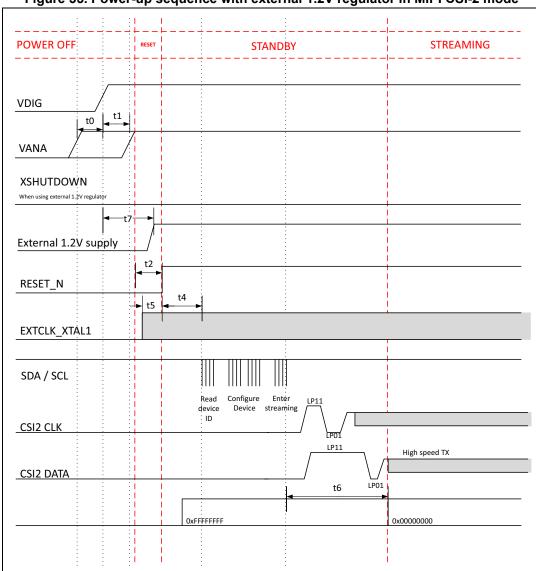

|    |      | 11.3.1            | Power-up procedure                              | 104 |

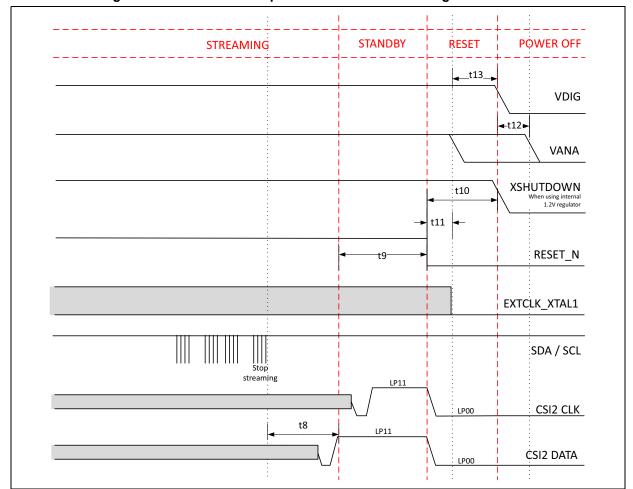

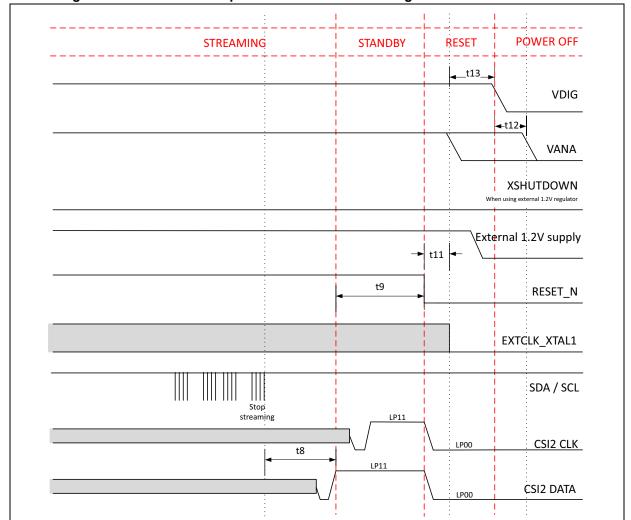

|    |      | 11.3.2            | Power-down procedure                            | 107 |

|    |      | 11.3.3            | Power off conditions                            | 109 |

|    | 11.4 | Externa           | al clock input                                  | 109 |

|    |      | 11.4.1            | Clock source                                    | 110 |

|    |      | 11.4.2            | Quartz crystal                                  | 110 |

|    | 11.5 | I2C pul           | II-up resistors                                 | 111 |

|    | 11.6 | Externa           | al sync input                                   |     |

|    | 11.7 | Error c           | orrecting code (ECC) output                     |     |

| 12 | Non- | volatile          | memory (NVM)                                    | 113 |

| 13 | Pack | age info          | ormation                                        | 114 |

|    | 13.1 | lm2BG             | A package information                           |     |

|    | 13.2 | Im2BG             | A package marking information                   |     |

|    | 13.3 | Deliver           | ry of packaged parts                            |     |

| 14 | Orde | ring inf          | ormation                                        | 117 |

| 15 | Acro | nyms a            | nd abbreviations                                | 118 |

| 16 | ECO  | PACK <sup>®</sup> |                                                 | 120 |

| 17 | Revi | sion his          | story                                           | 121 |

List of tables VG6640, VD6640

# List of tables

| Table 1.  | Device summary                                                         | . 1 |

|-----------|------------------------------------------------------------------------|-----|

| Table 2.  | Technical specifications                                               | . 9 |

| Table 3.  | Reference documents                                                    | 12  |

| Table 4.  | Signal description with Im2BGA 100 balls                               | 14  |

| Table 5.  | Valid register data types                                              | 31  |

| Table 6.  | Status registers [0x0000 to 0x0013]                                    |     |

| Table 7.  | Frame format description registers [0x0040 to 0x0055]                  |     |

| Table 8.  | Setup registers [0x0100 to 0x0114]                                     |     |

| Table 9.  | Integration and gain status registers [0x0200 to 0x0229]               |     |

| Table 10. | Video timing registers [0x0300 to 0x0387]                              |     |

| Table 11. | System flag registers [0x211D to 0x2121]                               |     |

| Table 12. | User interface set 0 Video timing registers [0x2124 to 0x2132]         |     |

| Table 13. | User interface set 0 HDR merge registers [0x2133 to 0x2176]            |     |

| Table 14. | User interface set 0 defect correction registers [0x2177 to 0x217C]    |     |

| Table 15. | User interface set 0 PWL compression registers [0x217D to 0x227D]      |     |

| Table 16. | User interface set 0 statistics control register [0x227E to 0x2286]    |     |

| Table 17. | User interface set 1 integration and gain registers [0x2287 to 0x2295] |     |

| Table 18. | User interface set 1 HDR merge registers [0x2296 to 0x22D9]            |     |

| Table 19. | User interface set 1 defect correction registers [0x22DA to 0x22DF]    |     |

| Table 20. | User interface set 1 PWL registers [0x22E0 to 0x23E0]                  |     |

| Table 21. | User interface set 1 statistics control registers [0x23E1 to 0x23E9]   |     |

| Table 22. | Temperature sensor registers [0x2429 to 0x242D]                        |     |

| Table 23. | Darkcal control register [0x244D - 0x2470]                             |     |

| Table 24. | Test pattern control registers [0x2475 to 0x2481]                      |     |

| Table 25. | Defect map register [0x2483]                                           |     |

| Table 26. | Gain merge compensation control registers [0x248B - 0x2492]            |     |

| Table 27. | Output interface control registers [0x249B - 0x24A3]                   |     |

| Table 28. | Statistics control registers [0x248B - 0x24D3]                         |     |

| Table 29. | NVM buffer data registers [0x2A00 to 0x2BFF]                           |     |

| Table 30. | I2C slave registers[0x41A8]                                            |     |

| Table 31. | CSI-2 short packet data types                                          |     |

| Table 32. | CSI-2 long packet data types                                           |     |

| Table 33. | Typical subsampling settings                                           |     |

| Table 34. | External clock frequency examples, full FOV, 45 fps                    |     |

| Table 35. | Examples of video mode capabilities                                    |     |

| Table 36. | Integration time limits                                                |     |

| Table 37. | Analog gain control                                                    |     |

| Table 38. | Test pattern types                                                     |     |

| Table 39. | Parameter classification                                               |     |

| Table 40. | Absolute maximum ratings                                               |     |

| Table 41. | Operating conditions                                                   |     |

| Table 42. | Typical current consumption in reset and standby                       |     |

| Table 43. | Typical current consumption while streaming                            |     |

| Table 44. | Maximum current consumption while streaming                            |     |

| Table 45. | EXTCLK XTAL1 - characteristics                                         |     |

| Table 46. | System clock - crystal                                                 |     |

| Table 47. | PLL timing characterics                                                |     |

| Table 48. | RESET input - timing characteristics                                   |     |

|           |                                                                        |     |

VG6640, VD6640 List of tables

| Table 49. | Digital input - signal characteristics                     |       |

|-----------|------------------------------------------------------------|-------|

| Table 50. | Digital output - signal characteristics                    | 91    |

| Table 51. | I <sup>2</sup> C interface - signal characteristics        | 92    |

| Table 52. | I <sup>2</sup> C interface - timing characteristics        | 92    |

| Table 53. | CSI-2 interface - high speed mode - signal characteristics | 94    |

| Table 54. | CSI-2 interface - low power mode - signal characteristics  | 94    |

| Table 55. | CSI-2 interface - high speed mode - timing characteristics | 94    |

| Table 56. | CSI-2 interface - low power mode - timing characteristics  | 94    |

| Table 57. | Parallel interface - signal characteristics                |       |

| Table 58. | Parallel interface - timing characteristics                | 95    |

| Table 59. | Electro-optical characteristics                            |       |

| Table 60. | Power-up sequence timing constraints                       | . 104 |

| Table 61. | Power-down sequence timing constraints                     | . 107 |

| Table 62. | Recommended crystal specifications                         |       |

| Table 63. | Ordering information                                       | . 117 |

| Table 64. | Acronyms and abbreviations                                 | . 118 |

| Table 65. | Document revision history                                  |       |

|           |                                                            |       |

List of figures VG6640, VD6640

# **List of figures**

| Figure 1.  | Ball assignment in Im2BGA 100 balls (top view)                      | 16  |

|------------|---------------------------------------------------------------------|-----|

| Figure 2.  | IO ring pad layout                                                  |     |

| Figure 3.  | Wafer description and stack                                         | 18  |

| Figure 4.  | Block diagram                                                       | 19  |

| Figure 5.  | Custom analog block (CAB) block diagram                             | 21  |

| Figure 6.  | Multiple exposure HDR pixel                                         | 22  |

| Figure 7.  | HDR video pipe                                                      | 23  |

| Figure 8.  | System state diagram                                                | 25  |

| Figure 9.  | Data transfer protocol                                              | 27  |

| Figure 10. | I <sup>2</sup> C device address                                     | 28  |

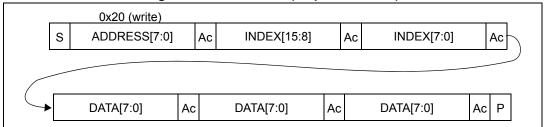

| Figure 11. | Data format (write)                                                 | 28  |

| Figure 12. | Data format (read)                                                  | 28  |

| Figure 13. | Data format (sequential write)                                      | 29  |

| Figure 14. | Data format (sequential read)                                       | 29  |

| Figure 15. | Right alignment for packing 10-bit data into two 8-bit registers    | 30  |

| Figure 16. | CSI-2 frame format                                                  | 67  |

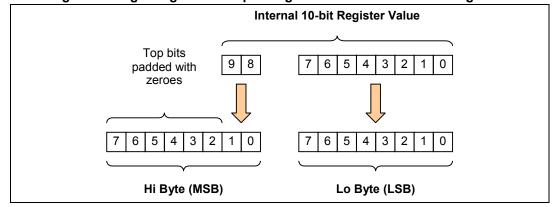

| Figure 17. | Hardware synchronization frame structure                            | 69  |

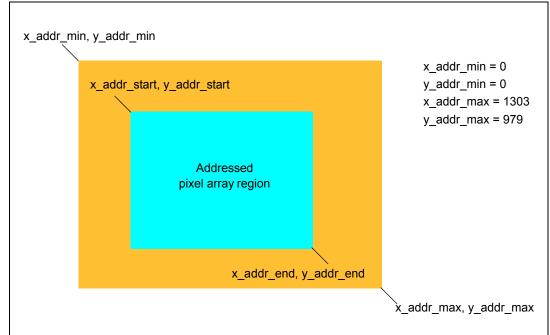

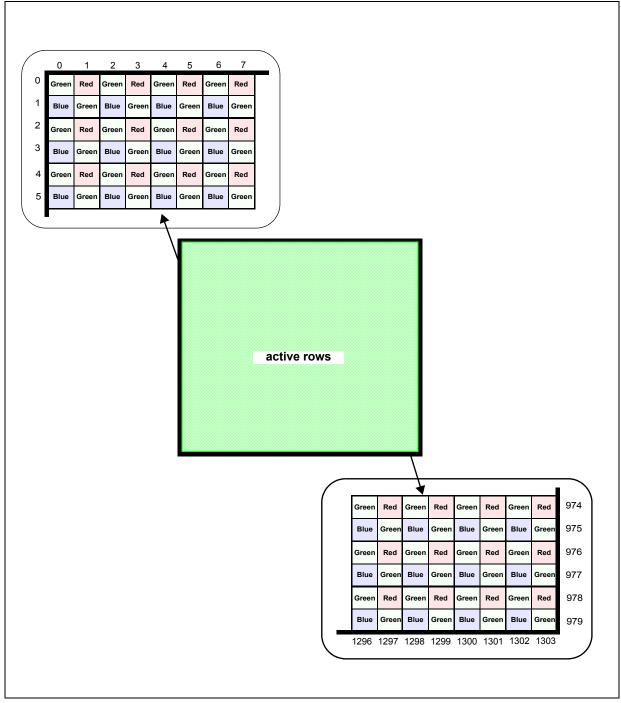

| Figure 18. | Programmable addressable region of the pixel array                  | 72  |

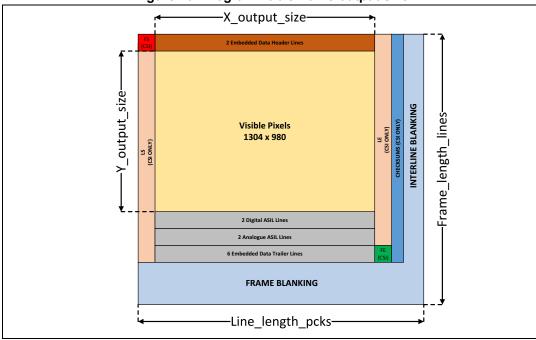

| Figure 19. | Programmable frame output size                                      | 72  |

| Figure 20. | 2 x 2 subsampling readout example (Bayer)                           | 74  |

| Figure 21. | Clock settings                                                      | 75  |

| Figure 22. | Bayer pattern                                                       | 78  |

| Figure 23. | Coarse integration and pixel readout                                | 80  |

| Figure 24. | Analog gain register format                                         | 81  |

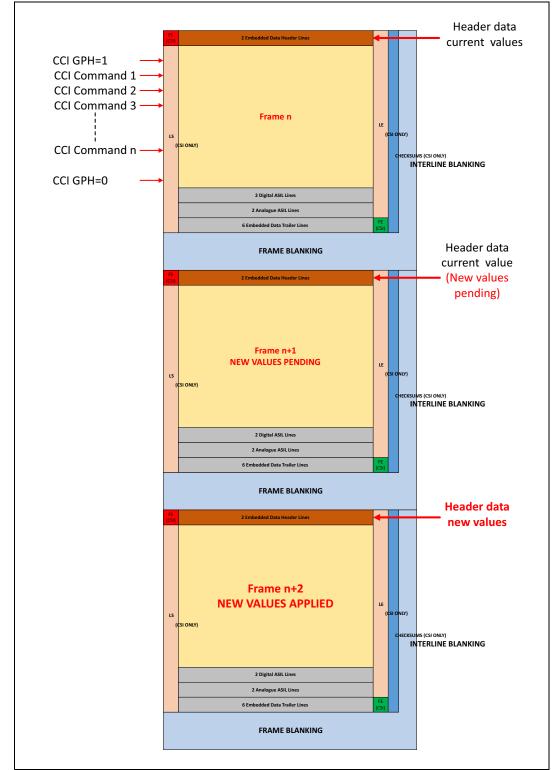

| Figure 25. | CCI parameter update window                                         |     |

| Figure 26. | Control loop synchronisation                                        | 84  |

| Figure 27. | 100% color bars                                                     | 86  |

| Figure 28. | Fade to gray' color bars                                            | 86  |

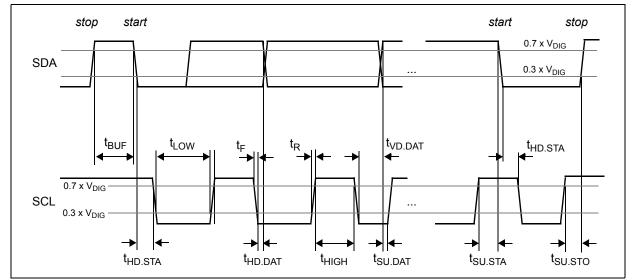

| Figure 29. | I <sup>2</sup> C interface timing                                   |     |

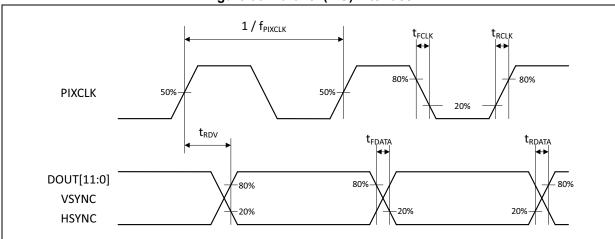

| Figure 30. | Parallel (ITU) interface                                            |     |

| Figure 31. | QE response data                                                    |     |

| Figure 32. | Example ethernet camera application                                 |     |

| Figure 33. | Example stereo synchronized cameras application                     |     |

| Figure 34. | Power-up sequence with internal 1.2V regulator in MIPI CSI-2 mode   |     |

| Figure 35. | Power-up sequence with external 1.2V regulator in MIPI CSI-2 mode   |     |

| Figure 36. | Power-down sequence with internal 1.2V regulator in MIPI CSI-2 mode | 108 |

| Figure 37. | Power-down sequence with external 1.2V regulator in MIPI CSI-2 mode |     |

| Figure 38. | Equivalent model of crystal                                         |     |

| Figure 39. | Im2BGA top view                                                     |     |

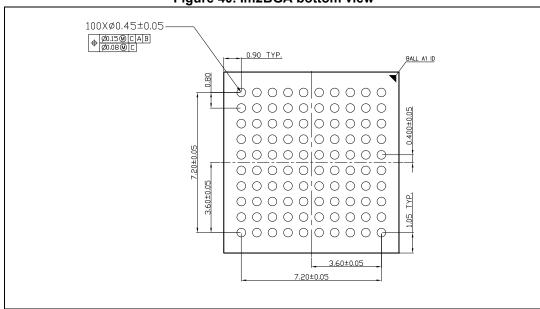

| Figure 40. | Im2BGA bottom view                                                  |     |

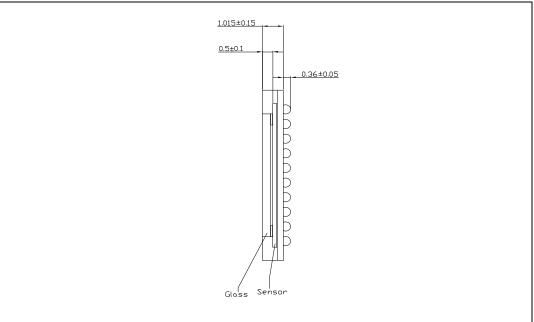

| Figure 41. | Im2BGA side view                                                    |     |

| Figure 42  | Im2BGA nackage marking information                                  | 116 |

VG6640, VD6640 Overview

## 1 Overview

The VG6640, VD6640 are generically referred to in this document as "the image sensor".

**Table 2. Technical specifications**

| Feature                                  | Detail                                                                                                                 |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Pixel resolution                         | 1304 x 980 (to allow 1280 x 960 + 8 border surrounding pixels for ISP processing)                                      |

| Sensor technology                        | 65 nm, CMOS imager process                                                                                             |

| Pixel size                               | 3.75 µm x 3.75 µm                                                                                                      |

| HDR characteristics                      | 3 integration times with real-time data merging                                                                        |

| Shutter                                  | Electrical rolling                                                                                                     |

| Frame rate at full resolution            | 45 fps                                                                                                                 |

| Frame rate at HD video (720p) resolution | 60 fps                                                                                                                 |

| Parallel interface data rate             | 66 Mpixel/s (12 bits per pixel)                                                                                        |

| CSI-2 serial interface data rate         | 2 x 550 Mbit/s                                                                                                         |

| Frame synchronization                    | ±1 line through an I <sup>2</sup> C command or through dedicated signal                                                |

| Package                                  | Exposed glass BGA 9.0 mm x 9.3 mm                                                                                      |

| Maximum recommended CRA <sup>(1)</sup>   | 25°                                                                                                                    |

| Pixel gain                               | +13 dB (x5)                                                                                                            |

| Analog gain                              | +12 dB (maximum)                                                                                                       |

| Supply voltages                          | 2.8V analog supply 1.8V digital I/O supply 1.2V digital core supply (may optionally be generated internally from 1.8V) |

| Power consumption (typical)              | 400mW @ 30 fps                                                                                                         |

| External clock frequency range           | 12-50 MHz, AC or DC coupled                                                                                            |

| Oscillator frequency range               | 12-27 MHz, quartz crystal                                                                                              |

| Junction Temperature range (Tj)          | -40°C to +125°C functional<br>(-40°C to +105°C for acceptable images)                                                  |

| Temperature sensors                      | Two factory calibrated temperature sensors provide ±3°C accuracy over the operating temperature range                  |

Due to the excellent angular response of the VG6640 pixels the microlens array does not require to be optimised for a specific lens CRA. At the quoted maximum CRA of 25 degrees the relative efficiency of the pixels is still greater than 80%.

Note: Further specifications can be found in Chapter 10: Electro-optical characteristics

Overview VG6640, VD6640

## 1.1 Interfaces

The image sensor is ready to connect to the camera enabled companion device. Image data is output from the image sensor over a 12-bit parallel interface or a dual lane MIPI CSI-2 serial interface. Before transmission, the image data is compressed from 22-bit to 12-bit using a compression algorithm that causes no perceptible losses.

The 12-bit parallel interface is capable of 66 Mpixel/s.

The dual lane MIPI CSI-2 serial data interface is capable of 2 x 550 Mbit/s and is the industry standard for low EMI and excellent EMC.

The control interface is I2C in either Fast (up to 400KHz) or Fast+ (up to 1MHz) modes.

## 1.2 Power supplies

Power supplies required:

- 2.8 V for the analog blocks

- 1.8 V for the digital I/Os

- 1.2 V for the digital core

The internal digital core operates from 1.2V. This may optionally be supplied from an external regulator or generated internally from the 1.8V supply by a low drop out regulator included in the image sensor.

#### 1.3 Clock and PLL

An input clock is required which can be supplied as an external clock in the range of 12 MHz to 50 MHz or as an external quartz crystal of 12 MHz to 27 MHz.

The image sensor has an embedded phased locked loop (PLL) block to generate all necessary internal clocks. The PLL can be configured to run at a fixed frequency or with a spread spectrum of up to 30 kHz modulation.

VG6640, VD6640 Overview

## 1.4 Image enhancement, status and test features

The video processor integrates a wide range of image enhancement functions, designed to ensure high image quality. These include:

- real-time exposure merging for High Dynamic Range (HDR) imaging

- comprehensive set of motion and flicker minimising HDR options

- flicker flag to indicate where flickering has been detected within a frame

- digital per-channel gain stage for white balancing

- · external synchronization

- windowing/image cropping

- subsampling

- analog, pixel and digital gain

- dark calibration

- frame crop

- defective pixel correction

- test pattern generation

- statistics generation

- embedded sensor status data (trailer, and header)

## 1.5 External frame synchronization

The external frame synchronization features two modes which can be exploited to synchronize the frame start in multiple-camera systems.

- Where an external frame synchronization signal is available, it can be applied to a

dedicated synchronization ball. The sensor will synchronize its frame start to the edge

of the synchronization signal. Further improvement to the synchronization accuracy

can be achieved by applying a common clock to all cameras.

- Where a frame synchronization signal is not available (remote cameras), an I<sup>2</sup>C register may be set to synchronize the frame start. The sensor will synchronize its frame start to the end of the I<sup>2</sup>C transmission of when the sync register is set.

## 1.6 Safety integrity

A set of self diagnosis features allows the device to support the automotive safety integrity level (ASIL) system requirements:

- ECC (error correction codes) for critical memories

- analog in-line test modes

- digital in-line test readout modes

- dual temperature sensor

- all diagnosis states can be read back from the internal registers and are also embedded in the image status data

Overview VG6640, VD6640

# 1.7 Reference documents

**Table 3. Reference documents**

| Title                                                              | Date              |

|--------------------------------------------------------------------|-------------------|

| MIPI Alliance Specification for D-PHY v1.10.00                     | 7th November 2011 |

| MIPI Alliance Standard for Camera Serial Interface 2 (CSI-2) v1.01 | 9th November 2010 |

| SMIA 1.0 Functional Specification                                  | 06/2004           |

| SMIA 1.0 Characterization Specification Rev A                      | 03/2005           |

| SMIA 1.0 Functional Specification ECR0001 ver 1                    | 02/2005           |

| ITU-R BT.601-7                                                     | 03/2011           |

VG6640, VD6640 Overview

## 1.8 Notice of disclaimer (MIPI)

The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled by any of the authors or developers of this material or MIPI. The material contained herein is provided on an "AS IS" basis and to the maximum extent permitted by applicable law, this material is provided AS IS AND WITH ALL FAULTS, and the authors and developers of this material and MIPI hereby disclaim all other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses, and of lack of negligence.

ALSO, THERE IS NO WARRANTY OF CONDITION OF TITLE, QUIET ENJOYMENT, QUIET POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD TO THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT. IN NO EVENT WILL ANY AUTHOR OR DEVELOPER OF THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT OR MIPI BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL, CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR ANY OTHER AGREEMENT, SPECIFICATION OR DOCUMENT RELATING TO THIS MATERIAL, WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

Without limiting the generality of this Disclaimer stated above, the user of the contents of this Document is further notified that MIPI: (a) does not evaluate, test or verify the accuracy, soundness or credibility of the contents of this Document; (b) does not monitor or enforce compliance with the contents of this Document; and (c) does not certify, test, or in any manner investigate products or services or any claims of compliance with the contents of this Document. The use or implementation of the contents of this Document may involve or require the use of intellectual property rights ("IPR") including (but not limited to) patents, patent applications, or copyrights owned by one or more parties, whether or not Members of MIPI. MIPI does not make any search or investigation for IPR, nor does MIPI require or request the disclosure of any IPR or claims of IPR as respects the contents of this Document or otherwise.

Questions pertaining to this document, or the terms or conditions of its provision, should be addressed to:

MIPI Alliance, Inc., c/o IEEE-ISTO, 445 Hoes Lane, Piscataway, NJ 08854, Attn: Board Secretary.

# 2 Signal, ball assignment, pad, and wafer description

# 2.1 Signal description

Table 4. Signal description with Im2BGA 100 balls

| Pin name               | Type <sup>(1)</sup> | Description                                                                                               | Reset<br>state <sup>(2)</sup> | Reference supply |

|------------------------|---------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------|------------------|

| Power supplies         |                     |                                                                                                           |                               |                  |

| VCORE                  | PWR                 | 1V2 power supply for the digital core (optional, 1V2 may be generated internally using the LDO regulator) |                               | 1.2 V            |

| VDIG                   | PWR                 | 1V8 power supply for the I/O ring (and internal LDO regulator)                                            |                               | 1.8 V            |

| VANA                   | PWR                 | 2V8 power supply for analog blocks                                                                        |                               | 2.8 V            |

| DGND                   | PWR                 | Digital ground                                                                                            |                               | 1.8 V            |

| AGND                   | PWR                 | Analog ground                                                                                             |                               | VANA             |

| Reference              |                     |                                                                                                           |                               |                  |

| VRTSF                  | REF                 | Internal reference. Must be connected by 220nF capacitor to AGND                                          |                               | N/A              |

| Clocks                 |                     |                                                                                                           |                               |                  |

| EXTCLK_XTAL1           | I-SCH               | External clock input, or, crystal oscillator input (dependent on state of EXTCLK_EN pin)                  |                               | N/A              |

| XTAL2                  | 0                   | Crystal oscillator output                                                                                 |                               | N/A              |

| CSI2 interface         |                     |                                                                                                           |                               |                  |

| DP_DL1, DN_DL1         | 0                   | CSI2 data lane 1, positive and negative                                                                   | HI_Z                          | VCORE            |

| DP_DL2, DN_DL2         | 0                   | CSI2 data lane 2, positive and negative                                                                   | HI_Z                          | VCORE            |

| DP_CL, DN_CL           | 0                   | CSI2 clock, positive and negative                                                                         | HI_Z                          | VCORE            |

| Parallel (ITU) interfa | се                  |                                                                                                           |                               |                  |

| DOUT[11:0]             | 0                   | ITU Data lines                                                                                            | LO                            | VDIG             |

| PIXCLK                 | 0                   | ITU Pixel Clock                                                                                           | LO                            | VDIG             |

| HSYNC                  | 0                   | ITU Horizontal Sync                                                                                       | LO                            | VDIG             |

| VSYNC                  | 0                   | ITU Vertical Sync                                                                                         | LO                            | VDIG             |

| Control interface      |                     |                                                                                                           |                               |                  |

| XSHUTDOWN              | I-SCH               | Internal 1V2 LDO enable (HI enables the regulator)                                                        |                               | VDIG             |

| RESET_N                | I-SCH-<br>PU20      | Master reset for digital core                                                                             |                               | VDIG             |

| EXTCLK_EN              | I-PD5               | External clock enable input                                                                               | LO                            | VDIG             |

| SDA                    | I/O                 | I2C-style data                                                                                            |                               | VDIG             |

Table 4. Signal description with Im2BGA 100 balls (continued)

| Pin name       | Type <sup>(1)</sup> | Description                                                        | Reset<br>state <sup>(2)</sup> | Reference supply |

|----------------|---------------------|--------------------------------------------------------------------|-------------------------------|------------------|

| SCL            | I                   | I2C-style clock                                                    |                               | VDIG             |

| FSYNC_IN       | I-PD5               | Frame synchronization input (rising edge)                          | LO                            | VDIG             |

| FSYNC_OUT      | 0                   | Frame synchronization output (start of integration on rising edge) | LO                            | VDIG             |

| ECC_OUT        | 0                   | Flags uncorrectable (double bit) ECC occurrences                   | LO                            | VDIG             |

| GPIO           | I/O                 | General purpose input or output / Flicker Indication               | LO                            | VDIG             |

| Test interface |                     |                                                                    |                               |                  |

| JTAG_TMS       | I-PD5               | Test mode (connect to GND when not in use)                         | LO                            | VDIG             |

| JTAG_TCK       | I-PD5               | Test clock (connect to VDIG when not in use)                       | LO                            | VDIG             |

| JTAG_TDI       | I-PD5               | Test data in (connect to GND when not in use)                      | LO                            | VDIG             |

| JTAG_TDO       | 0                   | Test data out                                                      | LO                            | VDIG             |

| Other pins     | •                   |                                                                    | •                             |                  |

| NC             |                     | Leave unconnected                                                  |                               | N/A              |

<sup>1.</sup> I = Input, O = Output, I/O = Input or output, I-PD5 -= Input with 5K pull-down, I-SCH = Input with Schmitt trigger, I-Sh-PU20 = Input Schmitt with 20k pull-up, REF = Reference, PWR = Power supply or ground

<sup>2.</sup> LO = Digital low level, HI = Digital high level, HI\_Z = High impedance state

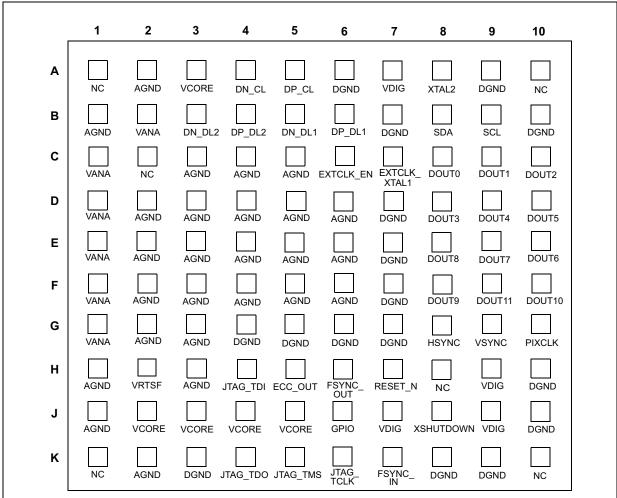

Figure 1. Ball assignment in Im2BGA 100 balls (top view)

57/

DNC = do not connect, the ball must be left unconnected

NC = not connected, the ball is not connected to anything inside the device

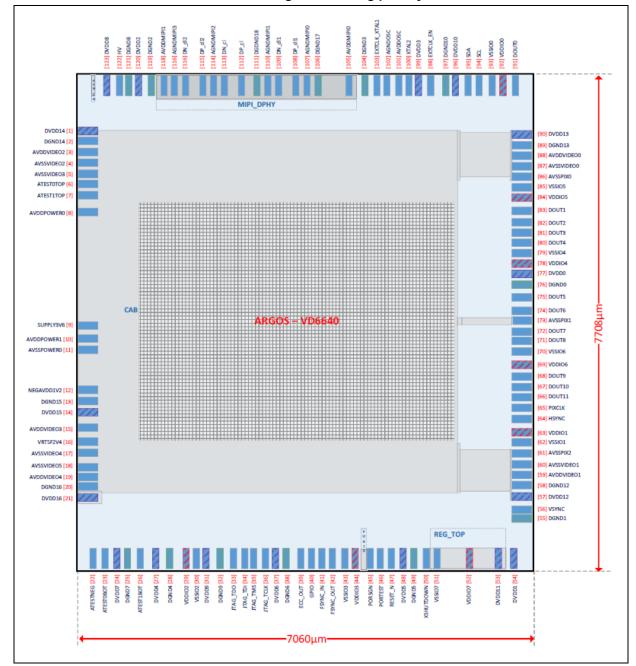

Figure 2. IO ring pad layout

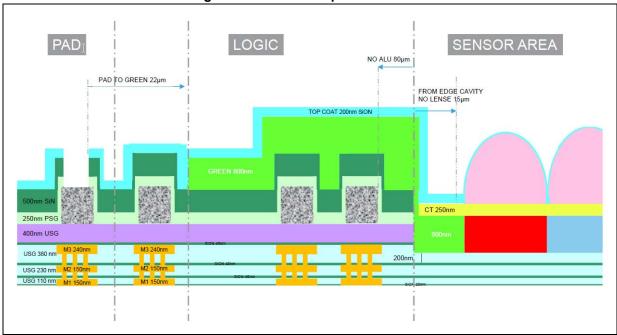

Figure 3. Wafer description and stack

## 3 Functional description

External sync. Power supply Image sensor Video timing 1V2 Temp. Charge sensors pumps Custom analog block (CAB) MIPI **HDR** 1304 x 980 **CSI-2 &** video pipe HDR pixels parallel I/O Companion device Master Clock & I<sup>2</sup>C NVM PLL controller External clock

Figure 4. Block diagram

The image sensor includes the following main functional blocks:

Master controller

Responsible for system operation and sequencing with the following features:

- microcontroller core

- clock and reset management

- I<sup>2</sup>C control interface and control transaction routing

- safe system startup from reset to standby

- system transition from standby to streaming mode

- system streaming soft stop

- device re-initialization to default mode (software reset)

- high dynamic mode setting (management of the integration time settings).

- non-volatile memory (NVM) management

- Custom analog block (CAB)

- Contains the pixel array and the analog components to drive it.

- Video timing block

- Generates digital video timing signals for the CAB with synchronization to an optional external sync signal.

577

- HDR video pipe

- Responsible for real-time image data processing at pixel clock rate. Processes the raw pixel data from the ADCs in the CAB. The HDR video pipe contains a set of correction algorithm blocks and dedicated blocks for data coding.

- Manages the 22bit to12bit compression using a programmable 32 element PWL table.

- Image data transmitters

- Video data coders and transmitters, including serial (MIPI) and parallel interfaces.

- On chip regulators

- Supplies the analog block and the digital core.

- Clock and PLL

- Provides all the clocks required for the video timing.

- Non-volatile memory (NVM)

- Stores production test data and part-to-part variation data for image quality enhancement.

- Temperature sensors

- Allows the application to take decisions based on the sensor temperature.

## 3.1 Analog video block

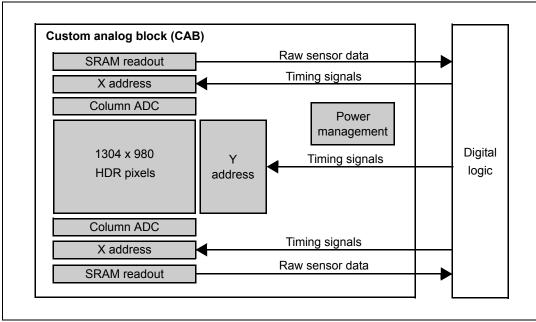

The custom analog block (CAB) includes the following main functional blocks:

- pixel array, see Section 3.1.1

- X, Y address, see Section 3.1.2

- dual column ADCs, see Section 3.1.3

- dual SRAM, see Section 3.1.4

- power management, see Section 3.1.5

- multiple exposure HDR pixel, see Section 3.1.6

577

Figure 5. Custom analog block (CAB) block diagram

## 3.1.1 Pixel array

The pixel array consists of:

- 1304 x 980 visible pixels, each of 3.75 μm x 3.75 μm pixel size

- pixels offer 2 global conversion gain settings with a nominal ratio of

- dark pixels used to calibrate the dark current

- border pixels required by the algorithms in the HDR video pipe

- automotive safety integrity level (ASIL) pixels a synthetic signal source used to generate stimuli for the analog signal chain which can then be verified by the receiver of the image

## 3.1.2 X, Y address

The X and Y addressing blocks address each pixel in the array in turn, to generate video data. Each pixel integrates the incoming light up to three times, in order to increase the dynamic range.

#### 3.1.3 Dual column ADCs

The dual column ADCs digitize the analog pixel signal from the pixel array. Analog gain may be applied to the analog pixel signal before digitization.

#### 3.1.4 Dual SRAM

The dual SRAM stores the pixel values for two integration times until the pixel values for the third integration time becomes available.

577

DocID023597 Rev 11

21/126

## 3.1.5 Power management

The power management block provides the necessary supplies to the CAB and improves the power supply rejection ratio (PSRR).

## 3.1.6 Multiple exposure HDR pixel

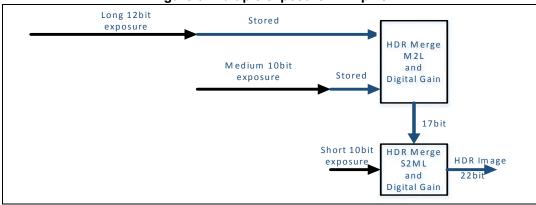

The high dynamic range (HDR) image data is constructed by combination of three exposures (integration time) for each pixel. A long exposure captures details in the dark parts of the scene, whilst a short exposure captures details in the bright parts. A mid-length exposure captures all mid-range details.

Figure 6. Multiple exposure HDR pixel

During pixel data collection, the long exposure is made first and stored in SRAM. Then the medium exposure is made Finally, the short exposure is made and once all the data is collected, the three exposures are intelligently merged to create one high dynamic range pixel value.

## 3.2 Digital video block

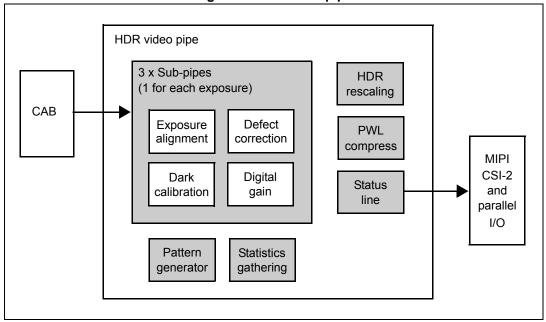

The HDR video pipe includes the following main functional blocks:

- three sub-pipes, one for each pixel exposure, see Section 3.2.1

- statistics gathering, see Section 3.2.2

- pattern generator, see Section 3.2.3

- HDR rescaling, see Section 3.2.4

- piece-wise linear (PWL) compression, see Section 3.2.5

- status line and trailer, see Section 3.2.6

- defect correction supporting RAW Bayer and Monochrome color masks.

57

Figure 7. HDR video pipe

## 3.2.1 Three sub-pipes for each pixel

Each sub-pipe contains the following blocks, operating on each exposure of the image:

Dark calibration

An algorithm that estimates the dark current for each pixel and each pixel exposure. The estimated dark current value is then subtracted from each pixel exposure value in order to accurately render the image.

Exposure alignment

Line memories that store the intermediate long and medium exposure time values until the short integration time value of the same pixel is available.

Defect correction

An algorithm to correct defective pixels. This can be configured to manage RAW Bayer or monochrome color masks. Single or couplet defective pixels may be removed dynamically. Couplet defective pixels may be mapped out and removed using data from the non-volatile memory (NVM). Up to 32 pixels may be mapped out.

Digital gain

In combination with the analog gain, a higher system gain can be achieved. The digital gain can also be used to compensate for the coarse step size of the analog gain, as the digital gain has a much finer step size. This allows further white balance and exposure corrections to be made by the companion device.

57/

## 3.2.2 Statistics gathering

The statistics gathering block collects and collates pixel values for use by exposure and white balance algorithms. The average pixel value and variance are generated for up to 48 zones (across the full field of view).

Histogram data can be collected over a maximum of four regions of interest (ROIs), and over any or all of the color planes. Each histogram has a resolution of 64 bins, each bin is 16-bits.

#### 3.2.3 Pattern generator

The pattern generator block generates a test pattern that can be used to test the entire HDR video pipe. The following patterns are available:

- color bars (plain and fade to 50%)

- grayscale (horizontal, vertical and diagonal)

- solid colors

- test cursors with programmable positions

- pseudo-random data

- HDR ramp

## 3.2.4 HDR rescaling

The HDR rescaling algorithm merges the three exposures for each pixel. Exposure correction factors are calculated and applied to compensate for non-linearities. The merge algorithm options ensure that true colors are preserved and flicker and ghost artifacts are minimized.

#### 3.2.5 Piecewise linear (PWL) compression

The PWL block contains a logarithmic type compression algorithm to reduce the data bit-depth transmitted and avoid excessive bandwidth requirements. The PWL compression algorithm is loss-less in the sense that any losses in image quality are below the noise floor of the image. This is implemented using a 32 point curve resulting in an improved SNR performance, reduced quantization noise and a more natural image.

#### 3.2.6 Status and trailer lines

The status and trailer lines include frame-by-frame metadata such as:

- product identification

- configuration status

- image statistics including histograms

- frame counter

The data in the status and data lines is encoded using the SMIA embedded line tagging mechanism. This mechanism allows the data to be decoded in a generic way. For example, data tags allow both the I<sup>2</sup>C index and the value of each register included in the status and trailer lines to be decoded.

Refer to SMIA 1.0 Part 1: Functional Specification, section 4.9 Embedded Data Line Formats for further details.

57

#### 3.2.7 **ASIL lines**

ASIL data lines follow the trailer data lines in the frame format. They including analog and digital test data that allows comprehensive system monitoring and fault detection.

#### **Device operating modes** 3.3

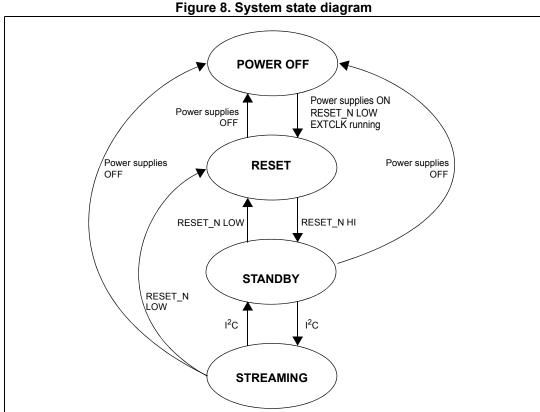

The mode changes in the image sensor are shown in Figure 8.

#### 3.3.1 Power off state

Power supplies are off.

#### 3.3.2 **Reset state**

All blocks are powered and in a state of reset. I<sup>2</sup>C communications are not supported in this mode. All registers are returned to their default values. EXTCLK should be provided to the sensor in this mode.

## 3.3.3 Standby state

Standby state preserves the contents of the register settings. I<sup>2</sup>C communications are supported in this mode. The internal video timing is reset to the start of a video frame in preparation for the enabling of active video. The previous settings of exposure and gain are preserved. The system clock must remain active when communicating with the image sensor.

If the MIPI CSI-2 interface is in use then the state of the bus in Standby depends on whether the previous state was Reset or Streaming. If the previous state was Reset then all MIPI CSI2 data lines remain at high impedance. If the previous state was Streaming then the MIPI CSI2 data lines go to LP11 state while in Standby state.

Standby state is entered from reset by setting RESET\_N high, or from streaming by writing to the mode\_select register; or by commanding a software reset by writing to the software reset register.

Note:

After a software reset or the transition of RESET\_N to high, all registers are returned to their default values.

#### 3.3.4 Streaming state

Streaming state allows live video data to be streamed to the output. Streaming mode is entered by writing to the mode\_select register.

57/

VG6640, VD6640 Control interface

## 4 Control interface

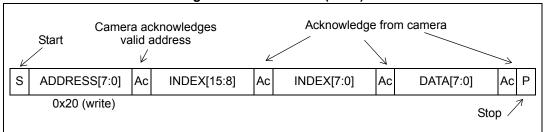

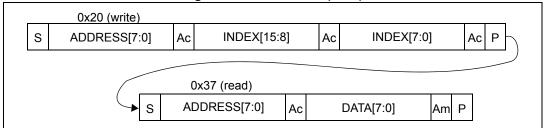

Control and status data is transferred to and from the image sensor using the control interface. The internal registers in the image sensor can be configured or read back by a companion device containing an I<sup>2</sup>C master (SDA, SCL). Commands are in the format specified by the control interface in the MIPI CSI-2 specification (16-bit index followed by 8-bit data).

The control interface is an I<sup>2</sup>C-type interface with two signals: serial data line (SDA) and serial clock line (SCL). Each device connected to the bus uses a unique address and a simple master/slave relationships exists.

Note: Technically, the control interface serial bus is a protocol and subset of the  $l^2C$  standard. For brevity, this datasheet will refer to the control interface as  $l^2C$ .

By default the image sensor operates in I<sup>2</sup>C Fast mode (up to 400kHz). For operation in Fast+ mode (up to 1MHz), this must be enabled by setting the relevant register.

Note: Operation in Fast+ mode requires a change in value of pull-up resistor to ensure fast enough rise time of the signals (see Section 11.5: I2C pull-up resistors).

Both SDA and SCL lines are connected to a positive supply voltage using pull-up resistors located externally or on the companion device. Lines are only actively driven low. A high condition occurs when lines are floating and the pull-up resistors pull lines up. When no data is transmitted both lines are high. See Chapter 9: Electrical characteristics on page 87 for electrical and timing information.

Clock signal (SCL) generation is performed by the master device. The master device initiates data transfer. The I<sup>2</sup>C bus on the image sensor uses a default device address of 0x20. This slave address is held in register 0x41A8 as detailed in the register map.

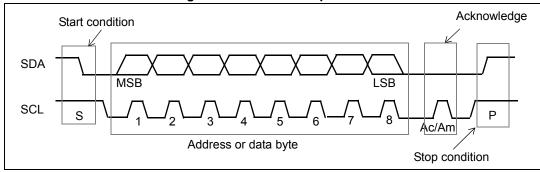

Figure 9. Data transfer protocol

Information is packed in 8-bit packets (bytes) always followed by an acknowledge bit, Ac for camera acknowledge and Am for master acknowledge. The internal data is produced by sampling SDA at a rising edge of SCL. The external data must be stable during the high period of SCL. The exceptions to this are start (S) or stop (P) conditions when SDA falls or rises respectively, while SCL is high.

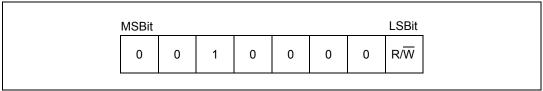

A message contains a series of bytes preceded by a start condition and followed by either a stop or repeated start (another start condition but without a preceding stop condition) followed by another message. The first byte contains the device address (0x20 by default) and also specifies the data direction. If the least significant bit (lsb) is low (that is, 0x20) the

Control interface VG6640, VD6640

message is a master write to the slave. If the lsb is set (that is, 0x21) then the message is a master read from the slave.

Figure 10. I<sup>2</sup>C device address

All serial interface communications with the sensor must begin with a start condition. The sensor acknowledges the receipt of a valid address by driving the SDA wire low. The state of the read/write bit (lsb of the address byte) is stored and the next byte of data, sampled from SDA, can be interpreted. During a write sequence the second and third bytes received provide a 16-bit index which points to one of the internal 8-bit registers.

Figure 11. Data format (write)

As data is received by the slave it is written bit by bit to a serial/parallel register. After each data byte has been received by the slave, an acknowledge is generated, the data is then stored in the internal register addressed by the current index.

During a read message, the contents of the register addressed by the current index is read out in the byte following the device address byte. The contents of this register are parallel loaded into the serial/parallel register and clocked out of the device by the falling edge of SCL.

Figure 12. Data format (read)

At the end of each byte, in both read and write message sequences, an acknowledge is issued by the receiving device (that is, the image sensor for a write and the baseband for a read).

A message can only be terminated by the bus master, either by issuing a stop condition or by a negative acknowledge (that is, **not** pulling the SDA line low) after reading a complete byte during a read operation.

VG6640, VD6640 Control interface

The interface also supports auto-increment indexing. After the first data byte has been transferred, the index is automatically incremented by 1. The master can therefore send data bytes continuously to the slave until the slave fails to provide an acknowledge or the master terminates the write communication with a stop condition. If the auto-increment feature is used the master does **not** have to send address indexes to accompany the data bytes.

Figure 13. Data format (sequential write)

Figure 14. Data format (sequential read)

Further details of the control interface protocol can be found in the MIPI Alliance Standard for Camera Serial Interface 2 (CSI-2).

Control interface VG6640, VD6640

## 4.1 Register formats

Any internal register that can be written to, can also be read from. There are also read only registers that contain device status information, for example, design revision details.

A read instruction from an unused register location returns the value 0x00. A read instruction from a reserved address may return any value.

A write instruction to a reserved or unused register location is illegal and the effect of such a write is undefined.

A read or write to an unused register location must not cause the I<sup>2</sup>C read or write message to be aborted. Therefore an I<sup>2</sup>C read or write message to an unused register location must complete in the same way as if the read or write message had addressed a used register location.

It is the responsibility of the companion device to only write to register locations which have been defined.

Note that some registers marked as Read Only (RO) or Do Not Write (DNW) can be written to and may read back with the data written but may also have unpredictable effects on the operation of the sensor.

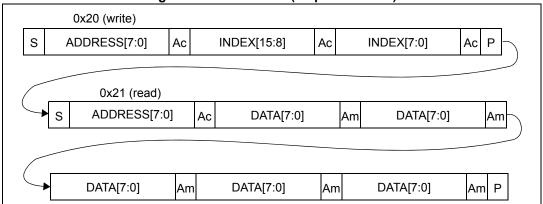

## 4.1.1 Data alignment within registers

Registers that are larger than 8 bits long are stored most significant byte first, i.e the MSB is placed in the location with the lowest index.

If the width of an internal register is narrower than the 8-bit, 16-bit or 32-bit register which reports it's value, then the register value is right aligned within the register and the unused MS bits are padded with zeroes.

Figure 15. Right alignment for packing 10-bit data into two 8-bit registers

VG6640, VD6640 Control interface

## 4.1.2 Valid register data types

The contents of the registers can represent a number of different data types (see *Table 5*). The register map uses this coding to help with the interpretation of the contents of each register.

Table 5. Valid register data types

| Data<br>type | Name                                  | Range                       | Description                                                                             |

|--------------|---------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------|

| 8UI          | 8-bit unsigned integer                | 0 to 255                    | -                                                                                       |

| 8SI          | 8-bit signed integer                  | -128 to 127                 | Two's complement notation                                                               |

| 16UI         | 16-bit unsigned integer               | 0 to 65535                  | -                                                                                       |

| 16SI         | 16-bit signed integer                 | -32768 to 32767             | Two's complement notation                                                               |

| 16UR         | 16-bit unsigned iReal                 | 0 to<br>255.99609375        | 08.08 fixed point number. 8 integer bits (MS Byte), 8 fractional bits (LS Byte)         |

| 16SR         | 16-bit signed iReal                   | -128 to<br>127.9960375      | Two's complement notation, 8 fractional bits                                            |

| 32UR         | 32-bit unsigned iReal                 | 0 to<br>65535.99998474      | 16.16 fixed point number. 16 integer bits (MS 2 Bytes), 16 fractional bits (LS 2 Bytes) |

| 32SR         | 32-bit signed iReal                   | -32768 to<br>32767.99998474 | Two's complement notation,16 fractional bits                                            |

| 32SF         | 32-bit IEEE floating-<br>point number | As per IEEE 754             | As per IEEE 754. 1 sign bit, 8 exponent bits, 23 fractional bits                        |

| 8C or<br>16C | 8-bit or 16-bit Coded                 | -                           | This indicates that the value is decoded to select one of several functions or modes.   |

| 8B or<br>16B | 8 or 16 bits                          | -                           | Each bit represents a specific function or mode.                                        |

Control interface VG6640, VD6640

# 4.2 Register map

User should write only to the register addresses defined in this document. Writes to other addresses may cause the VG6640 to operate incorrectly.

## 4.2.1 Status registers [0x0000 to 0x0013]

Table 6. Status registers [0x0000 to 0x0013]

| Index  | Byte | Register name         | Data<br>type | Default | Туре  | Comment                                                                                                                                                                                                                   |

|--------|------|-----------------------|--------------|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000 | HI   | -Sensor_Model_ID      | 16UI         | 0x02    | DNW   | Sensor model identification number.                                                                                                                                                                                       |

| 0x0001 | LO   |                       |              | 0x80    |       |                                                                                                                                                                                                                           |

| 0x0002 |      | Revision_Number_Major | 8UR          | 0x20    | DNW   | Revision identifier of the camera.  Default value depends on NVM content. 4.4                                                                                                                                             |

| 0x0006 |      | Pixel_Order           | 8UI          | 0x00    | DNW   | Color pixel readout order. Changes according to mirror and flip (register 0x0101).  0x00 - GR/BG normal.  0x01 - RG/GB horizontal mirror.  0x02 - BG/GR vertical flip.  0x03 - GB/RG vertical flip and horizontal mirror. |

| 0x0008 | HI   | Data Pedestal         | 16UI         | 0x00    | DNW   | Data pedestal being applied to the LongX4 data.                                                                                                                                                                           |

| 0x0009 | LO   | - Data_Pedestal       |              | 0x00    |       |                                                                                                                                                                                                                           |

| 0x0010 | HI   | - Frame_Count         | 32UI         | 0xFF    | - DNW | Increments by 1 every time a frame is streamed. Reports 0xFFFFFFFF when sensor is idle or after a soft reset. Rolls over at 0xFFFFFFE to 0x00000001.                                                                      |

| 0x0011 |      |                       |              | 0xFF    |       |                                                                                                                                                                                                                           |

| 0x0012 |      |                       |              | 0xFF    |       |                                                                                                                                                                                                                           |

| 0x0013 | LO   |                       |              | 0xFF    |       |                                                                                                                                                                                                                           |

VG6640, VD6640 Control interface

## 4.2.2 Frame format description registers [0x0040 to 0x0055]

Table 7. Frame format description registers [0x0040 to 0x0055]

| Index  | Byte | Register name                  | Data<br>type | Default | Туре   | Comment                                                                                                                                                                     |

|--------|------|--------------------------------|--------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0040 |      | Frame_Format_Model<br>_Type    | 8UI          | 0x01    | DNW    | Generic frame format  0x01 = 2 byte data format  0x02 = 4 byte data format                                                                                                  |

| 0x0041 |      | Frame_Format_Model_<br>Subtype | 8UI          | 0x15    | DNW    | Contains the number of 2-byte data format descriptors used The upper nibble defines the number of column descriptors The lower nibble defines the number of row descriptors |

| 0x0042 | HI   | Frame_Format                   |              | 0x55    |        | X output size                                                                                                                                                               |

| 0x0043 | LO   | _Descriptor_0                  | 16UI         | 0x18    | DNW    | [15:12] - Pixel code<br>[11:0] - X size (default 1304)                                                                                                                      |

| 0x0044 | HI   | Frame_Format                   |              | 0x10    |        | 2 embedded data header lines                                                                                                                                                |

| 0x0045 | LO   | _Descriptor_1                  | 16UI         | 0x02    | DNW    | [15:12] - Pixel code<br>[11:0] - number of data header lines                                                                                                                |

| 0x0046 | HI   | Frame_Format                   | 16UI         | 0x53    | DNW    | Y output size                                                                                                                                                               |

| 0x0047 | LO   | _Descriptor_2                  |              | 0xD4    |        | [15:12] - Pixel code<br>[11:0] - Y size (default 980)                                                                                                                       |

| 0x0048 | HI   | Frame_Format                   | 16UI         | 0x80    | DNW    | 2 digital ASIL lines                                                                                                                                                        |

| 0x0049 | LO   | _Descriptor_3                  |              | 0x02    |        | [15:12] - Pixel code<br>[11:0] - number of ASIL lines                                                                                                                       |

| 0x004A | HI   | Frame_Format                   | 16UI         | 0x90    | DNW    | 2 analog ASIL lines                                                                                                                                                         |

| 0x004B | LO   | _Descriptor_4                  |              | 0x02    |        | [15:12] - Pixel code<br>[11:0] - number of ASIL lines                                                                                                                       |

| 0x004C | HI   | Frame_Format                   |              | 0xA0    |        | 6 embedded data trailer lines                                                                                                                                               |

| 0x004D | LO   | <br>_Descriptor_5              | 16UI         | 0x06    | DNW    | [15:12] - Pixel code<br>[11:0] - number of data lines                                                                                                                       |

| 0x004E | HI   | Frame_Format                   | 16UI         | 0x00    | DNW    | unused descriptor                                                                                                                                                           |

| 0x004F | LO   | _Descriptor_6                  | 1001         | 0x00    | DINVV  | unused descriptor                                                                                                                                                           |

| 0x0050 | HI   | Frame_Format<br>_Descriptor_7  | 16UI         | 0x00    | DNW    | unused descriptor                                                                                                                                                           |

| 0x0051 | LO   |                                |              | 0x00    | DIVV   |                                                                                                                                                                             |

| 0x0052 | HI   | Frame_Format<br>_Descriptor_8  | 16UI         | 0x00    | DNW    | unused descriptor                                                                                                                                                           |

| 0x0053 | LO   |                                |              | 0x00    |        |                                                                                                                                                                             |

| 0x0054 | HI   | Frame_Format                   | 16UI         | 0x00    | DNW    | unused descriptor                                                                                                                                                           |

| 0x0055 | LO   | _Descriptor_9                  |              | 0x00    | J. 177 | anaoca acoonptor                                                                                                                                                            |

VG6640, VD6640 **Control interface**

#### 4.2.3 Setup registers [0x0100 to 0x0114]

Table 8. Setup registers [0x0100 to 0x0114]

| Index  | Byte | Register name          | Data<br>type | Default | Туре | Comment                                                                                                                                                                                           |

|--------|------|------------------------|--------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0100 |      | Mode_Select            | 8UI          | 0x00    | RW   | [7] - External sync mode: 0x0 - Master mode 0x1 - Slave mode [6] - Slave mode type: 0x0 - External pin slave mode 0x1 - I2C command slave mode [0] - Mode select: 0x00 = Standby 0x01 = Streaming |

| 0x0101 |      | Image_Orientation      | 8UI          | 0x00    | RW   | [7:2] - Reserved [1:0] - Image orientation:  0x0 = Normal  0x1 = Flip in X  0x2 = Flip in Y  0x3 = Flip in X and flip in Y                                                                        |

| 0x0103 |      | Software_Reset         | 8UI          | 0x00    | RW   | Software reset returns the sensor to its power-on defaults  0x00 = Normal operation  0x01 = Software reset enabled  The value of this register is automatically reset to 0x00                     |

| 0x0104 |      | Grouped_Parameter_Hold | 8UI          | 0x00    | RW   | The grouped parameter hold register disables the consumption of integration, gain and video timing parameters  0x00 = Consume values as normal 0x01 = Do not consume values                       |

| 0x0111 |      | Signalling_Mode        | 8UI          | 0x02    | RW   | Determines which transmission signalling mode is to be used $0x02 = CSI2$ output only $0x80 = Parallel/ITU$ output only $0x82 = CSI2$ and parallel/ITU output together                            |

34/126 DocID023597 Rev 11

Downloaded from Arrow.com.

VG6640, VD6640 Control interface

Table 8. Setup registers [0x0100 to 0x0114] (continued)

| Index  | Byte | Register name | Data<br>type | Default | Туре | Comment                                                                                                                  |

|--------|------|---------------|--------------|---------|------|--------------------------------------------------------------------------------------------------------------------------|

| 0x0112 | НІ   | - Data_Format | 16UI         | 0x16    | - RW | The value of this register contains the bit-depth of the uncompressed pixel data. The only valid value is 0x16 (22-bit). |

| 0x0113 | LO   |               |              | 0x0C    |      | The value of this register contains the bit-depth of the compressed pixel data. The only valid value is 0x0C (12-bit).   |

| 0x0114 |      | CSI_Lane_Mode | 8UI          | 0x01    | RW   | The number of CSI2 data lanes in use.  0x00 = 1-lane.  0x01 = 2-lane.                                                    |

Control interface VG6640, VD6640

## 4.2.4 Integration and gain status registers [0x0200 to 0x0229]

Table 9. Integration and gain status registers [0x0200 to 0x0229]

| Index  | Byte | Register name                             | Data<br>type | Default | Туре      | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|------|-------------------------------------------|--------------|---------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|