# L9945

# Automotive fully configurable 8-channel High/Low side MOSFET pre-driver suitable for 12 V and 24 V systems

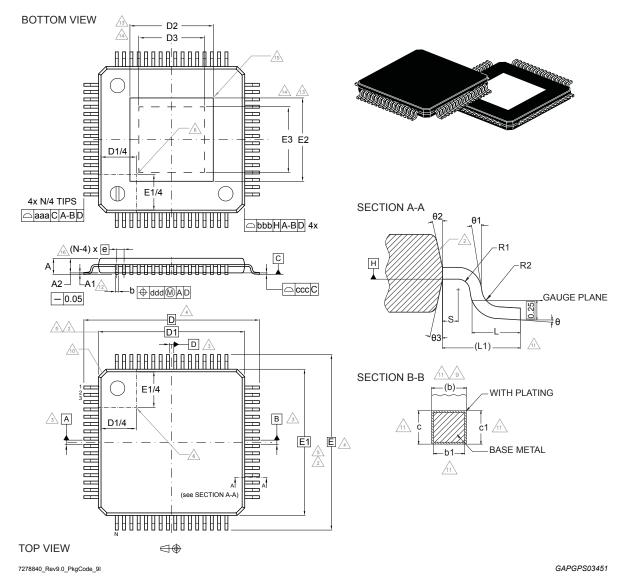

TQFP64 exposed pad down

# Features

- 12 V and 24 V battery systems compliance

- 3.3 V and 5 V logic compatible I/O

- 8-channel configurable MOSFET pre-driver

- High-side (N-channel and P-channel MOS)

- Low-side (N-channel MOS)

- H-bridge (up to 2 H-bridge)

- Peak & Hold (2 loads)

- Operating battery supply voltage 3.8 V to 36 V

- Operating VDD supply voltage 4.5 V to 5.5 V

- All device pins, except the ground pins, withstand at least 40 V

- Programmable gate charge/discharge currents for improving EMI behavior

- Individual diagnosis for:

- Short circuit to battery

- Open load

- Short circuit to ground

- Highly flexible overcurrent sensing implementation

- Possibility of monitoring external MOS drain to source voltage

- Possibility of monitoring voltage on external shunt resistor

- 64 programmable overcurrent thresholds independent for each channel

- Ultra-fast output shutdown in case of overcurrent

- Current limitation for H-Bridge configuration

- 32-bit SPI protocol available for configuration and diagnostics

- Failures latched even if they occur during diagnostics reading

- Daisy chain operation

- SDO protected against overvoltage

- Safety features

- Fast switch off redundant output disable through two external pins

- Built In Self Test (BIST) for logic operation

- Hardware Self Check (HWSC) for VDD5 overvoltage comparator

- Configurable Communication Check (CC) watchdog timer available

- Disable feedback through bi-directional pin

- Highly redundant output monitoring through dedicated SPI registers

- 10-bit ADC for battery and die temperature measurements available through SPI

- VDD5 monitoring for over/under voltage

- VPS (battery) monitoring for under voltage

| Prod       | luct status lin    | k             |

|------------|--------------------|---------------|

|            | L9945              |               |

| Pro        | duct summary       | /             |

| Order code | Package            | Packing       |

| L9945      | TQFP64             | Tray          |

| L9945TR    | (exposed pad down) | Tape and reel |

# **Description**

The L9945 is an 8-channel MOSFET pre-driver configurable for low-side, high-side, peak and hold and H-Bridge load control. It is designed to comply with the requirements of 12 V (passenger vehicle) and 24 V (commercial vehicle) battery systems.

All outputs can be PWM controlled. Six outputs are capable of driving safety relevant loads. One output can be dedicated to the actuation of safety relevant loads requiring a dedicated enable pin (EN6).

The device offers the possibility of controlling two independent H-Bridges.

The device can also drive up to two loads requiring "peak & hold" control strategy.

The driver outputs are protected against short circuit condition.

The device protects the external MOS in case of an overcurrent event.

Each output provides full diagnostic information such as short to battery, short to ground and open-load. Each output status can be constantly monitored through dedicated SPI registers.

The voltage slew rate of the external transistors 1-8 is controlled during turn ON and turn OFF in order to improve EMI behavior.

A double, redundant, external disable source is available through DIS and NDIS pins in order to improve safety.

The device is configurable via SPI through a 32-bit protocol.

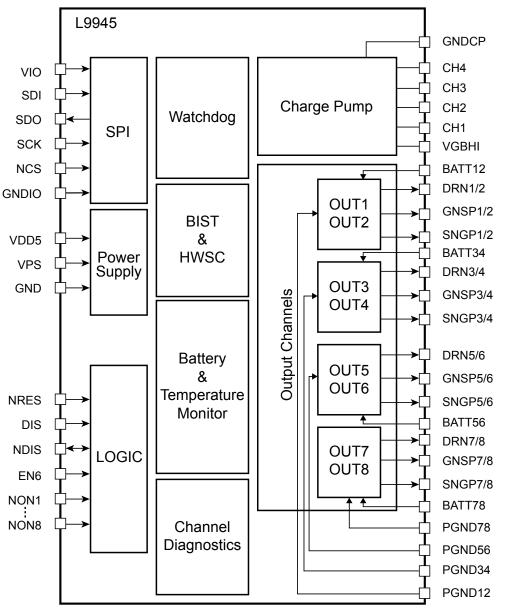

# 1 Block diagram

57

#### Figure 1. Block diagram

GADG2302170914PS

# 2 Applications

The device offers three different configuration options for the output channels: High-Side/Low-Side, Peak & Hold and H-Bridge. P&H configuration requires 2 or 4 channels, while H-Bridge requires 4 or 8 channels. Channels not used in P&H or H-Bridge are available for HS/LS usage. All the configurations involving channel 6 require the output driver 6 to be enabled through the EN6 input.

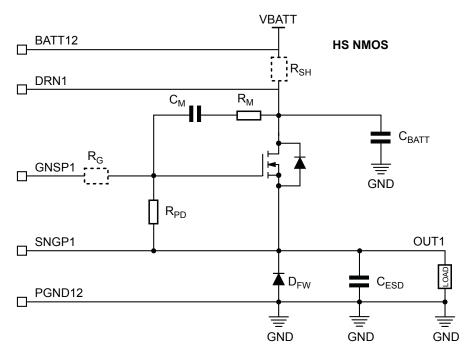

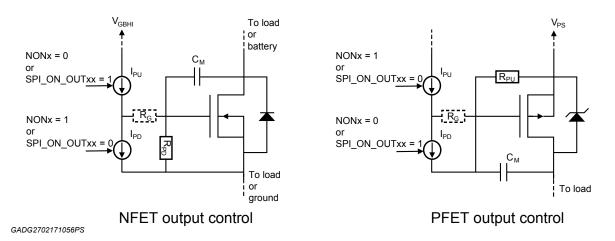

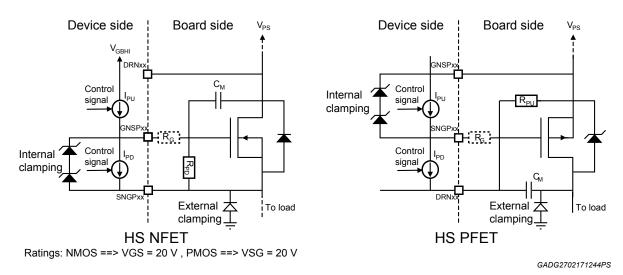

## **2.1** High-Side / Low-Side, with configurable FET type (N channel or P channel)

Each channel features a dedicated SPI register where the user can specify:

- MOS side: High-Side or Low-Side, through the LS\_HS\_config\_xx bit;

- MOS type: NMOS or PMOS, through the N\_P\_config\_xx bit;

- PMOS type is available only for High-Side.

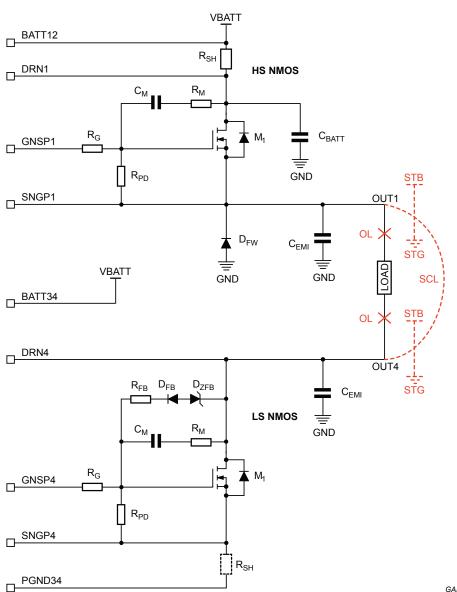

The picture below shows an example of High-Side configuration with NMOS transistor on channel 1. Refer to this schematic in order to understand how the external FET must be mounted with respect to the DRNx/GNSPx/SNGPx/BATTx pins.

#### Figure 2. Example of High-Side configuration with NMOS on channel 1

Note: the freewheeling diode is needed only in case of inductive load.

GADG2302171549PS

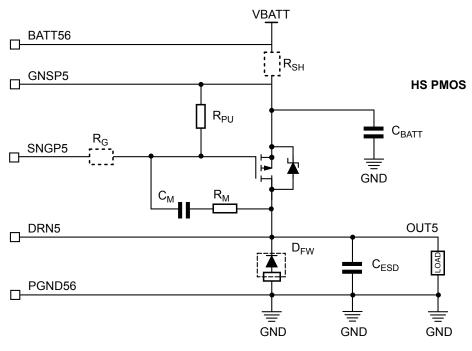

The following picture shows an example of High-Side configuration with PMOS transistor on channel 5. Refer to this schematic in order to understand how the external FET must be mounted with respect to the DRNx/GNSPx/SNGPx/BATTx pins.

#### Figure 3. Example of High-Side configuration with PMOS on channel 5

Note: the freewheeling diode is needed only in case of inductive load.

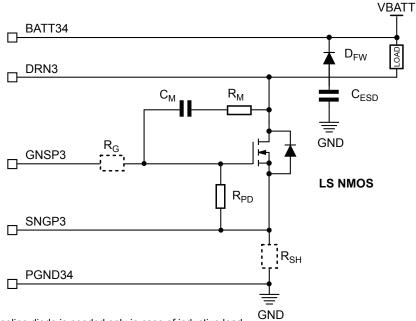

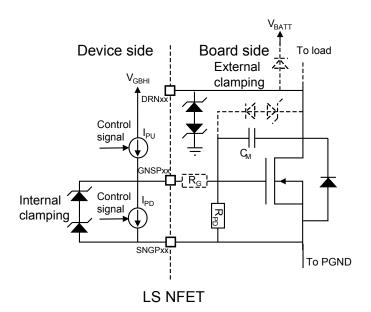

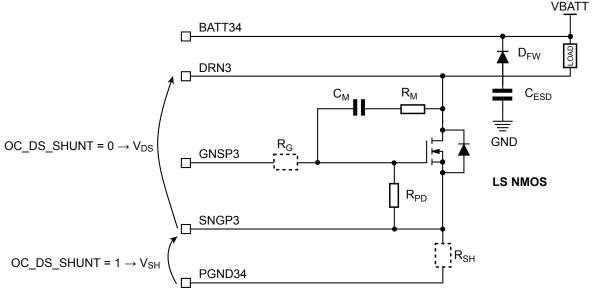

The picture below shows an example of Low-Side configuration with NMOS transistor on channel 3. Refer to this schematic in order to understand how the external FET must be mounted with respect to the DRNx/GNSPx/SNGPx/PGNDx pins.

#### Figure 4. Example of Low-Side configuration with NMOS on channel 3

Note: the freewheeling diode is needed only in case of inductive load.

GADG2302170929PS

GADG2302171301PS

Note: When using channel 6, the EN6 input must be set high to enable the output driver.

- The LS/HS configuration is suitable for driving whatever high-side/low-side loads as:

- Lamps (any channel);

- ON/OFF electrovalves (any channel);

- Any safety relevant load (channel 6 has dedicated EN6 enable input);

- Lambda probe heater (any channel);

- Limp home functionalities or not safety related loads (channels 7 and 8 not affected by external disable input).

### 2.2 Peak & Hold

The device can handle up to two peak & hold loads. There are two possible configurations which can co-exist:

- P&H1: it involves channels 1 (HS) and 4 (LS) and can be selected through the PH1\_config bit

- P&H2: it involves channels 2 (HS) and 3 (LS) and can be selected through the PH2\_config bit

Once a peak & hold configuration is selected through its config bit, the corresponding output channels are automatically configured according to the pre-determined transistor side. The FET type for the High-Side can be selected through its **N\_P\_config\_xx** bit.

#### Figure 5. Example of peak & hold configuration with NMOS (HS) on channel 1 and NMOS (LS) on channel

GADG2402171042PS

Figure 5 shows an example of P&H1 configuration with NMOS transistor on the High-Side. Refer to this schematic in order to understand how the external FETs must be mounted with respect to the DRNx/GNSPx/SNGPx/PGNDx/BATTx pins.

In case of PMOS on the High-Side, refer to Figure 3 in order to understand the DRNx/GNSPx/SNGPx/BATTx pin connection.

The peak and hold configuration is suitable for driving several types of loads as:

- Injectors;

- Fuel pump;

- Other type of electrovalves and coils that may benefit from peak and hold control.

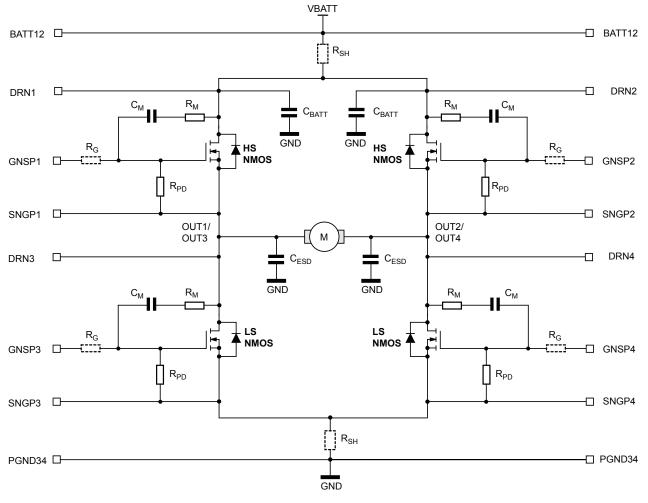

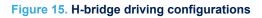

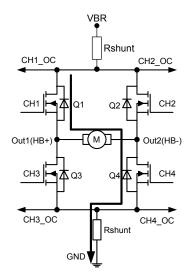

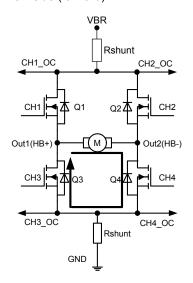

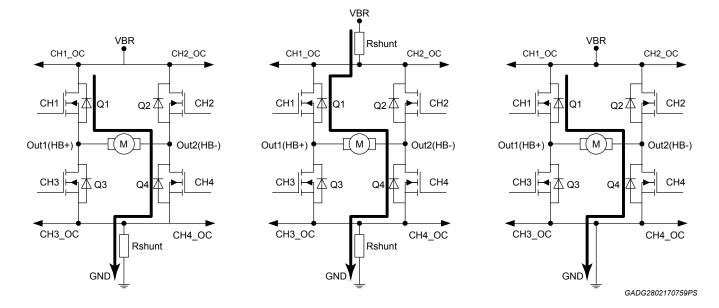

## 2.3 H-Bridge

The device can handle up to two H-Bridges. There are two possible configurations which can co-exist:

- H-Bridge 1: it involves channels 1 (HS), 2 (HS), 3 (LS) and 4 (LS) and can be selected through the **HB1\_config** bit

- H-Bridge 2: it involves channels 5 (HS), 6 (HS), 7 (LS) and 8 (LS) and can be selected through the HB2\_config bit

Once an H-Bridge configuration is selected through its config bit, the corresponding output channels are automatically configured as reported above. The FET type for the High-Side transistors can be selected through their **N\_P\_config\_xx** bit.

In case of H-bridge with PMOS on the High-Side, refer to Figure 3 in order to understand how DRNx/GNSPx/ SNGPx/BATTx are mounted with respect to NMOS pin connection.

The H-Bridge configuration is suitable for driving the following types of loads:

Brushed DC motors

Note: When configuring H-Bridge 2, the EN6 input must be set high to enable the output driver.

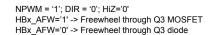

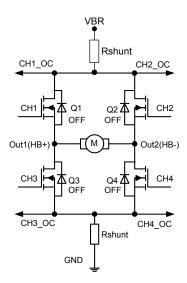

#### Figure 6. Example of H-Bridge configuration with NMOS as HS and LS transistors (channels 1-4 used)

GADG2402171049PS

# 3 Device pins

This section contains the device pinout, the pin description and configuration and the electrical characteristics.

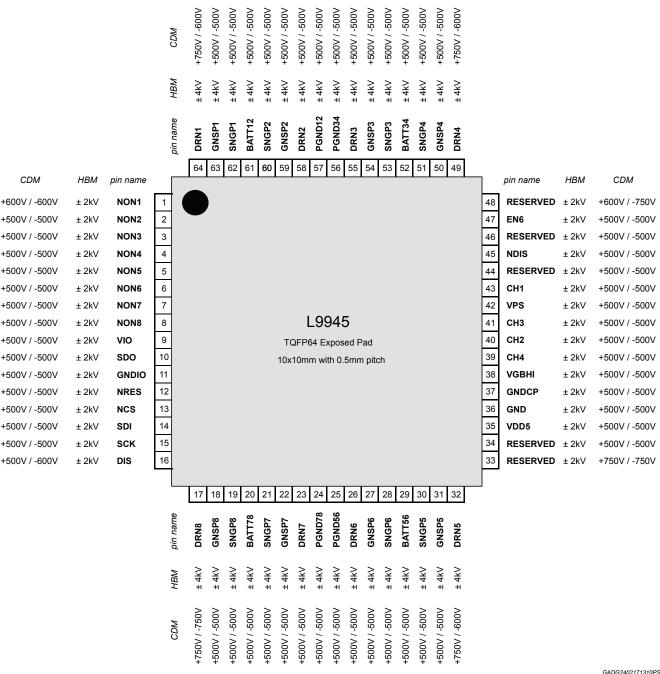

### 3.1 Pinout

The picture below shows the device pinout. Each pin features also the absolute maximum ratings. All pins, except the ground ones, can withstand at least 40 V to GND.

Maximum differential voltage allowed across the following pins is 20 V:

- GNSPx and SNGPx;

- CH2 and VPS;

- CH4 and CH2;

- VGBHI and VPS;

- VGBHI and CH4.

#### Figure 7. L9945 pinout

| negative positive | 60V  | 80V   | 60V   | 60V    | 60V   | 80V   | 60V  | 0.3V   | 0.3V   | 60V  | 80V   | 60V   | 60V    | 60V   | 80V   | 60V  |

|-------------------|------|-------|-------|--------|-------|-------|------|--------|--------|------|-------|-------|--------|-------|-------|------|

| negativ           | -20V | -14V  | -14V  | -1     | -14V  | -14V  | -20V | VE.0-  | VE.0-  | -20V | -14V  | -14V  | -1     | -14V  | -14V  | -20V |

| pin name          | DRN1 | GNSP1 | SNGP1 | BATT12 | SNGP2 | GNSP2 | DRN2 | PGND12 | PGND34 | DRN3 | GNSP3 | SNGP3 | BATT34 | SNGP4 | GNSP4 | DRN4 |

|                   | 64   | 63    | 62    | 61     | 60    | 59    | 58   | 57     | 56     | 55   | 54    | 53    | 52     | 51    | 50    | 49   |

positive negative pin name

| -0.3V | NON1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -0.3V | NON2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -0.3V | NON3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -0.3V | NON4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -0.3V | NON5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -0.3V | NON6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -0.3V | NON7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -0.3V | NON8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -0.3V | VIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -0.3V | SDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -0.3V | GNDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -0.3V | NRES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -0.3V | NCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -0.3V | SDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -0.3V | SCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -0.3V | DIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | -0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0.3V<br>-0 | -0.3V         NON2           -0.3V         NON3           -0.3V         NON4           -0.3V         NON5           -0.3V         NON6           -0.3V         NON7           -0.3V         NON8           -0.3V         SD0           -0.3V         GNDIO           -0.3V         SD0           -0.3V         SD0           -0.3V         SD0           -0.3V         SD0           -0.3V         SD0           -0.3V         SD0           -0.3V         SD1           -0.3V         SD1           -0.3V         SD1           -0.3V         SD1           -0.3V         SD1 |

positive negative pin name

|     | 0045  |  |

|-----|-------|--|

| – L | .9945 |  |

TQFP64 Exposed Pad

| 10x10mm with 0.5mm pitch |

|--------------------------|

|--------------------------|

| 46 | RESERVED | -0.3V | 60V  |

|----|----------|-------|------|

| 45 | NDIS     | -0.3V | 40V  |

| 44 | RESERVED | -0.3V | 60V  |

| 43 | CH1      | -0.3V | 60V  |

| 42 | VPS      | -1V   | 60V  |

| 41 | СНЗ      | -0.3V | 60V  |

| 40 | CH2      | -0.3V | 80V  |

| 39 | CH4      | -0.3V | 80V  |

| 38 | VGBHI    | -0.3V | 80V  |

| 37 | GNDCP    | -0.3V | 0.3V |

| 36 | GND      | -0.3V | 0.3V |

| 35 | VDD5     | -0.3V | 40V  |

| 34 | RESERVED | -0.3V | 60V  |

| 33 | RESERVED | -0.3V | 60V  |

negative positive

60V

40V

-0.3V

-0.3V

pin name

EN6

48 RESERVED

47

| 17   | 18    | 19    | 20     | 21    | 22    | 23   | 24     | 25     | 26   | 27    | 28    | 29     | 30    | 31    | 32   |

|------|-------|-------|--------|-------|-------|------|--------|--------|------|-------|-------|--------|-------|-------|------|

| DRN8 | GNSP8 | SNGP8 | BATT78 | SNGP7 | GNSP7 | DRN7 | PGND78 | PGND56 | DRN6 | GNSP6 | SNGP6 | BATT56 | SNGP5 | GNSP5 | DRN5 |

| -20V | -14V  | -14V  | -1V    | -14V  | -14V  | -20V | -0.3V  | -0.3V  | -20V | -14V  | -14V  | -1V    | -14V  | -14V  | -20V |

| 60V  | 80V   | 60V   | 60V    | 60V   | 80V   | 60V  | 0.3V   | 0.3V   | 60V  | X08   | 60V   | 60V    | 60V   | 80V   | 60V  |

GAPG0802160930CFT

Note:

# 3.2 Pin names and functions

The table below lists all the information about device pins.

The package exposed pad must be soldered on the PCB and connected to ground. Pins GNDIO and GNDCP must be shorted and ground connected.

Syntax: P = Power, G = Ground, D = Digital, A = Analog, I = Input, O = Output, NA = Not Available, L = Low, H = High, PU = Pull Up, PD = Pull Down.

| Pin #  | Pin Name       | Pin   | type   | PU/PD    | Active State  | HBM ESD <sup>(1)</sup> | Description                                      |

|--------|----------------|-------|--------|----------|---------------|------------------------|--------------------------------------------------|

| Power  | r Supply And   | Grou  | und    |          |               |                        |                                                  |

| 42     | VPS            | Р     | NA     | NA       | NA            | 4 kV                   | Battery Input, used to supply charge pump        |

| 36     | GND            | G     | NA     | NA       | NA            | 2 kV                   | Ground                                           |

| 35     | VDD5           | Р     | NA     | NA       | NA            | 2 kV                   | 5 V Input (usually output of external regulator) |

| Digita | l inputs (conr | necte | d to e | external | microcontroll | er)                    |                                                  |

| 1      | NON1           | D     |        | PU       | L             | 2 kV                   | Output 1 ON-OFF signal                           |

|        | NONT           | D     | 1      | FU       | L             | 2 KV                   | NPWM signal for H-Bridge 1                       |

| 2      | NON2           | D     | 1      | PU       | L             | 2 kV                   | Output 2 ON-OFF signal                           |

|        | NONZ           |       |        | 10       | L             | 2 10                   | DIR signal for H-Bridge 1                        |

| 3      | NON3           | D     |        | PU       | L             | 2 kV                   | Output 3 ON-OFF signal                           |

|        |                |       |        |          | _             |                        | HIZ signal for H-Bridge 1                        |

| 4      | NON4           | D     | Ι      | PU       | L             | 2 kV                   | Output 4 ON-OFF signal                           |

| 5      | NON5           | D     |        | PU       | L             | 2 kV                   | Output 5 ON-OFF signal                           |

|        |                |       |        |          | _             |                        | NPWM signal for H-Bridge 2                       |

| 6      | NON6           | D     | 1      | PU       | L             | 2 kV                   | Output 6 ON-OFF signal                           |

|        |                |       |        |          |               |                        | DIR signal for H-Bridge 2                        |

| 7      | NON7           | D     | I      | PU       | L             | 2 kV                   | Output 7 ON-OFF signal                           |

|        |                |       |        |          |               |                        | HIZ signal for H-Bridge 2                        |

| 8      | NON8           | D     | I      | PU       | L             | 2 kV                   | Output 8 ON-OFF signal                           |

|        | t pre-driver   |       |        | 1        |               |                        |                                                  |

| 64     | DRN1           | A     | I      | NA       | NA            | 4 kV                   | FET drain on channel 1                           |

| 63     | GNSP1          | A     | 0      | NA       | NA            | 4 kV                   | NFET gate / PFET source on channel 1             |

| 62     | SNGP1          | Α     | 0      | NA       | NA            | 4 kV                   | NFET source / PFET gate on channel 1             |

| 61     | BATT12         | Р     | I      | NA       | NA            | 4 kV                   | Battery for channels 1 and 2                     |

| 57     | PGND12         | G     | I      | NA       | NA            | 4 kV                   | Power ground for channels 1 and 2                |

| 58     | DRN2           | Α     | I      | NA       | NA            | 4 kV                   | FET drain on channel 2                           |

| 59     | GNSP2          | Α     | 0      | NA       | NA            | 4 kV                   | NFET gate / PFET source on channel 2             |

| 60     | SNGP2          | Α     | 0      | NA       | NA            | 4 kV                   | NFET source / PFET gate on channel 2             |

| 55     | DRN3           | Α     | I      | NA       | NA            | 4 kV                   | FET drain on channel 3                           |

| 54     | GNSP3          | Α     | 0      | NA       | NA            | 4 kV                   | NFET gate / PFET source on channel 3             |

| 53     | SNGP3          | А     | 0      | NA       | NA            | 4 kV                   | NFET source / PFET gate on channel 3             |

| 52     | BATT34         | Р     | I      | NA       | NA            | 4 kV                   | Battery for channels 3 and 4                     |

| 56     | PGND34         | G     | Ι      | NA       | NA            | 4 kV                   | Power ground for channels 3 and 4                |

# Table 1. Pin list

| 49         DRN4         A         I         NA         NA         4 kV         FET drain on channel 4           50         GNSP4         A         O         NA         NA         4 kV         NFET gate / PFET source on channel 4           51         SNGP4         A         O         NA         NA         4 kV         NFET source / PFET gate on channel 4           32         DRN5         A         I         NA         NA         4 kV         NFET gate / PFET gate on channel 5           31         GNSP5         A         O         NA         NA         4 kV         NFET gate / PFET gate on channel 5           30         SNGP5         A         O         NA         NA         4 kV         NET gate / PFET gate on channel 5           29         BATT56         P         I         NA         NA         4 kV         Power ground for channels 5 and 6           26         DRN6         A         I         NA         NA         4 kV         NET gate / PET source on channel 6           27         GNSP6         A         O         NA         NA         4 kV         NFET gate / PET source on channel 6           23         DRN7         A         I         NA         A kV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

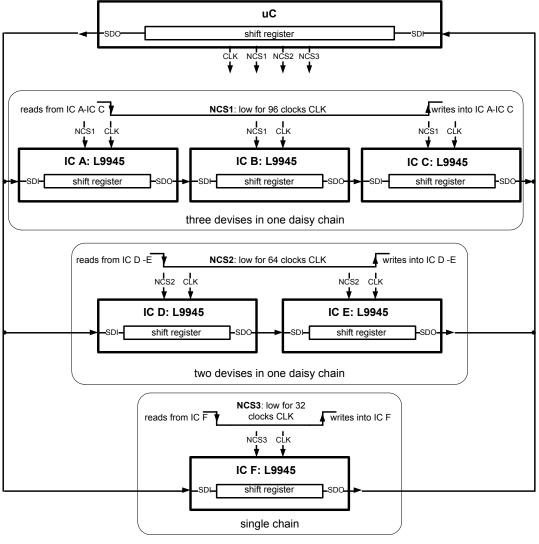

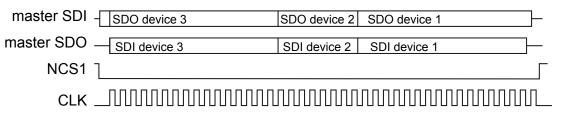

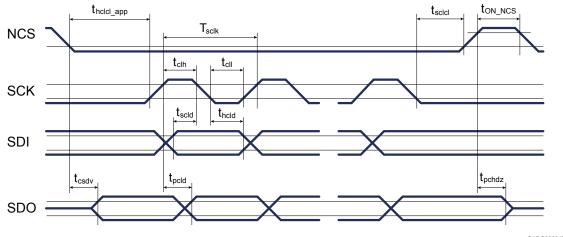

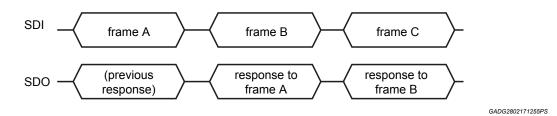

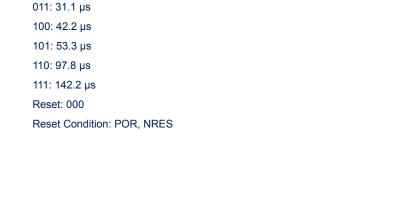

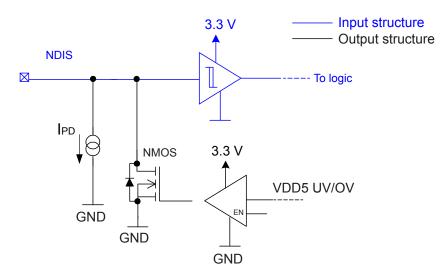

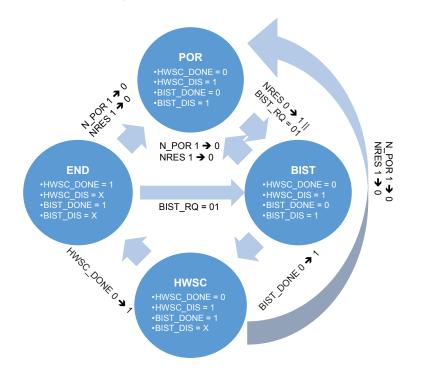

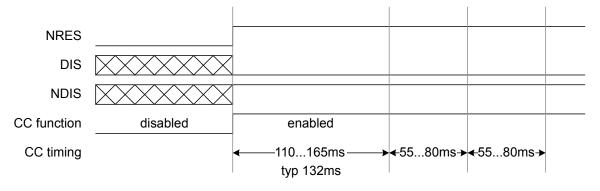

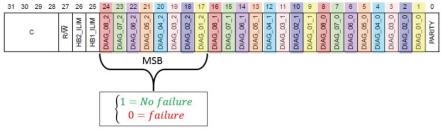

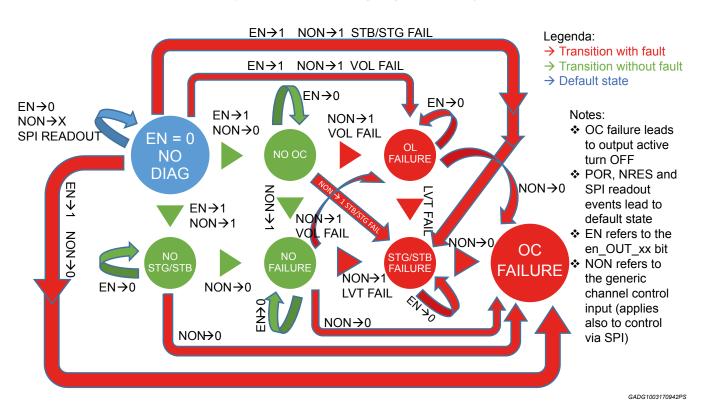

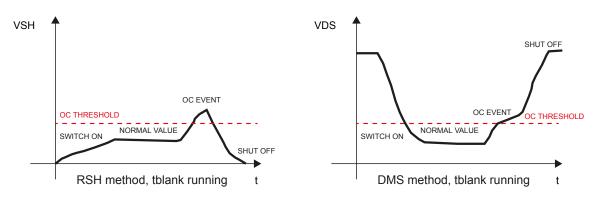

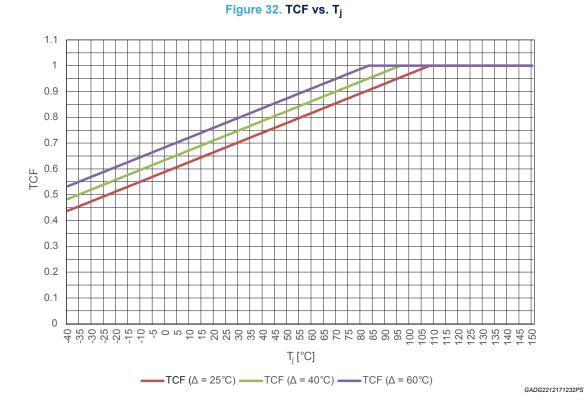

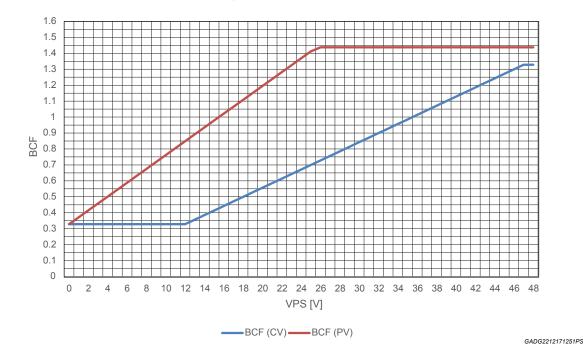

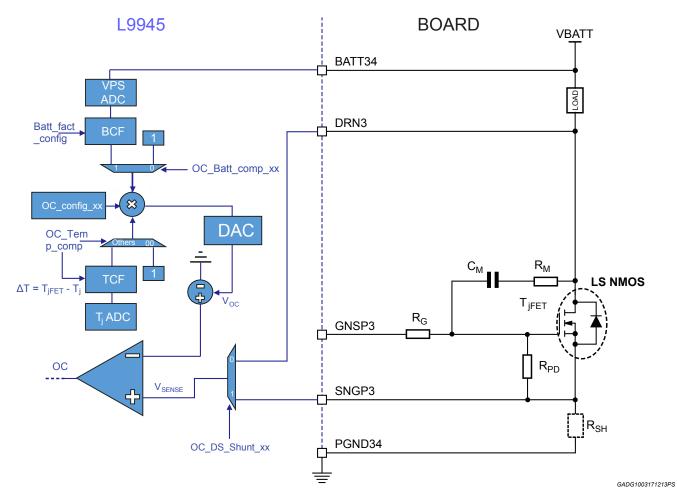

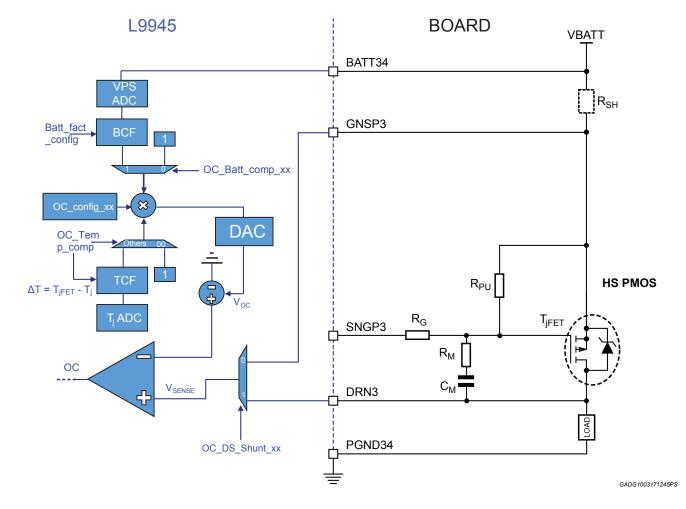

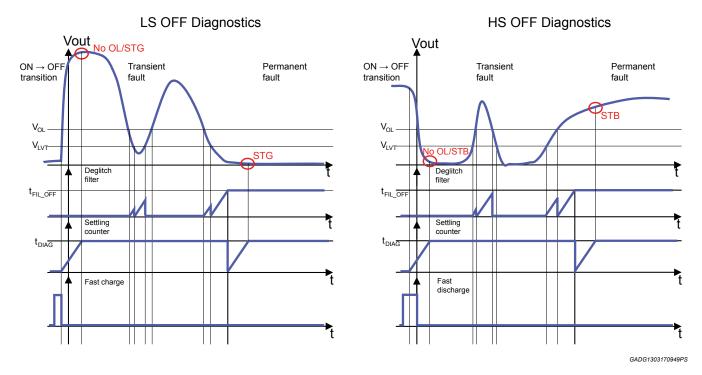

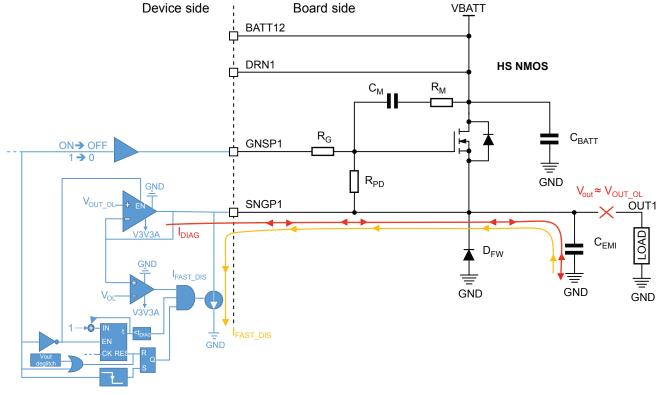

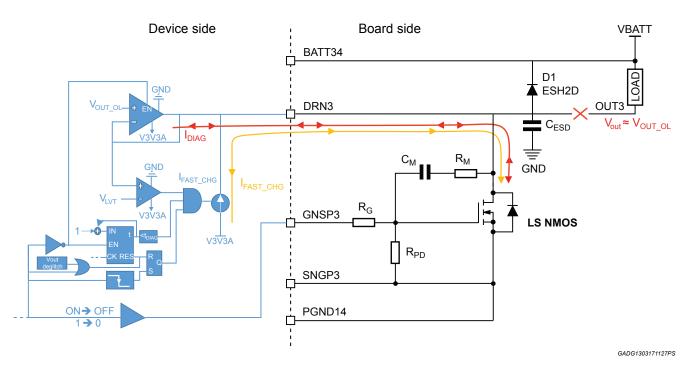

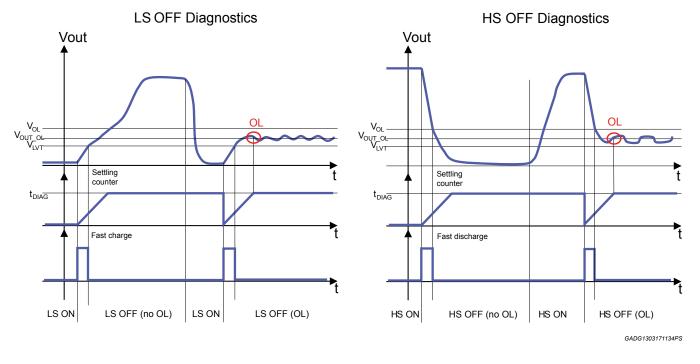

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|