# 128Kx32 5V NOR FLASH MODULE (SMD 5962-94716\*\*)

### **FEATURES**

- Access times of 50\*, 60, 70, 90, 120, 150ns

- Packaging:

- 66 pin, PGA type, 1.075 inch square, Hermetic Ceramic HIP (Package 400)

- 68 lead, Hermetic CQFP (G2U), 22.4mm (0.880 inch) square, 3.56mm (0.140 inch) high (Package 510)

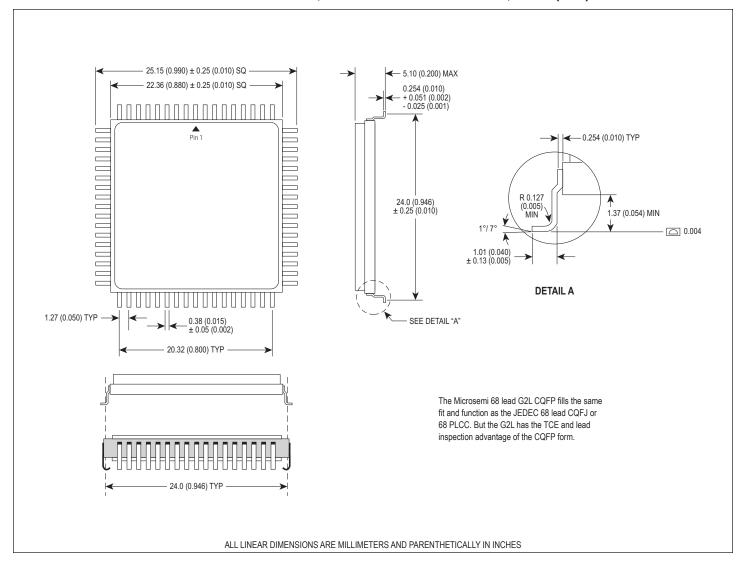

- 68 lead, Hermetic CQFP (G2L), 22.4mm (0.880 inch) square, 4.06mm (0.160 inch) high (Package 528)

- Sector architecture

- 8 equal size sectors of 16KBytes each

- Any combination of sectors can be concurrently erased.

Also supports full chip erase

- 100,000 erase/program cycles minimum

- Organized as 128Kx32

- Commercial, industrial and military temperature ranges

- 5 volt programming

- Low power CMOS

- Embedded erase and program algorithms

- TTL compatible inputs and CMOS outputs

- Built-in decoupling caps and multiple ground pins for low noise operation

- Page program operation and internal program control time

- Weight

WF128K32-XG2LX5 - 8 grams typical WF128K32-XG2UX5 - 8 grams typical WF128K32-XH1X5 - 13 grams typical

This product is subject to change without notice.

Note: For programming information and waveforms refer to Flash Programming 1M5 Application Note AN0036.

\* The access time of 50ns is available in Industrial and Commercial temperature ranges only.

#### FIGURE 1 – PIN CONFIGURATION FOR WF128K32N-XH1X5

| 1                   | 12                            | Top Vi                             | <b>ew</b> 34                 | 45                               | 56                  |

|---------------------|-------------------------------|------------------------------------|------------------------------|----------------------------------|---------------------|

|                     | ○WE₂#                         |                                    | I/O <sub>24</sub>            | Vcc 🔾                            |                     |

| ◯ I/O <sub>9</sub>  | ○CS₂#                         | ○I/O <sub>14</sub>                 | I/O <sub>25</sub>            | CS4#                             | I/O <sub>30</sub> ( |

| ◯ I/O <sub>10</sub> | GND                           | <b>○</b> I/ <b>0</b> <sub>13</sub> | I/O <sub>26</sub>            | WE4#                             | I/O <sub>29</sub>   |

| ○ A <sub>14</sub>   | O <sub>I/O<sub>11</sub></sub> | O <sub>I/O<sub>12</sub></sub>      | A7 (                         | I/O <sub>27</sub>                | I/O <sub>28</sub>   |

| ○ A₁6               | ○A₁0                          | ○oe#                               | A <sub>12</sub> 🔾            | A4 (                             | A1 ()               |

| O A <sub>11</sub>   | $\bigcirc_{A_9}$              | $\bigcirc$ NC                      | NC 🔾                         | <b>A</b> <sub>5</sub> $\bigcirc$ | A2 (                |

| $\bigcircA_0$       | ○A <sub>15</sub>              | ○WE₁#                              | A13 (                        | <b>A</b> <sub>6</sub>            | A <sub>3</sub> 🔾    |

| $\bigcircNC$        | Vcc                           | <b>○</b> I/ <b>0</b> <sub>7</sub>  | A8 (                         | WE3#                             | I/O <sub>23</sub>   |

| ◯ I/O₀              | ○cs₁#                         | ○I/O <sub>6</sub>                  | I/O <sub>16</sub>            | CS <sub>3</sub> #                | I/O <sub>22</sub>   |

| O I/O <sub>1</sub>  | $\bigcirc$ NC                 | ○I/O <sub>5</sub>                  | I/O <sub>17</sub>            | $GND \bigcirc$                   | I/O <sub>21</sub>   |

| ○ I/O <sub>2</sub>  | ○I/O₃                         | O <sub>I/O<sub>4</sub></sub>       | I/O <sub>18</sub> $\bigcirc$ | I/O <sub>19</sub>                | I/O <sub>20</sub>   |

| 11                  | 22                            | 33                                 | 44                           | 55                               | 66                  |

## Pin Description

| I/O <sub>0-31</sub> | Data Inputs/Outputs |

|---------------------|---------------------|

| A0-16               | Address Inputs      |

| WE <sub>1-4</sub> # | Write Enables       |

| CS1-4#              | Chip Selects        |

| OE#                 | Output Enable       |

| Vcc                 | Power Supply        |

| GND                 | Ground              |

| NC                  | Not Connected       |

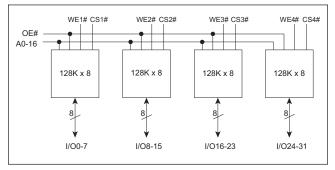

## **Block Diagram**

Microsemi Corporation reserves the right to change products or specifications without notice

<sup>\*\*</sup> For reference only. See SMD table on page 10.

#### FIGURE 3 - PIN CONFIGURATION FOR WF128K32-XG2UX5 AND WF128K32-XG2LX5

### **TOP VIEW**

#### PIN DESCRIPTION

| I/O <sub>0-31</sub> | Data Inputs/Outputs |

|---------------------|---------------------|

| A <sub>0-16</sub>   | Address Inputs      |

| WE <sub>1-4</sub> # | Write Enables       |

| CS <sub>1-4</sub> # | Chip Selects        |

| OE#                 | Output Enable       |

| Vcc                 | Power Supply        |

| GND                 | Ground              |

| NC                  | Not Connected       |

#### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS (1)**

| Parameter                                    |               | Unit   |

|----------------------------------------------|---------------|--------|

| Operating Temperature                        | -55 to +125   | °C     |

| Supply Voltage Range (Vcc)                   | -2.0 to +7.0  | V      |

| Signal voltage range (any pin except A9) (2) | -2.0 to +7.0  | V      |

| Storage Temperature Range                    | -65 to +150   | °C     |

| Lead Temperature (soldering, 10 seconds)     | +300          | °C     |

| Data Retention Mil Temp                      | 10            | years  |

| Endurance (write/erase cycles) Mil Temp      | 100,000 min   | cycles |

| A9 Voltage for sector protect (VID) (3)      | -2.0 to +12.5 | V      |

#### NOTES:

- Stresses above the absolute maximum rating may cause permanent damage to the device.

Extended operation at the maximum levels may degrade performance and affect reliability.

- 2. Minimum DC voltage on input or I/O pins is -0.5V. During voltage transitions, inputs may overshoot  $V_{SS}$  to -2.0 V for periods of up to 20ns. Maximum DC voltage on output and I/O pins is Vcc + 0.5V. During voltage transitions, outputs may overshoot to  $V_{CC}$  + 2.0 V for periods of up to 20ns.

- Minimum DC input voltage on A9 pin is -0.5V. During voltage transitions, A9 may overshoot Vss to -2V for periods of up to 20ns. Maximum DC input voltage on A9 is +12.5V which may overshoot to 13.5 V for periods up to 20ns.

#### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                | Symbol | Min | Max  | Unit |

|--------------------------|--------|-----|------|------|

| Supply Voltage           | Vcc    | 4.5 | 5.5  | V    |

| Operating Temp. (Mil, Q) | TA     | -55 | +125 | °C   |

| Operating Temp. (Ind)    | TA     | -40 | +85  | °C   |

| Operating Temp. (Com)    | TA     | 0   | +70  | °C   |

#### **CAPACITANCE**

Ta = +25°C

| Parameter                       | Symbol | Conditions                        | Max | Unit |

|---------------------------------|--------|-----------------------------------|-----|------|

| OE# capacitance                 | COE    | V <sub>IN</sub> = 0V, f = 1.0 MHz | 50  | pF   |

| WE <sub>1-4</sub> # capacitance | Cwe    | V <sub>IN</sub> = 0V, f = 1.0 MHz |     | pF   |

| HIP (PGA) H1                    |        |                                   | 20  |      |

| CQFP G2U/G2L                    |        |                                   | 15  |      |

| CS <sub>1-4</sub> # capacitance | Ccs    | V <sub>IN</sub> = 0V, f = 1.0 MHz | 20  | pF   |

| Data# I/O capacitance           | CI/O   | $V_{I/O} = 0V, f = 1.0 MHz$       | 20  | pF   |

| Address input capacitance       | CAD    | V <sub>IN</sub> = 0V, f = 1.0 MHz | 50  | pF   |

This parameter is guaranteed by design but not tested.

#### DC CHARACTERISTICS - CMOS COMPATIBLE

| Parameter                                   | Symbol             | Conditions                                                                            | Min        | Max       | Unit |

|---------------------------------------------|--------------------|---------------------------------------------------------------------------------------|------------|-----------|------|

| Input Leakage Current                       | ILI                | V <sub>CC</sub> = V <sub>CC MAX</sub> , V <sub>IN</sub> = GND to V <sub>CC</sub>      |            | 10        | μA   |

| Output Leakage Current                      | I <sub>LOx32</sub> | V <sub>CC</sub> = V <sub>CC MAX</sub> , V <sub>OUT</sub> = GND to V <sub>CC</sub>     |            | 10        | μA   |

| Vcc Active Current for Read (1)             | Icc1               | CS# = V <sub>IL</sub> , OE# = V <sub>IH</sub> , V <sub>CC</sub> = V <sub>CC MAX</sub> |            | 140       | mA   |

| Vcc Active Current for Program or Erase (2) | Icc2               | CS# = V <sub>IL</sub> , OE# = V <sub>IH</sub> , V <sub>CC</sub> = V <sub>CC MAX</sub> |            | 200       | mA   |

| Vcc Standby Current                         | Іссз               | Vcc = Vcc MAX, CS# = Vcc ±0.5V, OE# = ViH, f = 5MHz                                   |            | 6.5       | mA   |

| Vcc Static Current                          | Icc4               | Vcc = 5.5, CS# = ViH                                                                  |            | 0.6       | mA   |

| Input High Voltage                          | VIH                |                                                                                       | 2.0        | Vcc + 0.3 | V    |

| Input Low Voltage                           | VIL                |                                                                                       | -0.5       | +0.8      | V    |

| Voltage for Auto Select and Sector Protect  | V <sub>ID</sub>    |                                                                                       | 11.5       | 12.5      | V    |

| Output Low Voltage                          | VoL                | I <sub>OL</sub> = 8.0 mA, V <sub>CC</sub> = V <sub>CC MIN</sub>                       |            | 0.45      | V    |

| Output High Voltage                         | V <sub>OH1</sub>   | I <sub>OH</sub> = -2.5 mA, V <sub>CC</sub> = V <sub>CC MIN</sub>                      | 0.85 x Vcc |           | V    |

| Output High Voltage                         | V <sub>OH2</sub>   | IOH = -100 µA, VCC = VCC MIN                                                          | Vcc -0.4   |           | V    |

| Low Vcc Lock Out Voltage                    | VLKO               |                                                                                       | 3.2        |           | V    |

#### NOTES:

- 1. Icc current is typically less than 8mA/MHz, with OE# at ViH.

- 2. Icc active while Embedded Algorithm (program or erase) is in progress.

## AC CHARACTERISTICS - WRITE/ERASE/PROGRAM OPERATIONS, CS# CONTROLLED

| Parameter                         | Syn           | nbol | -{<br>Min | 50<br>Max | -6<br>Min | 60<br>Max | -7<br>Min | 70<br>Max | ے۔<br>Min | 90<br>Max | -1<br>Min | 20<br>Max | -1<br>Min | 50<br>Max | Unit |

|-----------------------------------|---------------|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|------|

| Write Cycle Time                  | tavav         | twc  | 50        |           | 60        |           | 70        |           | 90        |           | 120       |           | 150       |           | ns   |

| WE# Setup Time                    | twlel         | tws  | 0         |           | 0         |           | 0         |           | 0         |           | 0         |           | 0         |           | ns   |

| CS# Pulse Width                   | teleh         | tcp  | 25        |           | 30        |           | 35        |           | 45        |           | 50        |           | 50        |           | ns   |

| Address Setup Time                | tavel         | tas  | 0         |           | 0         |           | 0         |           | 0         |           | 0         |           | 0         |           | ns   |

| Data Setup Time                   | <b>t</b> DVEH | tos  | 25        |           | 30        |           | 30        |           | 45        |           | 50        |           | 50        |           | ns   |

| Data Hold Time                    | tehdx         | tон  | 0         |           | 0         |           | 0         |           | 0         |           | 0         |           | 0         |           | ns   |

| Address Hold Time                 | telax         | tан  | 40        |           | 45        |           | 45        |           | 45        |           | 50        |           | 50        |           | ns   |

| WE# Hold from WE# High            | tehwh         | twн  | 0         |           | 0         |           | 0         |           | 0         |           | 0         |           | 0         |           | ns   |

| CS# Pulse Width High              | tehel         | tсрн | 20        |           | 20        |           | 20        |           | 20        |           | 20        |           | 20        |           | ns   |

| Duration of Programming Operation | twnwh1        |      | 14        |           | 14        |           | 14        |           | 14        |           | 14        |           | 14        |           | μs   |

| Duration of Erase Operation       | twhwh2        |      | 2.2       | 60        | 2.2       | 60        | 2.2       | 60        | 2.2       | 60        | 2.2       | 60        | 2.2       | 60        | sec  |

| Read Recovery before Write        | tghel         |      | 0         |           | 0         |           | 0         |           | 0         |           | 0         |           | 0         |           | ns   |

| Chip Programming Time             |               |      |           | 12.5      |           | 12.5      |           | 12.5      |           | 12.5      |           | 12.5      |           | 12.5      | sec  |

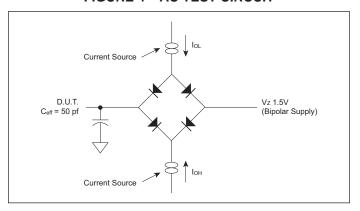

#### FIGURE 4 - AC TEST CIRCUIT

## **AC TEST CONDITIONS**

| Parameter                        | Тур                                        | Unit |

|----------------------------------|--------------------------------------------|------|

| Input Pulse Levels               | V <sub>IL</sub> = 0, V <sub>IH</sub> = 3.0 | V    |

| Input Rise and Fall              | 5                                          | ns   |

| Input and Output Reference Level | 1.5                                        | V    |

| Output Timing Reference Level    | 1.5                                        | V    |

#### Notes:

Vz is programmable from -2V to +7V.

$I_{\text{OL}}$  &  $I_{\text{OH}}$  programmable from 0 to 16mA.

Tester Impedance Z0 = 75  $\Omega$ .

$V_{Z}\ \text{is typically the midpoint of }V_{OH}\ \text{and}\ V_{OL}.$

$\ensuremath{\mathsf{Io_L}}\xspace \& \ensuremath{\mathsf{Io_H}}\xspace$  are adjusted to simulate a typical resistive load circuit.

ATE tester includes jig capacitance.

## AC CHARACTERISTICS - WRITE/ERASE/PROGRAM OPERATIONS, WE# CONTROLLED

| Parameter                                    | Syn    | nbol | -(  | 50   | -6  | 60   | -7  | 70   | -6  | 90   | -1  | 20   | -1  | 50   | Unit |

|----------------------------------------------|--------|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|------|

|                                              |        |      | Min | Max  |      |

| Write Cycle Time                             | tavav  | twc  | 50  |      | 60  |      | 70  |      | 90  |      | 120 |      | 150 |      | ns   |

| Chip Select Setup Time                       | telwl  | tcs  | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | ns   |

| Write Enable Pulse Width                     | twLwH  | twp  | 25  |      | 30  |      | 35  |      | 45  |      | 50  |      | 50  |      | ns   |

| Address Setup Time                           | tavwl  | tas  | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | ns   |

| Data Setup Time                              | tovwn  | tos  | 25  |      | 30  |      | 30  |      | 45  |      | 50  |      | 50  |      | ns   |

| Data Hold Time                               | twndx  | tон  | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | ns   |

| Address Hold Time                            | twlax  | tан  | 40  |      | 45  |      | 45  |      | 45  |      | 50  |      | 50  |      | ns   |

| Chip Select Hold Time                        | twhen  | tсн  | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | ns   |

| Write Enable Pulse Width High                | twnwL  | twph | 20  |      | 20  |      | 20  |      | 20  |      | 20  |      | 20  |      | ns   |

| Duration of Byte Programming Operation (min) | twnwh1 |      | 14  |      | 14  |      | 14  |      | 14  |      | 14  |      | 14  |      | μs   |

| Sector Erase Time                            | twhwh2 |      | 2.2 | 60   | 2.2 | 60   | 2.2 | 60   | 2.2 | 60   | 2.2 | 60   | 2.2 | 60   | sec  |

| Read Recovery Time Before Write              | tghwl  |      | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | ns   |

| Vcc Setup Time                               |        | tvcs | 50  |      | 50  |      | 50  |      | 50  |      | 50  |      | 50  |      | μs   |

| Chip Programming Time                        |        |      |     | 12.5 |     | 12.5 |     | 12.5 |     | 12.5 |     | 12.5 |     | 12.5 | sec  |

| Output Enable Setup Time                     |        | toes | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | ns   |

| Output Enable Hold Time (1)                  |        | tоен | 10  |      | 10  |      | 10  |      | 10  |      | 10  |      | 10  |      | ns   |

<sup>1.</sup> For Toggle and Data Polling.

#### **AC CHARACTERISTICS – READ ONLY OPERATIONS**

| Parameter                                                       | Syn   | nbol | -{  | 50  | -6  | 60  | -7  | 70  | -6  | 90  | -1  | 20  | -1: | 50  | Unit |

|-----------------------------------------------------------------|-------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|

|                                                                 |       |      | Min | Max |      |

| Read Cycle Time                                                 | tavav | trc  | 50  |     | 60  |     | 70  |     | 90  |     | 120 |     | 150 |     | ns   |

| Address Access Time                                             | tavqv | tacc |     | 50  |     | 60  |     | 70  |     | 90  |     | 120 |     | 150 | ns   |

| Chip Select Access Time                                         | telqv | tce  |     | 50  |     | 60  |     | 70  |     | 90  |     | 120 |     | 150 | ns   |

| OE# to Output Valid                                             | tglqv | toe  |     | 25  |     | 30  |     | 35  |     | 40  |     | 50  |     | 55  | ns   |

| Chip Select to Output High Z (1)                                | tehqz | tor  |     | 20  |     | 20  |     | 20  |     | 25  |     | 30  |     | 35  | ns   |

| OE# High to Output High Z (1)                                   | tgнqz | tor  |     | 20  |     | 20  |     | 20  |     | 25  |     | 30  |     | 35  | ns   |

| Output Hold from Address, CS# or OE# Change, whichever is first | taxqx | tон  | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns   |

Guaranteed by design, not tested.

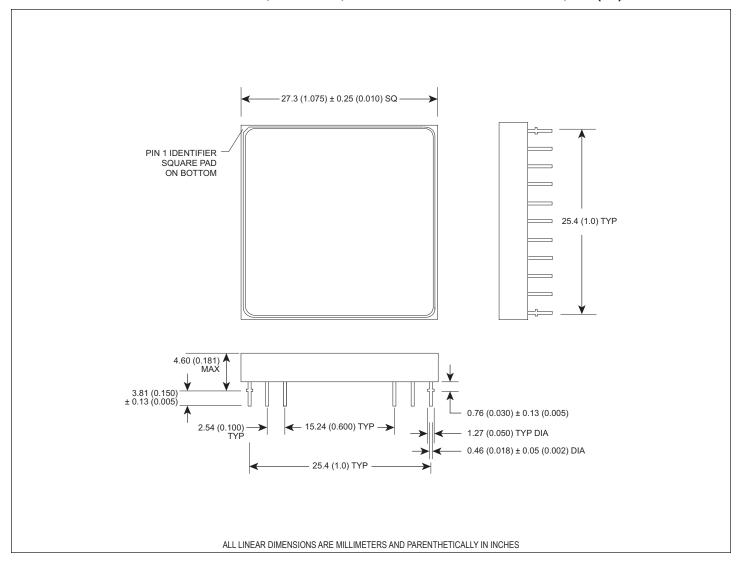

## PACKAGE 400 – 66 PIN, PGA TYPE, CERAMIC HEX-IN-LINE PACKAGE, HIP (H1)

## PACKAGE 510 - 68 LEAD, CERAMIC QUAD FLAT PACK, CQFP (G2U)

## PACKAGE 528 - 68 LEAD, CERAMIC QUAD FLAT PACK, CQFP (G2L)

#### **ORDERING INFORMATION**

|                                |                             | TTT          | 28K32 X - | ĬÎ |

|--------------------------------|-----------------------------|--------------|-----------|----|

| MICROSEMI CORPORATIO           | ON ————                     |              |           |    |

| NOR FLASH —                    |                             |              |           |    |

| Organization, 128K x 32 —      |                             |              |           |    |

| User configurable as 256       | 6K x 16 or 512K x 8         |              |           |    |

| IMPROVEMENT MARK —             |                             |              |           |    |

| N = No Connect at pin 8,       | 21, 28 and 39 in HIP for U  | pgrade       |           |    |

| ACCESS TIME (ns)               |                             |              |           |    |

| PACKAGE TYPE:                  |                             |              |           |    |

|                                | Hex In-line Package, HIP (  | Package 400) |           |    |

| ·                              | Quad Flat Pack, Low Profil  | ,            | 510)      |    |

|                                | Quad Flat Pack, Low Profile | ,            | •         |    |

|                                |                             |              |           |    |

| DEVICE GRADE:                  |                             |              |           |    |

| Q = MIL - STD 833 Co           | mpliant                     |              |           |    |

| M = Military Screened          | -55°C to +125°C             |              |           |    |

| I = Industrial                 | -40°C to +85°C              |              |           |    |

| C = Commercial                 | 0°C to + 70°C               |              |           |    |

| <b>VPP Programming Voltage</b> |                             |              |           | ┚╽ |

| 5 = 5V                         |                             |              |           |    |

| LEAD FINISH:                   |                             |              |           |    |

| Blank = Gold plated lead       | S                           |              |           |    |

| A = Solder dip leads           |                             |              |           |    |

| DEVICE TYPE     | SPEED | PACKAGE            | SMD NO.          |

|-----------------|-------|--------------------|------------------|

| 128K x 32 Flash | 150ns | 66 pin HIP (H1)    | 5962-94716 01H8X |

| 128K x 32 Flash | 120ns | 66 pin HIP (H1)    | 5962-94716 02H8X |

| 128K x 32 Flash | 90ns  | 66 pin HIP (H1)    | 5962-94716 03H8X |

| 128K x 32 Flash | 70ns  | 66 pin HIP (H1)    | 5962-94716 04H8X |

| 128K x 32 Flash | 60ns  | 66 pin HIP (H1)    | 5962-94716 05H8X |

|                 |       |                    |                  |

| 128K x 32 Flash | 150ns | 68 lead CQFP (G2U) | 5962-94716 01HNX |

| 128K x 32 Flash | 120ns | 68 lead CQFP (G2U) | 5962-94716 02HNX |

| 128K x 32 Flash | 90ns  | 68 lead CQFP (G2U) | 5962-94716 03HNX |

| 128K x 32 Flash | 70ns  | 68 lead CQFP (G2U) | 5962-94716 04HNX |

| 128K x 32 Flash | 60ns  | 68 lead CQFP (G2U) | 5962-94716 05HNX |

|                 |       |                    |                  |

| 128K x 32 Flash | 150ns | 68 lead CQFP (G2L) | 5962-94716 01HAX |

| 128K x 32 Flash | 120ns | 68 lead CQFP (G2L) | 5962-94716 02HAX |

| 128K x 32 Flash | 90ns  | 68 lead CQFP (G2L) | 5962-94716 03HAX |

| 128K x 32 Flash | 70ns  | 68 lead CQFP (G2L) | 5962-94716 04HAX |

| 128K x 32 Flash | 60ns  | 68 lead CQFP (G2L) | 5962-94716 05HAX |

NOTE: This table is for reference only. For 5962-94716 ordering information and specifications refer to latest SMD document.

## **Document Title**

128Kx32 5V NOR FLASH MODULE, SMD 5962-94716

## **Revision History**

| Rev#   | History                                                                                                                | Release Date | Status |

|--------|------------------------------------------------------------------------------------------------------------------------|--------------|--------|

| Rev 10 | Changes (Pg. 1-16)                                                                                                     | June 2011    | Final  |

|        | 10.1 Change document layout from White Electronic Designs to Microsemi                                                 |              |        |

|        | 10.2 Add document Revision History page                                                                                |              |        |

| Rev 11 | Changes (Pg. 1, 16)                                                                                                    | August 2011  | Final  |

|        | 11.1 Add "NOR" to headline                                                                                             |              |        |

| Rev 12 | Changes (Pg. 1, 3, 4, 5-15)                                                                                            | June 2012    | Final  |

|        | 12.1 Update features                                                                                                   |              |        |

|        | 12.2 Update Absolute Maximum Ratings, Recommended Operating Conditions and DC Characteristics – CMOS Compatible charts |              |        |

|        | 12.3 Delete subhead from all AC Characteristics charts                                                                 |              |        |

|        | 12.4 Delete AC Waveforms diagram                                                                                       |              |        |

|        | 12.5 Update package 510 – 68 Lead, Ceramic Quad Flat Pack, CQFP (G2U) diagram                                          |              |        |

|        | 12.6 Update package 528 – 68 Lead, Ceramic Quad Flat Pack, CQFP (G2L) diagram                                          |              |        |

|        | 12.7 Add NOR to Flash option in Ordering Information chart                                                             |              |        |

|        | 12.8 Update notes to QML chart                                                                                         |              |        |