# I<sup>2</sup>C Bus Buffer with Rise Time Accelerators and Hot Swap Capability

### ISL33001, ISL33002, ISL33003

The ISL33001, ISL33002, ISL33003 are 2-Channel Bus Buffers that provide the buffering necessary to extend the bus capacitance beyond the 400pF maximum specified by the I $^2$ C specification. In addition, the ISL33001, ISL33002, ISL33003 feature rise time accelerator circuitry to reduce power consumption from passive bus pull-up resistors and improve data-rate performance. All devices also include hot swap circuitry to prevent corruption of the data and clock lines when I $^2$ C devices are plugged into a live backplane, and the ISL33002 and ISL33003 add level translation for mixed supply voltage applications. The ISL33001, ISL33002, ISL33003 operate at supply voltages from +2.3V to +5.5V at a temperature range of -40°C to +85°C.

# **Summary of Features**

| PART<br>NUMBER | LEVEL TRANSLATION | ENABLE<br>PIN | READY<br>PIN | ACCELERATOR<br>DISABLE |

|----------------|-------------------|---------------|--------------|------------------------|

| ISL33001       | No                | Yes           | Yes          | No                     |

| ISL33002       | Yes               | No            | No           | Yes                    |

| ISL33003       | Yes               | Yes           | No           | No                     |

### **Related Literature**

- AN1543, "ISL33001MSOPEVAL1Z, ISL33002MSOPEVAL1Z, ISL33003MSOPEVAL1Z Evaluation Board User's Manual"

- AN1637, "Level Shifting Between 1.8V and 3.3V Using I<sup>2</sup>C Buffers"

#### **Features**

- 2 Channel I<sup>2</sup>C compatible bi-directional buffer

- +2.3VDC to +5.5VDC supply range

- >400kHz operation

- · Bus capacitance buffering

- · Rise time accelerators

- · Hot swapping capability

- ±6kV Class 3 HBM ESD protection on all pins

- ±12kV HBM ESD protection on SDA/SCL pins

- Enable pin (ISL33001 and ISL33003)

- · Logic level translation (ISL33002 and ISL33003)

- READY logic pin (ISL33001)

- · Accelerator disable pin (ISL33002)

- Pb-free (RoHS Compliant) 8 Ld SOIC (ISL33001 only), 8 Ld TDFN (3mmx3mm) and 8 Ld MSOP packages

- Low quiescent current . . . . . . . . . . 2.1mA typ

- Low shutdown current . . . . . . . . . . . . . 0.5µA typ

## Applications

- I<sup>2</sup>C bus extender and capacitance buffering

- Server racks for telecom, datacom, and computer servers

- · Desktop computers

- · Hot-swap board insertion and bus isolation

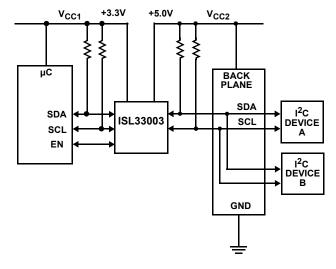

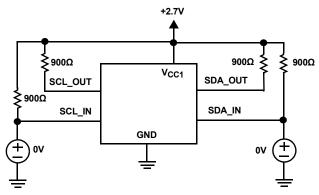

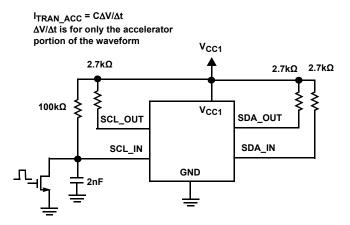

FIGURE 1. TYPICAL OPERATING CIRCUIT

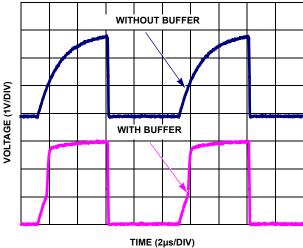

# 100kHz I<sup>2</sup>C BUS WITH 2.7kΩ PULL-UP RESISTOR AND 400pF BUS CAPACITANCE

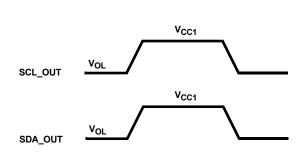

FIGURE 2. BUS ACCELERATOR PERFORMANCE

# **Ordering Information**

| PART NUMBER (Notes 1, 2, 3) | PART<br>MARKING           | TEMP. RANGE<br>(°C)       | PACKAGE<br>(Pb-free)             | PKG.<br>DWG. # |  |

|-----------------------------|---------------------------|---------------------------|----------------------------------|----------------|--|

| ISL33001IRTZ                | 3001                      | -40 to +85                | 8 Ld TDFN (0.65mm Pitch)         | L8.3x3A        |  |

| ISL33001IRT2Z               | 01R2                      | -40 to +85                | 8 Ld TDFN (0.5mm Pitch)          | L8.3x3H        |  |

| ISL33001IBZ                 | 33001 IBZ                 | -40 to +85                | 8 Ld SOIC                        | M8.15          |  |

| ISL33001IUZ                 | 33001                     | -40 to +85                | 8 Ld MSOP                        | M8.118         |  |

| ISL33002IRTZ                | 3002                      | -40 to +85                | 8 Ld TDFN (0.65mm Pitch)         | L8.3x3A        |  |

| ISL33002IRT2Z               | 02R2                      | -40 to +85                | 8 Ld TDFN (0.5mm Pitch)          | L8.3x3H        |  |

| ISL33002IUZ                 | 33002                     | -40 to +85                | 8 Ld MSOP                        | M8.118         |  |

| ISL33003IRTZ                | 3003                      | -40 to +85                | 8 Ld TDFN (0.65mm Pitch) L8.3x3A |                |  |

| ISL33003IRT2Z               | 03R2                      | -40 to +85                | 8 Ld TDFN (0.5mm Pitch) L8.3x3F  |                |  |

| ISL33003IUZ                 | 33003                     | -40 to +85                | 8 Ld MSOP M8.118                 |                |  |

| ISL33001MSOPEVAL1Z          | ISL33001 Evaluation Bo    | ard                       |                                  |                |  |

| ISL33002MSOPEVAL1Z          | ISL33002 Evaluation Bo    | ISL33002 Evaluation Board |                                  |                |  |

| ISL33003MS0PEVAL1Z          | ISL33003 Evaluation Board |                           |                                  |                |  |

#### NOTES:

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL33001</u>, <u>ISL33002</u>, <u>ISL33003</u>. For more information on MSL please see techbrief <u>TB363</u>.

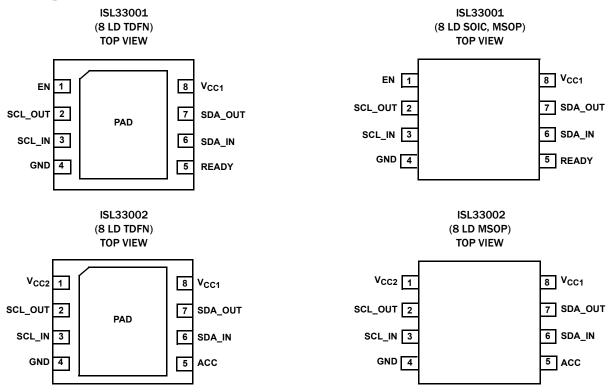

# **Pin Configurations**

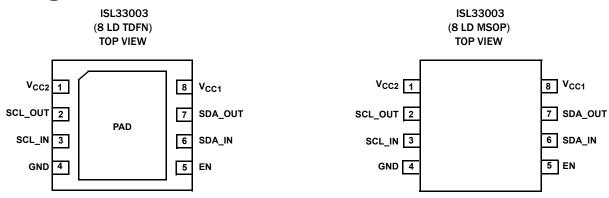

# Pin Configurations (Continued)

# **Pin Descriptions**

| PIN NAME         | PIN<br>NUMBER | FUNCTION                                                                                                                                                                                                                                                                                               | NOTES                                                              |

|------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| V <sub>CC1</sub> | 8             | $\rm V_{CC1}$ power supply, +2.3V to +5.5V. Decouple $\rm V_{CC1}$ to ground with a high frequency 0.01µF to 0.1µF capacitor.                                                                                                                                                                          |                                                                    |

| V <sub>CC2</sub> | 1             | $V_{CC2}$ power supply, +2.3V to +5.5V. Decouple $V_{CC2}$ to ground with a high frequency $0.01\mu F$ to $0.1\mu F$ capacitor. In level shifting applications, SDA_OUT and SCL_OUT logic thresholds are referenced to $V_{CC2}$ supply levels. Connect pull-up resistors on these pins to $V_{CC2}$ . | ISL33002 (8 LD TDFN, 8 LD MSOP)<br>ISL33003 (8 LD TDFN, 8 LD MSOP) |

| GND              | 4             | Device Ground Pin                                                                                                                                                                                                                                                                                      |                                                                    |

| EN               | 1             | Buffer Enable Pin. Logic "0" disables the device. Logic "1" enables the device. Logic                                                                                                                                                                                                                  | ISL33001 (8 LD TDFN, 8 LD SOIC, MSOP)                              |

|                  | 5             | threshold referenced to V <sub>CC1</sub> .                                                                                                                                                                                                                                                             | ISL33003 (8 LD TDFN, 8 LD MSOP)                                    |

| READY            | 5             | Buffer active 'Ready' open drain logic output. When buffer is active, READY is high impedance. When buffer is inactive, READY is low impedance to ground. Connect to $10k\Omega$ pull-up resistor to $V_{CC1}$ .                                                                                       | ISL33001 only                                                      |

| ACC              | 5             | Rise Time Accelerator Enable Pin. Logic "0" disables the accelerator. Logic "1" enables the accelerator. Logic threshold referenced to V <sub>CC1</sub> .                                                                                                                                              | ISL33002 only                                                      |

| SDA_IN           | 6             | Data I/O Pins                                                                                                                                                                                                                                                                                          |                                                                    |

| SDA_OUT          | 7             |                                                                                                                                                                                                                                                                                                        |                                                                    |

| SCL_IN           | 3             | Clock I/O Pins                                                                                                                                                                                                                                                                                         |                                                                    |

| SCL_OUT          | 2             |                                                                                                                                                                                                                                                                                                        |                                                                    |

| PAD              |               | Thermal pad should be connected to ground or floated.                                                                                                                                                                                                                                                  | Thermal Pad; TDFN only                                             |

Submit Document Feedback 3 intersil FN7560.6 July 11, 2014

#### **Absolute Maximum Ratings**

(All voltages referenced to GND)

| V <sub>CC1</sub> , V <sub>CC2</sub>          | 0.3V to +7V                                        |

|----------------------------------------------|----------------------------------------------------|

| SDA_IN, SCL_IN, SDA_OUT, SCL_OUT, READY      | 0.3V to +7V                                        |

| EN, ACC                                      | $\cdot \cdot -0.3V \text{ to } + (V_{CC1} + 0.3)V$ |

| Maximum Sink Current (SDA and SCL Pins)      | 20mA                                               |

| Maximum Sink Current (READY pin)             | 7mA                                                |

| Latch-Up Tested per JESD78, Level 2, Class A | 85°C                                               |

| ESD Ratings See <u>"ESI</u>                  | PROTECTION" on page 5                              |

### **Operating Conditions**

| Temperature Range, T <sub>A</sub>                          | -40°C to +85°C   |

|------------------------------------------------------------|------------------|

| V <sub>CC1</sub> and V <sub>CC2</sub> Supply Voltage Range | . +2.3V to +5.5V |

#### **Thermal Information**

| Thermal Resistance                | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-----------------------------------|------------------------|------------------------|

| 8 Ld TDFN Package (Notes 5, 6)    | 47                     | 4                      |

| (0.50mm Pitch)                    |                        |                        |

| 8 Ld TDFN Package (Notes 5, 6)    | 48                     | 6                      |

| (0.65mm Pitch)                    |                        |                        |

| 8 Ld MSOP Package (Notes 4, 7)    | 151                    | 50                     |

| 8 Ld SOIC Package (Notes 4, 7)    | 120                    | 56                     |

| Maximum Storage Temperature Range | 6                      | 5°C to +150°C          |

| Maximum Junction Temperature      |                        | +150°C                 |

| Pb-Free Reflow Profile            |                        | see <u>TB493</u>       |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- 4. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 5. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 6. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 7. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is taken at the package top center.

**Electrical Specifications**  $V_{EN} = V_{CC1}$ ,  $V_{CC1} = +2.3V$  to +5.5V,  $V_{CC2} = +2.3V$  to +5.5V, unless otherwise noted (Note 8). **Boldface limits apply over the operating temperature range, -40°C to +85°C.**

| PARAMETER                                    | SYMBOL                | CONDITIONS                                                                                 | TEMP<br>(°C) | MIN<br>(Note 9)     | TYP                 | MAX<br>(Note 9)     | UNITS |

|----------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------|--------------|---------------------|---------------------|---------------------|-------|

| POWER SUPPLIES                               |                       |                                                                                            |              | l                   | l                   | l .                 |       |

| V <sub>CC1</sub> Supply Range                | V <sub>CC1</sub>      |                                                                                            | Full         | 2.3                 | -                   | 5.5                 | V     |

| V <sub>CC2</sub> Supply Range                | V <sub>CC2</sub>      | ISL33002 and ISL33003                                                                      | Full         | 2.3                 | -                   | 5.5                 | ٧     |

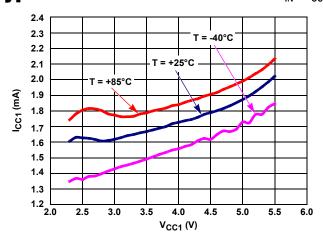

| Supply Current from V <sub>CC1</sub>         | I <sub>CC1</sub>      | V <sub>CC1</sub> = 5.5V; ISL33001 only ( <u>Note 11</u> )                                  | Full         | -                   | 2.1                 | 4.0                 | mA    |

|                                              |                       | V <sub>CC1</sub> = V <sub>CC2</sub> = 5.5V; ISL33002 and ISL33003 (Note 11)                | Full         | -                   | 2.0                 | 3.0                 | mA    |

| Supply Current from V <sub>CC2</sub>         | I <sub>CC2</sub>      | V <sub>CC2</sub> = V <sub>CC1</sub> = 5.5V; ISL33002 and ISL33003 (Note 11)                | Full         | -                   | 0.22                | 0.6                 | mA    |

| V <sub>CC1</sub> Shut-down Supply            | I <sub>SHDN1</sub>    | V <sub>CC1</sub> = 5.5V, V <sub>EN</sub> = GND; ISL33001 only                              | Full         | -                   | 0.5                 | -                   | μΑ    |

| Current                                      |                       | V <sub>CC1</sub> = V <sub>CC2</sub> = 5.5V, V <sub>EN</sub> = GND; ISL33003 only (Note 13) | Full         | -                   | 0.05                | -                   | μΑ    |

| V <sub>CC2</sub> Shut-down Supply<br>Current | I <sub>SHDN2</sub>    | V <sub>CC1</sub> = V <sub>CC2</sub> = 5.5V, V <sub>EN</sub> = GND, ISL33003 only (Note 13) | Full         | -                   | 0.06                | -                   | μΑ    |

| START-UP CIRCUITRY                           |                       |                                                                                            |              |                     |                     | l                   |       |

| Precharge Circuitry<br>Voltage               | V <sub>PRE</sub>      | SDA and SCL pins floating                                                                  | Full         | 0.8                 | 1                   | 1.2                 | V     |

| Enable High Threshold<br>Voltage             | V <sub>EN_H</sub>     |                                                                                            | +25          | -                   | 0.5*V <sub>CC</sub> | 0.7*V <sub>CC</sub> | V     |

| Enable Low Threshold<br>Voltage              | V <sub>EN_L</sub>     |                                                                                            | +25          | 0.3*V <sub>CC</sub> | 0.5*V <sub>CC</sub> | -                   | V     |

| Enable Pin Input Current                     | I <sub>EN</sub>       | Enable from 0V to V <sub>CC1;</sub> ISL33001 and ISL33003                                  | Full         | -1                  | 0.1                 | 1                   | μΑ    |

| Enable Delay, On-Off                         | t <sub>EN-HL</sub>    | ISL33001 and ISL33003 (Note 10)                                                            | +25          | -                   | 10                  | -                   | ns    |

| Enable Delay, Off-On                         | t <sub>EN-LH</sub>    | ISL33001 and ISL33003 (Figure 3)                                                           | +25          | -                   | 86                  | -                   | μs    |

| Bus Idle Time                                | t <sub>IDLE</sub>     | (Figure 4, Note 12)                                                                        | Full         | 50                  | 83                  | 150                 | μs    |

| Ready Pin OFF State<br>Leakage Current       | I <sub>OFF</sub>      | ISL33001 only                                                                              | +25          | -1                  | 0.1                 | 1                   | μΑ    |

| Ready Delay, On-Off                          | t <sub>READY-HL</sub> | ISL33001 only (Note 10)                                                                    | +25          | -                   | 10                  | -                   | ns    |

Submit Document Feedback 4 intersil FN7560.6

July 11, 2014

**Electrical Specifications**  $V_{EN} = V_{CC1}$ ,  $V_{CC1} = +2.3V$  to +5.5V,  $V_{CC2} = +2.3V$  to +5.5V, unless otherwise noted (Note 8). Boldface limits apply over the operating temperature range, -40 °C to +85 °C. (Continued)

| PARAMETER                                 | SYMBOL                | CONDITIONS                                                                                                                               | TEMP<br>(°C) | MIN<br>(Note 9)      | TYP                  | MAX<br>(Note 9)      | UNITS |

|-------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------|----------------------|----------------------|-------|

| Ready Delay, Off-On                       | t <sub>READY-LH</sub> | ISL33001 only (Note 10)                                                                                                                  | +25          | -                    | 10                   | -                    | ns    |

| Ready Output Low Voltage                  | V <sub>OL_READY</sub> | V <sub>CC1</sub> = +2.5V, I <sub>PULLUP</sub> = 3mA; ISL33001 only                                                                       | Full         | -                    | -                    | 0.4                  | V     |

| RISE-TIME ACCELERATORS                    |                       |                                                                                                                                          |              | •                    |                      |                      |       |

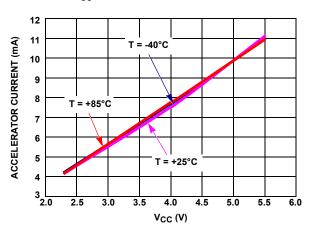

| Transient Accelerator<br>Current          | I <sub>TRAN_ACC</sub> | $V_{CC1} = 2.7V$ , $V_{CC2} = 2.7V$ ; (ACC = $0.7*V_{CC1}$ for ISL33002 only) (Figure 8)                                                 | +25          | -                    | 5                    | -                    | mA    |

| Accelerator Pin Enable<br>Threshold       | V <sub>ACC_EN</sub>   | ISL33002 only                                                                                                                            | +25          | -                    | 0.5*V <sub>CC1</sub> | 0.7*V <sub>CC1</sub> | V     |

| Accelerator Pin Disable<br>Threshold      | V <sub>ACC_DIS</sub>  | ISL33002 only                                                                                                                            | +25          | 0.3*V <sub>CC1</sub> | 0.5*V <sub>CC1</sub> | -                    | V     |

| Accelerator Pin Input<br>Current          | I <sub>ACC</sub>      | ISL33002 only                                                                                                                            | +25          | -1                   | 0.1                  | 1                    | μΑ    |

| Accelerator Delay, On-Off                 | t <sub>PDOFF</sub>    | ISL33002 only (Note 10)                                                                                                                  | +25          | -                    | 10                   | -                    | ns    |

| ESD PROTECTION                            |                       |                                                                                                                                          |              |                      | 1                    | i.                   |       |

| SDA, SCL I/O Pins                         |                       | Human Body Model, SDA and SCL pins to ground only (JESD22-A114)                                                                          | +25          | -                    | ±12                  | -                    | kV    |

| All Pins                                  |                       | Machine Model (JESD22-A115)                                                                                                              | +25          | -                    | ±400                 | -                    | ٧     |

|                                           |                       | Class 3 HBM ESD (JESD22-A114)                                                                                                            | +25          |                      | ±6                   | -                    | kV    |

| INPUT-OUTPUT CONNECTIO                    | NS                    |                                                                                                                                          |              | •                    |                      |                      |       |

| Input Low Threshold                       | V <sub>IL</sub>       | $V_{CC1} = V_{CC2}$ , 10k $\Omega$ to $V_{CC1}$ on SDA and SCL pins                                                                      | +25          | -                    | -                    | 0.3*V <sub>CC1</sub> | V     |

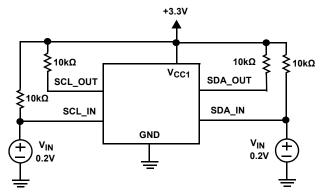

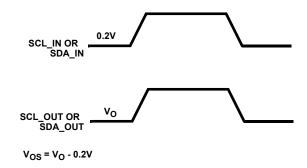

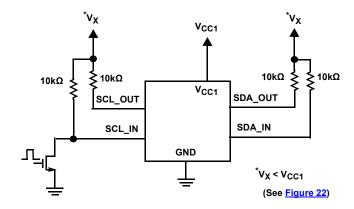

| Input-Output Offset<br>Voltage            | V <sub>OS</sub>       | $V_{CC1}$ = 3.3V, 10kΩ to $V_{CC1}$ on SDA and SCL pins, $V_{INPUT}$ = 0.2V; $V_{CC2}$ = 3.3V, ISL33002 and ISL33003 (Figure 5)          | Full         | 0                    | 50                   | 150                  | mV    |

| Output Low Voltage                        | V <sub>OL</sub>       | $V_{CC1}$ = 2.7V, $V_{INPUT}$ = 0V, $I_{SINK}$ = 3mA on SDA/SCL pins; $V_{CC2}$ = 2.7V, ISL33002 and ISL33003 (Figure 6)                 | Full         | -                    | -                    | 0.4                  | V     |

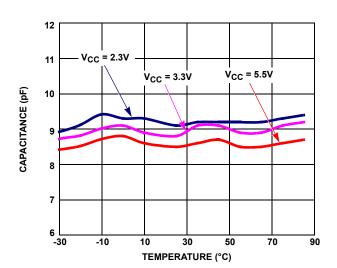

| Buffer SDA and SCL Pins Input Capacitance | C <sub>IN</sub>       | (Figure 25)                                                                                                                              | +25          | -                    | 10                   | -                    | pF    |

| Input Leakage Current                     | I <sub>LEAK</sub>     | SDA and SCL pins = V <sub>CC1</sub> = 5.5V;<br>V <sub>CC2</sub> = 5.5V, ISL33002 and ISL33003                                            | Full         | -5                   | 0.1                  | 5                    | μΑ    |

| TIMING CHARACTERISTICS                    |                       |                                                                                                                                          |              |                      |                      | •                    | •     |

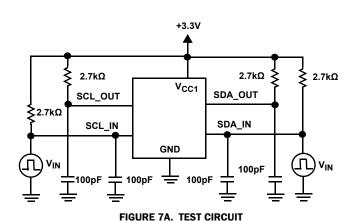

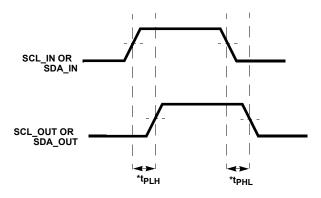

| SCL/SDA Propagation<br>Delay High-to-Low  | t <sub>PHL</sub>      | $C_{LOAD}$ = 100pF, 2.7k $\Omega$ to $V_{CC1}$ on SDA and SCL pins, $V_{CC1}$ = 3.3V; $V_{CC2}$ = 3.3V, ISL33002 and ISL33003 (Figure 7) | +25          | 0                    | 27                   | 100                  | ns    |

| SCL/SDA Propagation<br>Delay Low-to-High  | t <sub>PLH</sub>      | $C_{LOAD}$ = 100pF, 2.7k $\Omega$ to $V_{CC1}$ on SDA and SCL pins, $V_{CC1}$ = 3.3V; $V_{CC2}$ = 3.3V, ISL33002 and ISL33003 (Figure 7) | +25          | 0                    | 2                    | 26                   | ns    |

#### NOTES:

- 8. The algebraic convention, whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

- 9. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 10. Typical value determined by design simulations. Parameter not tested.

- 11. Buffer is in the connected state.

- 12. ISL33002 and ISL33003 limits established by characterization. Not production tested.

- 13. If the  $V_{CC1}$  and  $V_{CC2}$  voltages diverge, then the shut down  $I_{CC}$  increases on the higher voltage supply.

Submit Document Feedback 5 Intersil\* FN7560.6

July 11, 2014

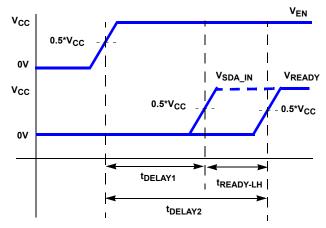

## **Test Circuits and Waveforms**

- SDA\_OUT and SCL pins connected to V<sub>CC</sub>

- Enable Delay Time Measured on ISL33001 only

- ISL33003 performance inferred from ISL33001

- If tDELAY1 < tEN-LH then tDELAY2 = tEN-LH + tIDLE + tREADY-LH

- If t<sub>DELAY1</sub> > t<sub>EN-LH</sub> then t<sub>DELAY2</sub> = t<sub>EN-LH</sub> + t<sub>READY-LH</sub>

FIGURE 3. ENABLE DELAY TIME

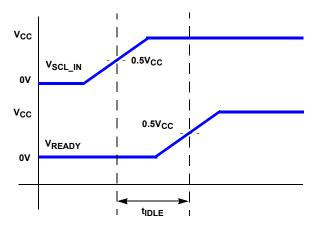

- V<sub>SDA IN</sub> = V<sub>SDA OUT</sub> = V<sub>SCL OUT</sub> = V<sub>EN</sub> = V<sub>CC</sub>

- EN Logic Input must be high for t > Enable Delay (t<sub>EN\_LH</sub>) prior to SCL\_IN transition

- Bus Idle Time Measured on ISL33001 only

- ISL33002 and ISL33003 performance inferred from ISL33001

FIGURE 4. BUS IDLE TIME

FIGURE 5A. TEST CIRCUIT

FIGURE 5B. MEASUREMENT POINTS

FIGURE 5. INPUT TO OUTPUT OFFSET VOLTAGE

FIGURE 6A. TEST CIRCUIT

FIGURE 6B. MEASUREMENT POINTS

FIGURE 6. OUTPUT LOW VOLTAGE

Submit Document Feedback FN7560.6 6 intersil July 11, 2014

# Test Circuits and Waveforms (Continued)

\*Propagation delay measured between 50% of  $V_{\mbox{\scriptsize CC1}}$

FIGURE 7B. MEASUREMENT POINTS

FIGURE 7. PROPAGATION DELAY

FIGURE 8. ACCELERATOR CURRENT TEST CIRCUIT

FIGURE 9. ACCELERATOR PULSE WIDTH TEST CIRCUIT

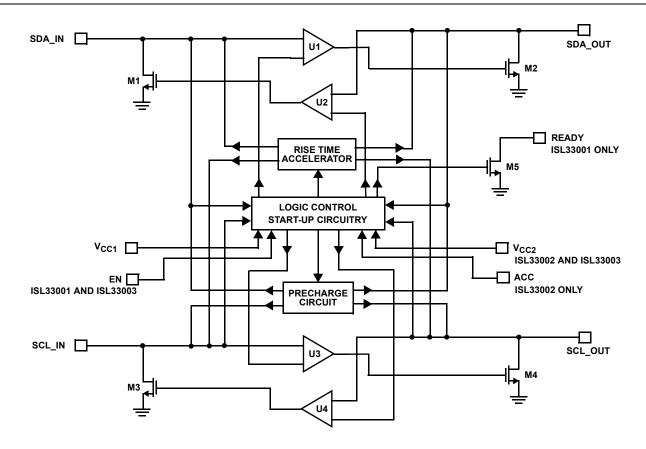

FIGURE 10. CIRCUIT BLOCK DIAGRAM

# **Application Information**

The ISL33001, ISL33002, ISL33003 ICs are 2-Wire Bidirectional Bus Buffers designed to drive heavy capacitive loads in open-drain/open-collector systems. The ISL33001, ISL33002, ISL33003 incorporate rise time accelerator circuitry that improves the rise time for systems that use a passive pull-up resistor for logic HIGH. These devices also feature hot swapping circuitry for applications that require hot insertion of boards into a host system (i.e., servers racks and I/O card modules). The ISL33001 features a logic output flag (READY) that signals the status of the buffer and an EN pin to enable or disable the buffer. The ISL33002 features two separate supply pins for voltage level shifting on the I/O pins and a logic input to disable the rise time accelerator circuitry. The ISL33003 features an EN pin and the level shifting functionality.

# I<sup>2</sup>C and SMBUS Compatibility

The ISL33001, ISL33002, ISL33003 ICs are  $I^2C$  and SMBUS compatible devices, designed to work in open-drain/open-collector bus environments. The ICs support both clock stretching and bus arbitration on the SDA and SCL pins. They are designed to operate from DC to more than 400kHz, supporting Fast Mode data rates of the  $I^2C$  specification.In addition, the buffer rise time accelerators are designed to increase the capacitive drive capability of the bus. With careful choosing of components, driving a bus with the  $I^2C$  specified maximum bus capacitance of 400pF at 400kHz data rate is possible.

### **Start-Up Sequencing and Hot Swap Circuitry**

The ISL33001, ISL33002, ISL33003 buffers contain undervoltage lock out (UVLO) circuitry that prevents operation of the buffer until the IC receives the proper supply voltage. For  $V_{CC1}$  and  $V_{CC2}$ , this voltage is approximately 1.8V on the rising edge of the supply voltage. Externally driven signals at the SDA/SCL pins are ignored until the device supply voltage is above 1.8V. This prevents communication errors on the bus until the device is properly powered up. The UVLO circuitry is also triggered on the falling edge when the supply voltage drops below 1.7V.

Once the IC comes out of the UVLO state, the buffer remains disconnected until it detects a valid connection state. A valid connection state is either a BUS IDLE condition (see Figure 4) or a STOP BIT condition (a rising edge on SDA\_IN when SCL\_IN is high) along with the SCL\_OUT and SDA\_OUT pins being logic high.

Note: For the ISL33001 and ISL33003 with EN pins, after coming out of UVLO, there will be an additional delay from the enable circuitry if the EN pin voltage is not rising at the same time as the supply pins (see <u>Figure 3</u>) before a valid connection state can be established.

Coming out of UVLO but prior to a valid connection state, the SDA and SCL pins are pre-charged to 1V to allow hot insertion. Because the bus at any time can be between 0V and  $V_{CC}$ , pre-charging the I/O pins to 1V reduces the maximum differential voltage from the buffer I/O pin and the active bus.

Submit Document Feedback 8 intersil FN7560.6

The pre-charge circuitry reduces system disturbance when the IC is hot plugged into a live back plane that may have the bus communicating with other devices.

Note: For The ISL33001 and ISL33003 with EN pins, the pre-charge circuitry is active only after coming out of UVLO and having the device enabled.

#### **Connection Circuitry**

Once a valid connection condition is met, the buffer is active and the input stage of the SDA/SCL pins is controlled by external drivers. The output of the buffer will follow the input of the buffer. The directionality of the IN/OUT pins are not exclusive (bi-directional operation) and functionally behave identical to each other. Being a two channel buffer, the SDA and SCL pins also behave identically. In addition, the SDA and SCL portions of the buffer are independent from each other. The SDA pins can be driven in one direction while the SCL pins can be driven opposite.

Refer to Figure 10 for the operation of the bi-directional buffer. When the input stage of the buffer on one side is driven low by an external device, the output of the buffer drives an open-drain transistor to pull the 'output' pin low. The 'output' pin will continue to be held low by the transistor until the external driver on the 'input' releases the bus.

To prevent the buffer from entering a latched condition where both internal transistors are actively pulling the I/O pins low, the buffer is designed to be active in only one direction. The buffer logic circuitry senses, which input stage is being externally driven low and sets that buffer to be the active one. For example, referring to Figure 10, if SDA\_OUT is externally driven low, buffer U2 will be active and buffer U1 is inactive. M1 is turned on to drive SDA\_IN low, effectively buffering the signal from SDA\_OUT to SDA IN. The low signal at the input of U1 will not turn M2 on because U1 remains inactive, preventing a latch condition.

#### **Buffer Output Low and Offset Voltage**

By design, when a logic input low voltage is forced on the input of the buffer, the output of the buffer will have an input to output offset voltage. The output voltage of the buffer is determined by Equation 1:

$$V_{OUT} = V_{IN} + V_{OS} + [V_{CC}/R_{PULL-UP} \times r_{ON}]$$

(EQ. 1)

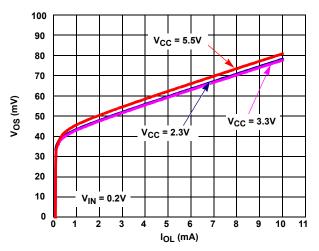

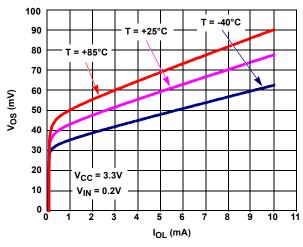

Where  $V_{\mbox{OS}}$  is the buffer internal offset voltage,  $R_{\mbox{Pull-Up}}$  is the pull-up resistance on the SDA/SCL pin to  $V_{CC}$  and  $r_{ON}$  is the ON-resistance of the buffer's internal NMOS pull-down device. The last term of the equation is the additional voltage drop developed by sink current and the internal resistance of the transistor. The Vos of the buffer can be determined by Figures 19, 20 and is typically 40mV. Reducing the pull-up resistor values increases the sink current and increases the output voltage of the buffer for a given input low voltage (Figures 17, through 20).

#### **Rise Time Accelerators**

The ISL33001, ISL33002, ISL33003 buffer rise time accelerators on the SDA/SCL pins improve the transient performance of the system. Heavy load capacitance or weak pull-up resistors on an Open-Drain bus cause the rise time to be excessively long, which leads to data errors or reduced data rate performance. The rise time accelerators are only active on the low-to-high transitions and provide an active constant current source to slew the voltage on the pin quickly (Figure 21).

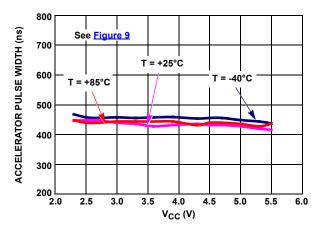

The rise time accelerators are triggered immediately after the buffer release threshold (approximately 30% of V<sub>CC</sub>) on both sides of the buffer is crossed. Once triggered, the accelerators are active for a defined pulse width (Figure 22) with the current source turning off as it approaches the supply voltage.

#### Enable Pin (ISL33001 and ISL33003)

When driven high, the enable pin puts the buffer into its normal operating state. After power-up, EN high will activate the bus pre-charge circuitry and wait for a valid connection state to enable the buffer and the accelerator circuitry.

Driving the EN pin low disables the accelerators, disables the buffer so that signals on one side of the buffer will be isolated from the other side, disables the pre-charge circuit and places the device in a low power shutdown state.

#### **READY Logic Pin (ISL33001 Only)**

The READY pin is a digital output flag for signaling the status of the buffer. The pin is the drain of an Open-Drain NMOS. Connect a resistor from the READY pin to V<sub>CC1</sub> to provide the high pull-up. The recommended value is  $10k\Omega$ .

When the buffer is disabled by having the EN pin low or if the start-up sequencing is not complete, the READY pin will be pulled low by the NMOS. When the buffer has the EN pin high and a valid connection state is made at the SDA/SCL pins, the READY pin will be pulled high by the pull-up resistor. The READY pin is capable of sinking 3mA when pulled low while maintaining a voltage of less than 0.4V.

#### **ACC Accelerator Pin (ISL33002 Only)**

The ACC logic pin controls the rise time accelerator circuitry of the buffer. When ACC is driven high, the accelerators are enabled and will be triggered when crossing the buffer release threshold. When ACC is driven low, the accelerators are disabled.

For lightly loaded buses, having the accelerators active may cause ringing or noise on the rising edge transition. Disabling the accelerators will have the buffers continue to perform level shifting with the V<sub>CC1</sub> and V<sub>CC2</sub> supplies and provide capacitance buffering.

#### **Propagation Delays**

On a low-to-high transition, the rising edge signal is determined by the bus pull-up resistor, load capacitance, and the accelerator current from the ISL33001, ISL33002, ISL33003 buffer. Prior to the accelerators becoming active, the buffer is connected and the output voltage will track the input of the buffer. When the accelerators activate the buffer connection is released and the signal on each side of the buffer rises independently. The accelerator current on both sides of the buffer will be equal. If the pull-up resistance on both sides of the buffer are also equal, then differences in the rise time will be proportional to the difference in capacitive loading on the two sides.

Because the signals on each side of the buffer rise independently, the propagation delay can be positive or negative. If the input side rises slowly relative to the output (i.e., heavy capacitive loading on the input and light load on the output) then the propagation delay  $t_{PLH}$  is negative. If the output side rises slowly relative to the input,  $t_{PLH}$  is positive.

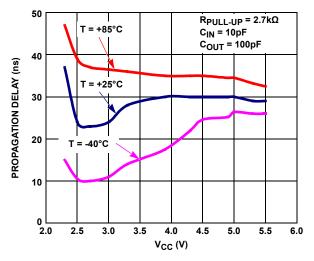

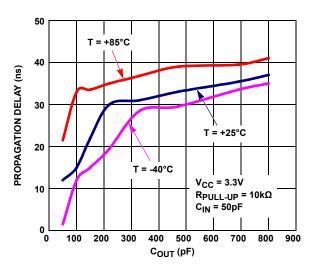

For high-to-low transitions, there is a finite propagation delay through the buffer from the time an external low on the input drives the NMOS output low. This propagation delay will always be positive because the buffer connect threshold on the falling edge is below the measurement points of the delay. In addition to the propagation delay of the buffer, there will be additional delay from the different capacitive loading of the buffer. Figures 23 and 24 show how the propagation delay from high-to-low,  $t_{\rm PHL}$ , is affected by  $t_{\rm CC}$  and capacitive loading.

The buffer's propagation delay times for rising and falling edge signals must be taken into consideration for the timing requirements of the system. SETUP and HOLD times may need to be adjusted to take into account excessively long propagation delay times caused by heavy bus capacitances.

#### **Pull-Up Resistor Selection**

While the ISL33001, ISL33002, ISL33003 2-Channel buffers are designed to improve the rise time of the bus in passive pull-up systems, proper selection of the pull-up resistor is critical for system operation when a buffer is used. For a bus that is operating normally without active rise time circuitry, using the ISL33001, ISL33002, ISL33003 buffer allows larger pull-up resistor values to reduce sink currents when the bus is driving low. However, choose a pull-up resistor value of no larger than  $20k\Omega$  regardless of the bus capacitance seen on the SDA/SCL lines. The Bus Idle or Stop Bit condition requires valid logic high voltages to give a valid connection state. Pull-up resistor values  $20k\Omega$  or smaller are recommended to overcome the typical  $150k\Omega$  impedance of the pre-charge circuitry, delivering valid high levels.

Submit Document Feedback 10 intersil FN7560.6

July 11, 2014

#

FIGURE 11. I<sub>CC1</sub> ENABLED CURRENT vs V<sub>CC1</sub> (ISL33001)

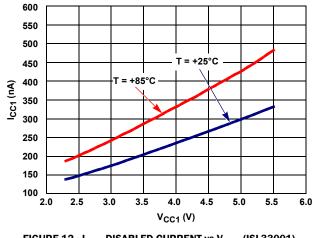

FIGURE 12. I<sub>CC1</sub> DISABLED CURRENT vs V<sub>CC1</sub> (ISL33001)

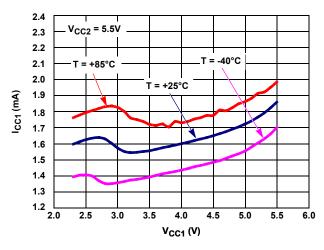

FIGURE 13.  $I_{CC1}$  ENABLED CURRENT vs  $V_{CC1}$  (ISL33002 AND ISL33003)

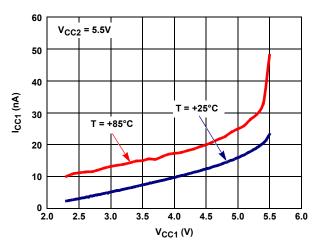

FIGURE 14. I<sub>CC1</sub> DISABLED CURRENT vs V<sub>CC1</sub> (ISL33003)

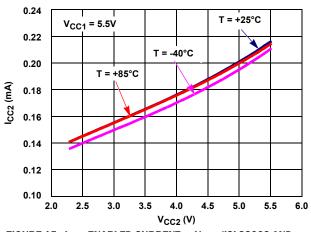

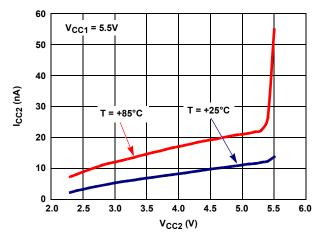

FIGURE 15.  $I_{CC2}$  ENABLED CURRENT vs  $V_{CC2}$  (ISL33002 AND ISL33003)

FIGURE 16. I<sub>CC2</sub> DISABLED CURRENT vs V<sub>CC2</sub> (ISL33003)

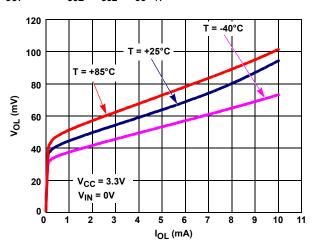

# $\textbf{Typical Performance Curves}_{\text{(Continued)}} \quad c_{\text{IN}} = c_{\text{OUT}} = 10 \text{pF}, \ v_{\text{CC1}} = v_{\text{CC2}} = v_{\text{CC}}, \ T_{\text{A}} = +25 \,^{\circ}\text{C}; \ \text{Unless Otherwise}$

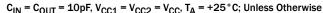

FIGURE 17. SDA/SCL OUTPUT LOW VOLTAGE VS SINK CURRENT VS VCC

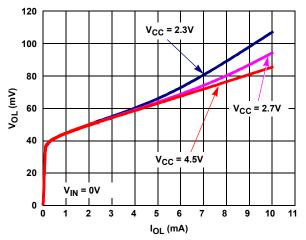

FIGURE 18. SDA/SCL OUTPUT LOW VOLTAGE vs SINK CURRENT vs **TEMPERATURE**

FIGURE 19. INPUT TO OUTPUT OFFSET VOLTAGE vs SINK CURRENT

FIGURE 20. INPUT TO OUTPUT OFFSET VOLTAGE vs SINK CURRENT vs TEMPERATURE

FIGURE 21. ACCELERATOR PULL-UP CURRENT vs V<sub>CC</sub>

FIGURE 22. ACCELERATOR PULSE WIDTH vs V<sub>CC</sub>

12 intersil FN7560.6 July 11, 2014

# $\textbf{Typical Performance Curves}_{\text{(Continued)}} \quad c_{\text{IN}} = c_{\text{OUT}} = 10 \text{pF}, \ V_{\text{CC1}} = V_{\text{CC2}} = V_{\text{CC}}, \ T_{\text{A}} = +25 \,^{\circ}\text{C}; \ \text{Unless Otherwise}$

FIGURE 23. PROPAGATION DELAY H-L vs V<sub>CC</sub>

FIGURE 24. PROPAGATION DELAY H-L vs COUT

FIGURE 25. SDA/SCL PIN CAPACITANCE vs TEMPERATURE vs V<sub>CC</sub>

# **Die Characteristics**

SUBSTRATE AND TDFN THERMAL PAD POTENTIAL (POWERED UP):

**GND**

#### **PROCESS:**

0.25µm CMOS

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest revision.

| DATE               | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 11, 2014      | FN7560.6 | In "Features" on page 1, changed "Low quiescent Current" from "2.2mA" to "2.1mA".  On page 4, added "Pb-Free Reflow Profile" entry to "Thermal Info" section.  In "Electrical Spec" table on page 4, changed "V <sub>CC</sub> " to "V <sub>CC1</sub> " in the "Supply Current from V <sub>CC2</sub> " row.  In "Electrical Spec" table on page 5, for parameter "Input Low Threshold", moved the "TYP" column entry to the "MAX" column.  On page 6, Figure 4, clarified the associated notes.  On page 7, Figure 8, changed "I <sub>ACC</sub> " to I <sub>TRAN_ACC</sub> ", and noted that the ΔV/Δt is for the accelerator portion of the waveform. |

| December 19, 2013  | FN7560.5 | Added Note 13 at the end of the "Elec Spec" table on page 5 as follows:  "13. If the Vcc1 and Vcc2 voltages diverge, then the shut-down lcc increases on the higher voltage supply."  Added reference "(Note 13)" after "ISL33003 only" in rows for Vcc1 and Vcc2 "Shut-down Supply current" parameters (last 2 rows of "Power Supplies" section) on page 4.                                                                                                                                                                                                                                                                                          |

| October 12, 2012   | FN7560.4 | Changed "SDA_IN, SCL_IN0.3V to $+(V_{CC1}+0.3)V$ , SDA_OUT, SCL_OUT0.3V to $+(V_{CC2}+0.3)V$ , ENABLE, READY, ACC0.3V to $+(V_{CC1}+0.3)V^*$ to "SDA_IN, SCL_IN, SDA_OUT, SCL_OUT, READY0.3V to $+7V$ ; ENABLE, ACC0.3V to $+(V_{CC1}+0.3)V^*$ , in the Absolute Maximum Ratings section at the top of page 4. Removed "Pb-free Reflow Profile" and link from "Thermal Information" section at the top of page 4. Added "open drain" and "Connect to $10k\Omega$ pull-up resistor to $V_{CC1}$ .", in Pin Descriptions in the READY section on page 3.                                                                                                |

| October 11, 2011   | FN7560.3 | Converted to new datasheet template.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    |          | Changed Title of datasheet from: "2-Wire Bus Buffer With Rise Time Accelerators and Hot Swap Capability" to: I <sup>2</sup> C Bus Buffer with Rise Time Accelerators and Hot Swap Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |          | Pg 1, added to Related Literature: AN1637, "Level Shifting Between 1.8V and 3.3V Using I2C Buffers"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    |          | Replaced POD M8.118 Rev 3 with Rev 4 due to the following changes:  Corrected lead width dimension in side view 1 from "0.25 - 0.036" to "0.25 - 0.36"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    |          | Replaced POD M8.15 Rev 1 with Rev 3 due to the following changes: Changed in Typical Recommended Land Pattern the following: 2.41(0.095) to 2.20(0.087) 0.76 (0.030) to 0.60(0.023) 0.200 to 5.20(0.205)                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                    |          | Figure 3 (was Fig1) - Added: - If tDELAY1 < tEN-LH then tDELAY2 = tEN-LH + tIDLE + tREADY-LH - If tDELAY1 > tEN-LH then tDELAY2 = tEN-LH + tREADY-LH and replaced graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| September 13, 2010 | FN7560.2 | Added SOIC package information to datasheet for ISL33001.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| April 30, 2010     | FN7560.1 | Changed typical value of "Supply Current from V <sub>CC1</sub> " on page 4 for ISL33001 only from 2.2mA to 2.1mA.  Changed typical value of "Input-Output Offset Voltage" on page 5 from 100mV to 50mV.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| March 18, 2010     | FN7560.0 | Initial Release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at www.intersil.com.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support

Submit Document Feedback 14 intersil FN7560.6

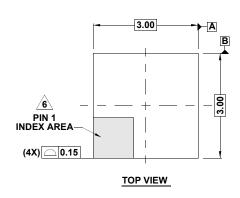

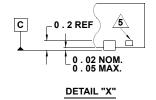

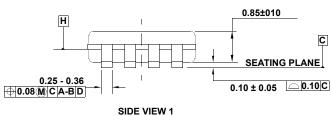

# **Package Outline Drawing**

#### L8.3x3H

8 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE (TDFN) Rev 0, 2/08

2.38

1.50 REF

6 X 0.50

2.20

1.64

8 X 0.40

8 X 0.40

8 X 0.40

**BOTTOM VIEW**

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

DETAIL "X"

- Lead width dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

Submit Document Feedback 15 FN7560.6 July 11, 2014

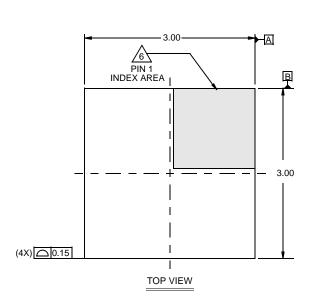

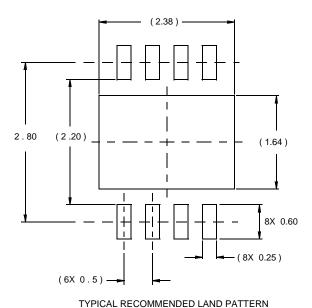

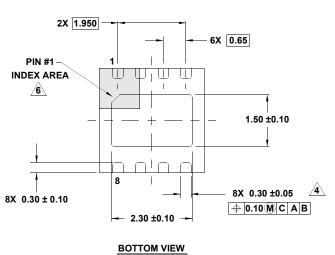

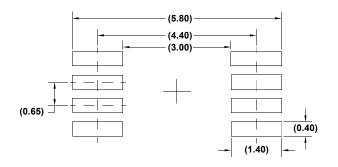

# Package Outline Drawing L8.3x3A

#### **8 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE**

Rev 4, 2/10

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- Dimension applies to the metallized terminal and is measured between 0.15mm and 0.20mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6 The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. Compliant to JEDEC MO-229 WEEC-2 except for the foot length.

Submit Document Feedback 16 FN7560.6 July 11, 2014

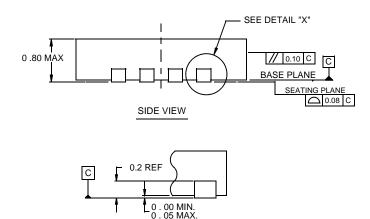

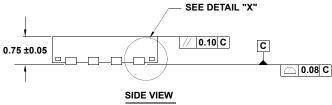

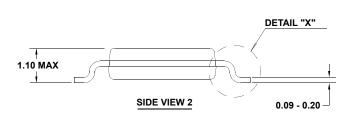

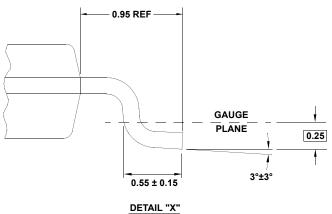

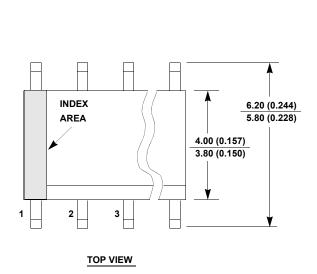

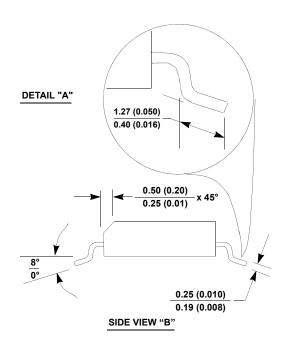

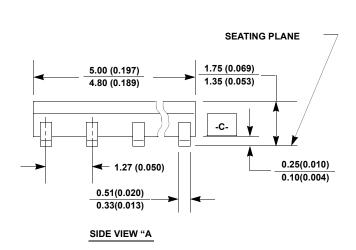

### **Package Outline Drawing** M8.118

#### 8 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE

Rev 4, 7/11

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- 1. Dimensions are in millimeters.

- 2. Dimensioning and tolerancing conform to JEDEC MO-187-AA and AMSEY14.5m-1994.

- 3. Plastic or metal protrusions of 0.15mm max per side are not included.

- Plastic interlead protrusions of 0.15mm max per side are not included.

- 5. Dimensions are measured at Datum Plane "H".

- 6. Dimensions in () are for reference only.

Submit Document Feedback 17 intersil FN7560.6 July 11, 2014

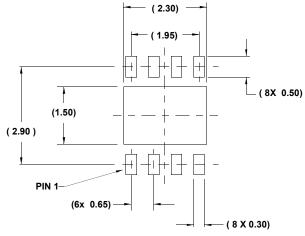

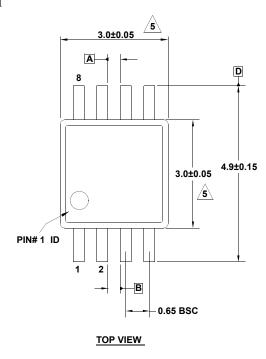

# **Package Outline Drawing**

#### M8.15

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE Rev  $\mathbf{4}, \mathbf{1/12}$

#### NOTES:

- 1. Dimensioning and tolerancing per ANSI Y14.5M-1994.

- Package length does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 3. Package width does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 4. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 5. Terminal numbers are shown for reference only.

- The lead width as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- 7. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

- 8. This outline conforms to JEDEC publication MS-012-AA ISSUE C.

Submit Document Feedback 18 intersil FN7560.6

July 11, 2014

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

### Intersil:

| ISL33001|BZ | ISL33001|BZ-T | ISL33001|RT2Z | ISL33001|RT2Z-T | ISL33001|RTZ | ISL33001|RTZ-T | ISL33001|RTZ-T | ISL33001|RTZ-T | ISL33002|RTZ-T | ISL33002|RTZ-T | ISL33002|RTZ-T | ISL33002|RTZ-T | ISL33002|RTZ-T | ISL33003|RTZ-T | ISL33003|R