Data Sheet March 5, 2010 FN6786.0

# DAE-1 for Manufacturers of High-Performance Class-D Audio Amplifiers

The D2Audio<sup>™</sup> D2-814xx is a fully self-contained 4 channel digital amplifier controller System-On-Chip (SOC). The D2-814xx enables rapid system design for manufacturers of home theater receivers, multi-room distributed audio systems, and powered speakers.

The D2-814xx contains a high-performance digital switching controller to play any input source on any output channel.

A configurable audio signal processor provides equalization, volume control, tone control, and compression for each channel, also crossover and power limiting for powered speaker applications.

The D2-814xx includes 4-channels I<sup>2</sup>S/Left-Justified inputs (16 to 24-bit, 32kHz to 192kHz), optional S/PDIF receiver (16 to 24-bit).

Boot options include: Self-boot from external serial ROM, asynchronous SCI slave boot, and serial slave boot from host uCon.

Please see the part number availability table for additional information on support for D2Audio™ SoundSuite™ firmware, as well as for SRS Labs™ and Dolby Labs™ algorithm support.

#### **Features**

- Powerful Digital Audio Management Reference Design Dependant SRC, Routing, Mixing, Multiple Digital Audio I/O, Tone Control, Parametric EQ, Compression

- Reduced Audio System Cost for Manufacturers of Class-D Audio Amplifiers

- Audio Processing Features Enable Optimized Speaker Performance and Delivers Dramatically Improved Sound Quality

- Minimum Development Cost/Risk/ Time-to-Market

- Pure Digital Path

- Superior Dynamic Range

- >110dB SNR, <0.1% THD+N

- 20Hz 20kHZ ±0.5dB Frequency Response

### Complete Class-D Amplifier Controller SOC

- Digital Switching Controller

- · Flexible Audio Input Sources

- Multiple Controller Synchronization

- Bridge and Non-Bridged Output Topologies

- Stand-Alone or Micro-Controller Boot Option

- 4 Channels

- Pb-Free (RoHS Compliant)

#### High-Performance Sound

- Unique Performance for Each Part Number

- Superior Dynamic Range

- >110 dB SNR, <0.1% THD+N

- 20Hz-20kHz ±0.5dB Frequency Response

#### Graceful Protection and Recovery

Complete Short-Circuit, Overcurrent, and Overvoltage Fault Protection

# Pure Digital Path

- Digital Audio Inputs which Support I<sup>2</sup>S and Left-Justified Formats with Linear PCM (32kHz to 192kHz, 16 to 24-bit)

- Digital Audio Input which Supports S/PDIF Format with Linear PCM (32kHz to 192kHz, 16 to 24-bit)

#### Multiple Part Offerings

- D2-81412-LR: 144-pin LQFP

- D2-81433-LR: 128-pin LQFP

- D2-81434-LR: 128-pin LQFP Supporting Dolby Labs<sup>™</sup> Technology

- D2-81435-LR: 128-pin LQFP Supporting SRS Labs<sup>™</sup> Technology

# **Ordering Information**

| PART NUMBER<br>(Notes 2, 3, 4) | PART MARKING | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|--------------------------------|--------------|----------------------|----------------|

| D2-81412-LR                    | D2-81412-LR  | 144 Ld LQFP          | Q144.20x20B    |

| D2-81433-LR                    | D2-81433-LR  | 128 Ld LQFP          | Q128.14x14     |

| D2-81434-LR (Note 1)           | D2-81434-LR  | 128 Ld LQFP          | Q128.14x14     |

| D2-81435-LR (Note 1)           | D2-81435-LR  | 128 Ld LQFP          | Q128.14x14     |

#### NOTES:

- D2Audio is obliged to confirm that NDAs and/or Evaluation Sample Licenses are in place with all 3rd Party IP Owners and potential D2Audio

customers before the sale of product or evaluation kits which contains either a D2-81434-LR or D2-81435-LR. Sale of the D2-81434-LR is only

available to Dolby Laboratories licensees in good standing. Sale of the D2-81435-LR is only available to SRS Labs licensees in good standing.

- 2. Delivery of 3rd party Firmware is subject to prior confirmation with the 3rd party IP vendors that the OEM/ODM/Customer is currently in good standing and having the appropriate licenses in place for the respective technology. TruSurround HD and TruSurround HD4 are trademarks of SRS Labs, Inc. Dolby and the Double-D symbol are registered trademarks of Dolby Laboratories.

- 3. Please see separate Application Notes for D2Audio™ SoundSuite, Dolby Labs™, and SRS Labs™ firmware, register tables and signal flow information.

- 4. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

# D2-81412, D2-81433, D2-81434, D2-81435

# **Table of Contents**

| D2-814xx Architecture                         | 4  |

|-----------------------------------------------|----|

| D2-814xx Signal Flow                          | 4  |

| Absolute Maximum Ratings                      |    |

| Thermal Information                           |    |

| Operating Conditions                          |    |

| Electrical Specifications                     |    |

| Switching Characteristics - Serial Audio Port |    |

| Switching Characteristics - 2-Wire Interface  |    |

| Switching Characteristics - 2-wire interface  | ′  |

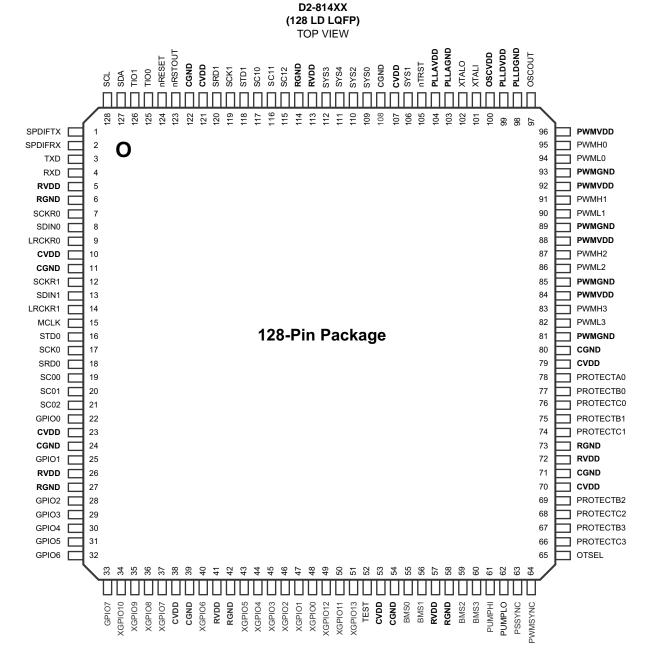

| D2-814xx 128-Pin Package Pinout               | 8  |

| Pin Definitions, 128-Pin LQFP Package         | 9  |

| Pin Descriptions 128-Pin Package              | 11 |

| Serial Audio Interface (SAI) Pins             | 11 |

| S/PDIF Pins                                   | 11 |

| PWM Pins                                      | 11 |

| 2-Wire Serial Pins                            | 11 |

| XGPIO Pins                                    | 11 |

| Reset and Test Pins                           | 12 |

| Crystal Oscillator and PLL Pins               | 12 |

| GPIO Pins                                     | 12 |

| System Configuration Pins                     | 12 |

| Serial Communications Interface (SCI) Pins    | 12 |

| Optional/Reserved Function Pins               | 12 |

| Boot Mode Select Pins                         | 13 |

| Timer (TIO) Pins                              | 13 |

| PWM Protection Pins                           | 13 |

| Power Pins                                    | 13 |

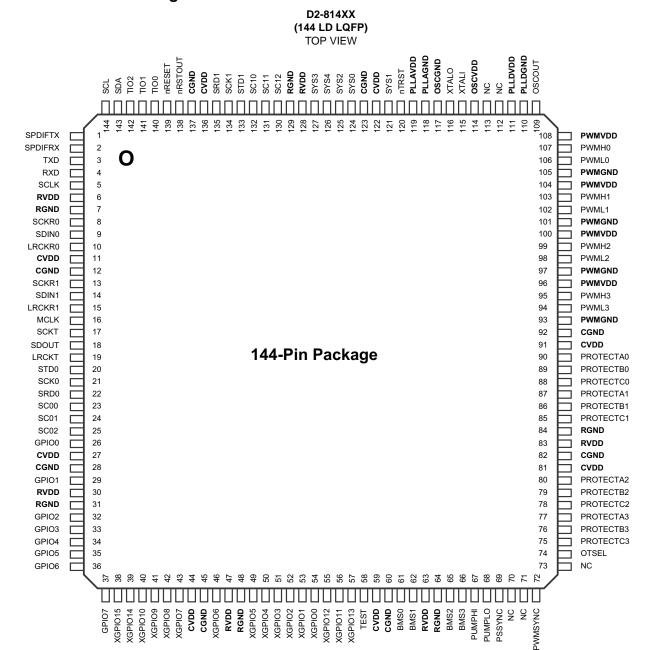

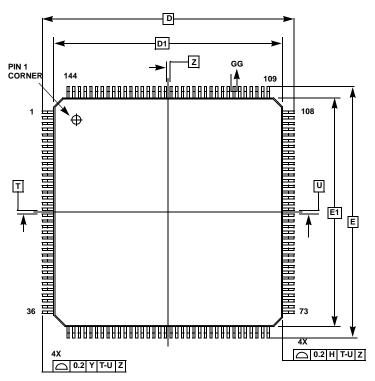

| D2-814xx 144-Pin Package Pinout            | 14 |

|--------------------------------------------|----|

| Pin Definitions 144-Pin LQFP Package       | 15 |

| Pin Descriptions 144-Pin Package           | 17 |

| Serial Audio Interface (SAI) Pins          | 17 |

| S/PDIF Pins                                | 18 |

| PWM Pins                                   | 18 |

| 2-Wire Serial Pins                         | 18 |

| XGPIO Pins                                 | 18 |

| Reset and Test Pins                        | 18 |

| Crystal Oscillator and PLL Pins            | 18 |

| GPIO Pins                                  | 18 |

| System Configuration Pins                  | 18 |

| Serial Communications Interface (SCI) Pins | 19 |

| Optional/Reserved Function Pins            | 19 |

| Boot Mode Select Pins                      | 19 |

| Timer (TIO) Pins                           | 19 |

| PWM Protection Pins                        | 19 |

| Power Pins                                 | 20 |

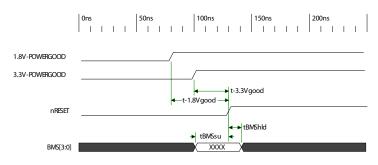

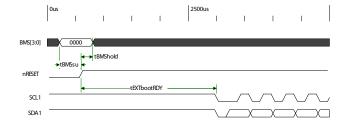

| D2-814xx Reset and Boot Modes              | 20 |

| Reset                                      | 20 |

| Boot Modes                                 | 20 |

| Document Revision History                  | 22 |

| Trademarks                                 | 23 |

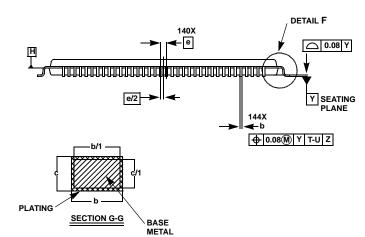

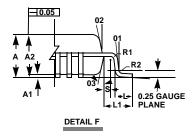

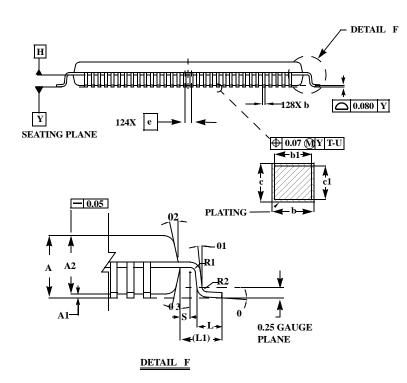

| Thin Plastic Quad Flatpack Package (LQFP)  | 24 |

| Thin Plastic Quad Flatpack Packages (LQFP) | 25 |

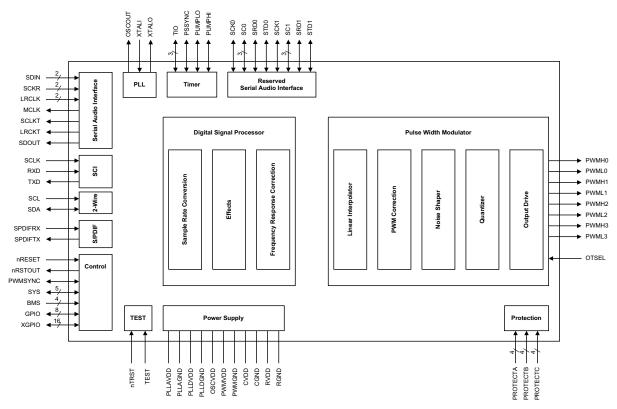

### D2-814xx Architecture

FIGURE 1. D2-814xx BLOCK DIAGRAM (144-PIN PACKAGE)

# D2-814xx Signal Flow

The D2-814xx supports a wide variety of signal flows that are fully programmable and are reference design dependant. The D2-814xx IC is to only be used as part of a licensed Reference Design Platform (RDP) package from D2Audio Corporation. The designer should note that each Reference Design Platform (RDP) package has a set signal flow, which is handled by the specified firmware and associated performance level, which is determined primarily by the surrounding components used in the design. Please refer to the specific D2Audio Digital Amplifier Datasheet for the design-specific signal flows and corresponding register set.

# **Absolute Maximum Ratings**

| Supply Voltage RVDD, PWMVDD0.3V to 4.0V Supply Voltage |

|--------------------------------------------------------|

| CVDD, PLLAVDD, PLLDVDD, OSCVDD0.3V to 2.4V             |

| Input Voltage, any input but XTALI0.3V to RVDD + 0.3V  |

| Input Voltage XTALI                                    |

| Input Current, any pin but supplies ±10mA              |

# **Operating Conditions**

Operating Temperature (T<sub>MAX</sub>) (Note 5) . . . . . . . . -10°C to +85°C

# **Thermal Information**

| hermal Resistance (Typical, Note 1)                 | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C/W) |

|-----------------------------------------------------|----------------------|------------------------|

| 128 Ld LQFP                                         |                      |                        |

| Airflow @ 0                                         | 59.1                 | 17.8                   |

| Airflow @ 1m/s                                      | 52.8                 | 17.8                   |

| Airflow @ 2m/s                                      | 50.5                 | 17.8                   |

| 144 Ld LQFP                                         |                      |                        |

| Airflow @ 0                                         | 56.5                 | 17.6                   |

| Airflow @ 1m/s                                      | 50.9                 | 17.6                   |

| Airflow @ 2m/s                                      | 48.9                 | 17.6                   |

| Junction Temperature (T <sub>JNC</sub> ) (Note 5)   |                      |                        |

| Storage Temperature Range (T <sub>STG</sub> ) (Note | 5)55                 | °C to +150°C           |

| Pb-Free Reflow Profile                              | s                    | ee link below          |

| http://www.intersil.com/pbfree/Pb-FreeR             | eflow.asp            |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTE:

5. For both 128 Ld LQFP and 144 Ld LQFP

# **Electrical Specifications**

| PARAMETER                                                                                        | SYMBOL           | MIN                | TYP     | MAX              | UNIT        |

|--------------------------------------------------------------------------------------------------|------------------|--------------------|---------|------------------|-------------|

| PIN CHARACTERISTICS T <sub>A</sub> = +25°C, CVDD = PLLAVDD = at 0.0V. All voltages referenced to |                  | D = 1.8V ±5%, RVDD | = PWMVD | D = 3.3V ±10%. A | All grounds |

| High Level Input Drive Voltage (Note 6)                                                          | V <sub>IH</sub>  | 2.0                | -       | =                | V           |

| Low Level Input Drive Voltage (Note 6)                                                           | V <sub>IL</sub>  | -                  | -       | 0.8              | V           |

| High Level Output Drive Voltage (Note 7) lout = -Pad Drive                                       | V <sub>OH</sub>  | RVDD - 0.3         | -       | -                | V           |

| Low Level Output Drive Voltage (Note 7) lout = +Pad drive                                        | V <sub>OL</sub>  | -                  | -       | 0.3              | V           |

| High Level Input Drive Voltage (Note 8)                                                          | V <sub>IHX</sub> | 0.7                | -       | OSCVDD           | V           |

| Low Level Input Drive Voltage (Note 8)                                                           | V <sub>ILX</sub> | -                  | -       | 0.3              | V           |

| High Level Output Drive Voltage OSCOUT pin                                                       | V <sub>OHO</sub> | PLLDVDD - 0.3      | -       | -                | V           |

| Low Level Output Drive Voltage OSCOUT pin                                                        | V <sub>OLO</sub> | -                  | -       | 0.3              | V           |

| Input Leakage Current                                                                            | I <sub>IN</sub>  | -                  |         | ±10              | uA          |

| Input Capacitance                                                                                | C <sub>IN</sub>  | -                  | 9       | -                | pF          |

| Output Capacitance                                                                               | C <sub>OUT</sub> | -                  | 9       | -                | pF          |

| POWER REQUIREMENTS Typical supply currents measured typical audio data traffic. Minimum          | ,,               | ·                  |         | •                | Hz with     |

| Core Supply Pins                                                                                 | CVDD             | 1.7                | 1.8     | 1.9              | V           |

|                                                                                                  |                  | 0.01               | 325     |                  | mA          |

| Digital I/O Pad Ring Supply Pins                                                                 | RVDD             | 3.0                | 3.3     | 3.6              | V           |

|                                                                                                  |                  | 0.01               | 10      |                  | mA          |

| PWM I/O Pad Ring Supply Pins                                                                     | PWMVDD           | 3.0                | 3.3     | 3.6              | V           |

|                                                                                                  |                  | 0.01               | 5       |                  | mA          |

#### **Electrical Specifications (Continued)**

| PARAMETER                | SYMBOL  | MIN  | TYP | MAX | UNIT |

|--------------------------|---------|------|-----|-----|------|

| Analog Supply Pins (PLL) | PLLAVDD | 1.7  | 1.8 | 1.9 | V    |

|                          |         | 0.01 | 10  |     | mA   |

|                          | PLLDVDD | 1.7  | 1.8 | 1.9 | V    |

|                          |         | 0.01 | 2   |     | mA   |

|                          | OSCVDD  | 1.7  | 1.8 | 1.9 | V    |

|                          |         | 0.01 | 4   |     | mA   |

#### NOTES:

- 6. All input pins except XTALI

- 7. All digital output pins

- 8. For XTALI input overdrive operation only

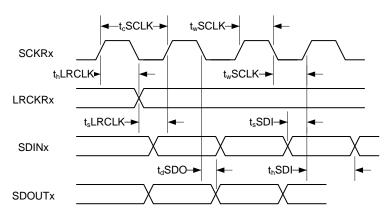

# **Switching Characteristics - Serial Audio Port**

$T_A$  = +25°C, CVDD = PLLAVDD = PLLDVDD = OSCVDD = 1.8V ±5%, RVDD = PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground.

| SYMBOL               | DESCRIPTION                                     | MIN | TYP | MAX  | UNIT |

|----------------------|-------------------------------------------------|-----|-----|------|------|

| t <sub>c</sub> SCLK  | SCKRx frequency - SCKR0, SCKR1                  |     |     | 12.5 | MHz  |

| t <sub>w</sub> SCLK  | SCKRx pulse width (high and low) - SCKR0, SCKR1 | 40  |     |      | ns   |

| t <sub>s</sub> LRCLK | LRCKRx setup to SCLK rising - LRCKR0, LRCKR1    | 20  |     |      | ns   |

| t <sub>h</sub> LRCLK | LRCKRx hold from SCLK rising - LRCKR0, LRCKR1   | 20  |     |      | ns   |

| t <sub>s</sub> SDI   | SDINx setup to SCLK rising - SDIN0, SDIN1       | 20  |     |      | ns   |

| t <sub>h</sub> SDI   | SDINx hold from SCLK rising - SDIN0, SDIN1      | 20  |     |      | ns   |

| t <sub>d</sub> SDO   | SDOUTx delay from SCLK falling                  |     |     | 20   | ns   |

FIGURE 2. SERIAL AUDIO PORT TIMING

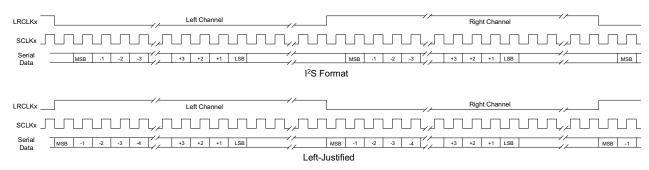

### **SERIAL AUDIO INTERFACE (SAI PORTS)**

The D2-814xx IC contains one SAI port for each pair of channels. Each input can support an individually selectable sample rate from 32kHz to 192kHz. All digital audio inputs are 3.3V CMOS logic. The SAI port is designed to interface with standard digital audio components and to accept I<sup>2</sup>S or Left-Justified data formats. Note: This port is entirely independent from the Reserved SAI port. The Reserved SAI port may or may not be used in a particular design.

For I<sup>2</sup>S format, the left channel data is read when LRCK is low. For the Left-Justified format, the left channel data is read when LRCK is high. Either format requires data to be valid on the rising edge of SCLK and sent MSB-first on SDIN with 32 bits of data per channel. Each set of digital inputs runs asynchronously to the others and may accept different sample rates and formats.

FIGURE 3. SAI PORT DATA FORMATS

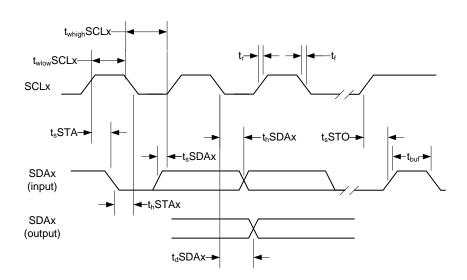

# **Switching Characteristics - 2-Wire Interface**

$T_A$  = +25°C, CVDD = PLLAVD = PLLDVDD = OSCVDD = 1.8V ±5%, RVDD = PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground.

| SYMBOL                  | DESCRIPTION                            | MIN | MAX | UNIT |

|-------------------------|----------------------------------------|-----|-----|------|

| fSCL                    | SCL frequency                          |     | 100 | kHz  |

| t <sub>buf</sub>        | Bus free time between transmissions    | 4.7 |     | μs   |

| t <sub>wlow</sub> SCLx  | SCL clock low                          | 4.7 |     | μs   |

| t <sub>whigh</sub> SCLx | SCL clock high                         | 4.0 |     | μs   |

| t <sub>s</sub> STA      | Setup time for a (repeated) Start      | 4.7 |     | μs   |

| t <sub>h</sub> STA      | Start condition Hold time              | 4.0 |     | μs   |

| t <sub>h</sub> SDAx     | SDA hold from SCL falling (see note)   | 0   |     | μs   |

| t <sub>s</sub> SDAx     | SDA setup time to SCL rising           | 250 |     | ns   |

| t <sub>d</sub> SDAx     | SDA output delay time from SCL falling |     | 3.5 | μs   |

| t <sub>r</sub>          | Rise time of both SDA and SCL          |     | 1   | μs   |

| t <sub>f</sub>          | Fall time of both SDA and SCL          |     | 300 | ns   |

| t <sub>s</sub> STO      | Setup time for a Stop condition        | 4.7 |     | μs   |

#### NOTE:

9. Data must be held sufficient time to bridge the 300ns transition time of SCL

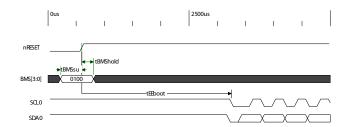

FIGURE 4. 2-WIRE INTERFACE TIMING

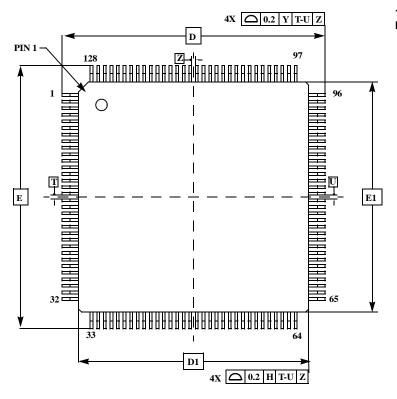

# D2-814xx 128-Pin Package Pinout

FIGURE 5. D2-814xx PINOUT, 128-PIN LQFP PACKAGE

# Pin Definitions, 128-Pin LQFP Package

TABLE 1. PIN DEFINITIONS TABLE, 128-PIN LQFP PACKAGE

| 7         SCKR0         I/O         Serial           9         LRCKR0         I/O         Serial           8         SDIN0         Input         Serial           12         SCKR1         I/O         Serial           14         LRCKR1         I/O         Serial           13         SDIN1         Input         Serial           SPDIF PINS         Input         S/PDII           2         SPDIFTX         Output         S/PDII           2         SPDIFRX         Input         S/PDII           PWM PINS         95         PWMH0         Output         Chann           94         PWML0         Output         Chann           91         PWMH1         Output         Chann           90         PWML1         Output         Chann           87         PWMH2         Output         Chann           86         PWML2         Output         Chann | r Clock Audio Bit Clock Receiver 0 Audio Left/Right Clock Receiver 0 Audio Data In 0 Audio Bit Clock Receiver 1 Audio Left/Right Clock Receiver 1 Audio Data In 1 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7         SCKR0         I/O         Serial           9         LRCKR0         I/O         Serial           8         SDIN0         Input         Serial           12         SCKR1         I/O         Serial           14         LRCKR1         I/O         Serial           13         SDIN1         Input         Serial           SPDIF PINS         Input         S/PDII           2         SPDIFTX         Output         S/PDII           2         SPDIFRX         Input         S/PDII           PWM PINS         95         PWMH0         Output         Chann           94         PWML0         Output         Chann           91         PWMH1         Output         Chann           90         PWML1         Output         Chann           87         PWMH2         Output         Chann           86         PWML2         Output         Chann | Audio Bit Clock Receiver 0 Audio Left/Right Clock Receiver 0 Audio Data In 0 Audio Bit Clock Receiver 1 Audio Left/Right Clock Receiver 1                         |

| 9 LRCKR0 I/O Serial 8 SDIN0 Input Serial 12 SCKR1 I/O Serial 14 LRCKR1 I/O Serial 13 SDIN1 Input Serial SPDIF PINS 1 SPDIFTX Output S/PDII 2 SPDIFRX Input S/PDII PWM PINS 95 PWMH0 Output Chann 94 PWML0 Output Chann 91 PWMH1 Output Chann 90 PWML1 Output Chann 87 PWMH2 Output Chann 86 PWML2 Output Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Audio Left/Right Clock Receiver 0 Audio Data In 0 Audio Bit Clock Receiver 1 Audio Left/Right Clock Receiver 1                                                    |

| 8         SDIN0         Input         Serial           12         SCKR1         I/O         Serial           14         LRCKR1         I/O         Serial           13         SDIN1         Input         Serial           SPDIF PINS           1         SPDIFTX         Output         S/PDII           2         SPDIFRX         Input         S/PDII           PWM PINS           95         PWMH0         Output         Chann           94         PWML0         Output         Chann           91         PWMH1         Output         Chann           90         PWML1         Output         Chann           87         PWMH2         Output         Chann           86         PWML2         Output         Chann                                                                                                                                       | Audio Data In 0 Audio Bit Clock Receiver 1 Audio Left/Right Clock Receiver 1                                                                                      |

| 12         SCKR1         I/O         Serial           14         LRCKR1         I/O         Serial           13         SDIN1         Input         Serial           SPDIF PINS           1         SPDIFTX         Output         S/PDII           2         SPDIFRX         Input         S/PDII           PWM PINS           95         PWMH0         Output         Chann           94         PWML0         Output         Chann           91         PWMH1         Output         Chann           90         PWML1         Output         Chann           87         PWMH2         Output         Chann           86         PWML2         Output         Chann                                                                                                                                                                                              | Audio Bit Clock Receiver 1 Audio Left/Right Clock Receiver 1                                                                                                      |

| 14         LRCKR1         I/O         Serial           13         SDIN1         Input         Serial           SPDIF PINS           1         SPDIFTX         Output         S/PDII           2         SPDIFRX         Input         S/PDII           PWM PINS           95         PWMH0         Output         Chann           94         PWML0         Output         Chann           91         PWMH1         Output         Chann           90         PWML1         Output         Chann           87         PWMH2         Output         Chann           86         PWML2         Output         Chann                                                                                                                                                                                                                                                    | Audio Left/Right Clock Receiver 1                                                                                                                                 |

| 13         SDIN1         Input         Serial           SPDIF PINS           1         SPDIFTX         Output         S/PDII           2         SPDIFRX         Input         S/PDII           PWM PINS           95         PWMH0         Output         Chann           94         PWML0         Output         Chann           91         PWMH1         Output         Chann           90         PWML1         Output         Chann           87         PWMH2         Output         Chann           86         PWML2         Output         Chann                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                   |

| SPDIF PINS           1         SPDIFTX         Output         S/PDII           2         SPDIFRX         Input         S/PDII           PWM PINS           95         PWMH0         Output         Chann           94         PWML0         Output         Chann           91         PWMH1         Output         Chann           90         PWML1         Output         Chann           87         PWMH2         Output         Chann           86         PWML2         Output         Chann                                                                                                                                                                                                                                                                                                                                                                   | Audio Data In 1                                                                                                                                                   |

| 1         SPDIFTX         Output         S/PDII           2         SPDIFRX         Input         S/PDII           PWM PINS           95         PWMH0         Output         Chann           94         PWML0         Output         Chann           91         PWMH1         Output         Chann           90         PWML1         Output         Chann           87         PWMH2         Output         Chann           86         PWML2         Output         Chann                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                   |

| 2         SPDIFRX         Input         S/PDII           PWM PINS           95         PWMH0         Output         Chann           94         PWML0         Output         Chann           91         PWMH1         Output         Chann           90         PWML1         Output         Chann           87         PWMH2         Output         Chann           86         PWML2         Output         Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                   |

| PWM PINS  95 PWMH0 Output Chann 94 PWML0 Output Chann 91 PWMH1 Output Chann 90 PWML1 Output Chann 87 PWMH2 Output Chann 86 PWML2 Output Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | = data output                                                                                                                                                     |

| 95 PWMH0 Output Chann 94 PWML0 Output Chann 91 PWMH1 Output Chann 90 PWML1 Output Chann 87 PWMH2 Output Chann 86 PWML2 Output Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | data input                                                                                                                                                        |

| 94 PWML0 Output Chann 91 PWMH1 Output Chann 90 PWML1 Output Chann 87 PWMH2 Output Chann 86 PWML2 Output Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                   |

| 91 PWMH1 Output Chann 90 PWML1 Output Chann 87 PWMH2 Output Chann 86 PWML2 Output Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | el 0 PWM high side output                                                                                                                                         |

| 90 PWML1 Output Chann 87 PWMH2 Output Chann 86 PWML2 Output Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | el 0 PWM low side output                                                                                                                                          |

| 87 PWMH2 Output Chann 86 PWML2 Output Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | el 1 PWM high side output                                                                                                                                         |

| 86 PWML2 Output Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | el 1 PWM low side output                                                                                                                                          |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | el 2 PWM high side output                                                                                                                                         |

| 83 PWMH3 Output Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | el 2 PWM low side output                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | el 3 PWM high side output                                                                                                                                         |

| 82 PWML3 Output Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | el 3 PWM low side output                                                                                                                                          |

| 65 OTSEL Input Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | topology select input                                                                                                                                             |

| 64 PWMSYNC I/O PWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Sync                                                                                                                                                              |

| 2-WIRE SERIAL PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   |

| 128 SCL I/O Two w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ire serial clock                                                                                                                                                  |

| 127 SDA I/O Two w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ire serial data                                                                                                                                                   |

| XGPIO PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                   |

| 34, 35, 36, 37, 40, 43, XGPIO[10:0] I/O Gener 44, 45, 46, 47, 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | al purpose I/O                                                                                                                                                    |

| 50 XGPIO[11] I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                   |

| 49 XGPIO[12] I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                   |

| 51 XGPIO[13] I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                   |

| GPIO PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                   |

| 33, 32, 31, 30, 29, 28, GPIO[7:0] I/O Gener 25, 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | al purpose I/O                                                                                                                                                    |

| RESET AND TEST PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                   |

| 124 nRESET Input Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - active low                                                                                                                                                      |

| 123 nRSTOUT Output Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | output- active low output                                                                                                                                         |

| 105 nTRST Input Test re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | set - active low                                                                                                                                                  |

| 52 TEST Input Hardw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | are test pin                                                                                                                                                      |

| CRYSTAL OSCILLATOR AND PLL PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                   |

| 97 OSCOUT Output Oscilla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                   |

| 101 XTALI Input Crysta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tor output to slave device                                                                                                                                        |

| 102 XTALO Output Crysta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                   |

# D2-81412, D2-81433, D2-81434, D2-81435

TABLE 1. PIN DEFINITIONS TABLE, 128-PIN LQFP PACKAGE (Continued)

| PIN NUMBER                           | PORT NAME             | TYPE   | DESCRIPTION                                           |

|--------------------------------------|-----------------------|--------|-------------------------------------------------------|

| SYSTEM CONFIGURA                     |                       |        | 2-23.11.119.11                                        |

| 109                                  | SYS0                  | I/O    | Reserved for factory test                             |

| 109                                  | SYS1                  | I/O    |                                                       |

| 110                                  | SYS2                  | 1/0    | _                                                     |

| 110                                  | SYS3                  | I/O    |                                                       |

| 111                                  | SYS4                  | I/O    |                                                       |

|                                      | FIONS INTERFACE (SCI) |        |                                                       |

|                                      | RXD                   | I/O    | SCI receive data                                      |

| 4                                    |                       |        |                                                       |

| 3                                    | TXD                   | I/O    | SCI transmit data                                     |

| 1                                    | UDIO INTERFACE PINS   | 1/0    | December 1 Oction Applies Interface 2 To Date on ODIO |

| 16                                   | STD0                  | 1/0    | Reserved Serial Audio Interface 0 Tx Data or GPIO     |

| 17                                   | SCK0                  | I/O    | Reserved Serial Audio Interface 0 Clock or GPIO       |

| 18                                   | SRD0                  | I/O    | Reserved Serial Audio Interface 0 Rx Data or GPIO     |

| 19                                   | SC00                  | I/O    | Reserved Serial Audio Interface 0 Control 0 or GPIO   |

| 20                                   | SC01                  | I/O    | Reserved Serial Audio Interface 0 Control 1 or GPIO   |

| 21                                   | SC02                  | I/O    | Reserved Serial Audio Interface 0 Control 2 or GPIO   |

| 118                                  | STD1                  | I/O    | Reserved Serial Audio Interface 1 Tx Data or GPIO     |

| 119                                  | SCK1                  | I/O    | Reserved Serial Audio Interface 1 Clock or GPIO       |

| 120                                  | SRD1                  | I/O    | Reserved Serial Audio Interface 1 Rx Data or GPIO     |

| 117                                  | SC10                  | I/O    | Reserved Serial Audio Interface 1 Control 0 or GPIO   |

| 116                                  | SC11                  | I/O    | Reserved Serial Audio Interface 1 Control 1 or GPIO   |

| 115                                  | SC12                  | I/O    | Reserved Serial Audio Interface 1 Control 2 or GPIO   |

| BOOT MODE SELECT                     | PINS                  |        |                                                       |

| 55                                   | BMS0                  | Input  | Boot Mode Select 0                                    |

| 56                                   | BMS1                  | Input  | Boot Mode Select 1                                    |

| 59                                   | BMS2                  | Input  | Boot Mode Select 2                                    |

| 60                                   | BMS3                  | Input  | Boot Mode Select 3                                    |

| TIMER (TIO) PINS                     |                       |        |                                                       |

| 126, 125                             | TIO[1:0]              | I/O    | Timer I/O ports                                       |

| 61                                   | PUMPHI                | I/O    | Power supply pump control, high side or GPIO          |

| 62                                   | PUMPLO                | I/O    | Power supply pump control, low side or GPIO           |

| 63                                   | PSSYNC                | I/O    | Power supply synchronization or GPIO                  |

| PWM PROTECTION PI                    | NS                    | 1      |                                                       |

| 78                                   | PROTECTA0             | I/O    | PWM Temperature status input, or GPIO                 |

| 67, 69, 75, 77                       | PROTECTB[3:0]         | I/O    | PWM Over Current Protection inputs, or GPIO           |

| 66, 68, 74, 76                       | PROTECTC[3:0]         | I/O    | PWM Shoot Through Current inputs or GPIO              |

| POWER PINS                           |                       | 1      |                                                       |

| 104                                  | PLLAVDD               | Power  | PLL Analog power                                      |

| 103                                  | PLLAGND               | Ground | PLL Analog ground                                     |

| 99                                   | PLLDVDD               | Power  | PLL Digital power                                     |

| 98                                   | PLLDGND               | Ground | PLL Digital ground                                    |

| 100                                  | OSCVDD                | Power  | Oscillator power                                      |

| 121, 107, 79, 70, 53,<br>38, 23, 10, | CVDD                  | Power  | Core power - 8 pins                                   |

TABLE 1. PIN DEFINITIONS TABLE, 128-PIN LQFP PACKAGE (Continued)

| PIN NUMBER                          | PORT NAME | TYPE   | DESCRIPTION                      |

|-------------------------------------|-----------|--------|----------------------------------|

| 122, 108, 80, 71, 54,<br>39, 24, 11 | CGND      | Ground | Core ground - 8 pins             |

| 96, 92, 88, 84                      | PWMVDD    | Power  | PWM output pin power - 4 pins    |

| 93, 89, 85, 81                      | PWMGND    | Ground | PWM output pin ground - 4 pins   |

| 113, 72, 57, 41, 26, 5              | RVDD      | Power  | Digital pad ring power - 6 pins  |

| 114, 73, 58, 42, 27, 6              | RGND      | Ground | Digital pad ring ground - 6 pins |

### Pin Descriptions 128-Pin Package

Pins are 100% firmware and Reference Design Platform (RDP) Package dependent for their functionality. Output pins have one of 3 drive strengths - 4mA, 8mA, or 16mA. These strengths are characterized by the current that the pin will source or sink at the specified output voltage level.

#### **SERIAL AUDIO INTERFACE (SAI) PINS**

#### MCLK Master Clock Output

Master Clock output for external ADC/DAC components with 8mA drive strength. Pin drives low on reset. MCLK is also used by test hardware to monitor various internal clocks.

#### SCKR0 SAI Receiver Bit Clock 1

SAI Receiver 0 bit clock is an output when D2-814xx is a master, or an input when D2-814xx is a slave. Defaults to an input on reset. Output has 4mA drive strength. Input has hysteresis.

### LRCKR0 SAI Receiver Left/Right Clock 0

SAI Receiver 0 left/right audio frame clock is an output when D2-814xx is a master or an input when D2-814xx is a slave. Defaults to an input on reset. Output has 4mA drive strength. Input has hysteresis.

#### SDIN0 SAI Receiver Serial Data Input 0

SAI Receiver 0 data input.

### SCKR1 SAI Receiver Bit Clock 1

SAI Receiver 1 bit clock is an output when D2-814xx is a master, or an input when D2-814xx is a slave. Defaults to an input on reset. Output has 4mA drive strength. Input has hysteresis.

#### LRCKR1 SAI Receiver Left/Right Clock 1

SAI Receiver 1 left/right audio frame clock is an output when D2-814xx is a master or an input when D2-814xx is a slave. Defaults to an input on reset. Output has 4mA drive strength. Input has hysteresis.

# SDIN1 SAI Receiver Serial Data Input 1

SAI Receiver 1 data input.

#### S/PDIF PINS

#### SPDIFRX S/PDIF Data Input

This pin is the S/PDIF audio input and accepts a 3.3V stereo input up to 192kHz. To drive this pin, appropriate buffer

and/or isolation circuits may be necessary to convert the S/PDIF cable input signal to clean logic levels.

# SPDIFTX S/PDIF Data Output

This pin is the S/PDIF audio output and drives a 3.3V stereo output up to 192kHz.

#### **PWM PINS**

#### PWMxH PWM High Side Driver Outputs

PWM high side driver outputs, where x is 0 to 3, with 16mA drive strength. Pin drives to state determined by OTSEL on reset.

#### PWMxL PWM Low Side Driver Outputs

PWM low side driver outputs, where x is 0 to 3, with 16mA drive strength. Pin drives low on reset.

#### **OTSEL Output Topology Select Input**

Output topology select input. OTSEL pin state controls the PWMxH drive polarity. Typically, OTSEL will be tied either high for active-low PWMxH FET drivers, or tied low for active-high PWMxH FET drivers.

#### **PWMSYNC PWM Synchronization**

PWM synchronization port with 4mA drive. Used in multi-D2-814xx configurations to synchronize the PWM controllers. The master D2-814xx will drive synchronization data to the slave D2-814xx(s), thus the pin will be an output on the master D2-814xx and an input on the slave D2-814xx(s). Pin floats on reset.

#### 2-WIRE SERIAL PINS

#### SCL Serial Clock

Two-Wire Serial clock port, open drain driver with 4mA drive strength. Bidirectional signal is used by both the master and slave controllers for clock signaling.

## SDA Serial Data

Two-Wire Serial data port, open drain driver with 4mA drive strength. Bidirectional signal used by both the master and slave controllers for data transport.

# **XGPIO PINS**

#### XGPIO[10:0] General Purpose I/O

Bidirectional GPIO port with 4mA driver. Resets to input port.

#### XGPIO[11] General Purpose I/O

Bidirectional GPIO port with 4mA driver. Resets to input port.

#### XGPIO[12] General Purpose I/O

Bidirectional GPIO port with 4mA driver. Resets to input port.

#### XGPIO[13] General Purpose I/O

Bidirectional GPIO port with 4mA driver. Resets to input port.

#### **RESET AND TEST PINS**

#### nRESET System Reset Input

Active low reset input with hysteresis. Low level activates system level reset, initializing all internal logic and program operations. System latches boot mode selection on the IRQ input pins on the rising edge.

#### nRSTOUT System Reset Output

Active low reset output with 4mA driver. Pin drives low on any of POR output, 3.3V brown out detector, 1.8V brown out detector.

#### **TEST Test Mode Input**

Hardware test mode control. For D2Audio usage only. Must be tied low.

#### nTRST Test Reset Input

Active low test port reset. Low level activates test reset, initializing test hardware. Must be driven low with nRESET.

#### **CRYSTAL OSCILLATOR AND PLL PINS**

## **OSCOUT** Oscillator Output

Analog oscillator output to slave D2-814xx devices. On reset, OSCOUT drives a buffered version of the crystal oscillator signal from the XTALI pin. May be turned off by program control.

#### **XTALI** Crystal Oscillator Input

Crystal oscillator analog input port. An external clock source would be driven into the this port. In multi-D2-814xx systems, the OSCOUT from the master D2-814xx would drive the XTALI pin.

# XTALO Crystal Oscillator Output

Crystal oscillator analog output port. When using an external clock source, this pin must be open.

### **GPIO PINS**

## GPIO[7:0] General Purpose I/O

Bidirectional GPIO ports with 4mA driver. Resets to input ports.

#### **SYSTEM CONFIGURATION PINS**

#### SYS0 System Configuration Data 0

Reserved for factory test. Tie low with  $10k\Omega$  resistor.

## SYS1 System Configuration Data 1

Reserved for factory test. Tie high with  $10k\Omega$  resistor.

#### SYS2 System Configuration Data 2

Reserved for factory test. Tie high with  $10k\Omega$  resistor.

#### SYS3 System Configuration Data 3

Reserved for factory test. Tie high with  $10k\Omega$  resistor.

#### SYS4 System Configuration Data 4

Reserved for factory test. Tie high with  $10k\Omega$  resistor.

#### **SERIAL COMMUNICATIONS INTERFACE (SCI) PINS**

#### **RXD** Receive Data

Serial communications receiver data with 4mA drive. Resets to input port. May be configured to GPIO.

#### **TXD** Transmit Data

Serial communications transmitter data with 4mA drive. Resets to input port. May be configured to GPIO.

#### OPTIONAL/RESERVED FUNCTION PINS

#### SCK0 Reserved Serial Audio Interface 0 Serial Clock

Serial Audio Interface 0 serial clock port with 4mA driver and hysteresis receiver. Resets to input port. May be configured as GPIO.

# SC00-SC02 Reserved Serial Audio Interface 0 Serial Control

0 serial control port with 4mA driver. Resets to input port. May be configured as GPIO.

# STD0 Reserved Serial Audio Interface 0 Serial Transmit Data

Serial Audio Interface 0 serial transmit data port with 4mA driver. Resets to input port. May be configured as GPIO.

# SRD0 Reserved Serial Audio Interface 0 Serial Receive Data

Serial Audio Interface 0 serial receive data port with 4mA driver. Resets to input port. May be configured as GPIO.

## SCK1 Reserved Serial Audio Interface 1 Serial Clock

Serial Audio Interface 1 serial clock port with 4mA driver and hysteresis receiver. Resets to input port. May be configured as GPIO.

# SC10-SC12 Reserved Serial Audio Interface 1 Serial Control

Serial Audio Interface 1 serial control port with 4mA driver. Resets to input port. May be configured as GPIO.

#### STD1 Reserved Serial Audio Interface 1 Serial Transmit Data

Serial Audio Interface 1 serial transmit data port with 4mA driver. Resets to input port. May be configured as GPIO.

# SRD1 Reserved Serial Audio Interface 1 Serial Receive Data

Serial Audio Interface 1 serial receive data port with 4mA driver. Resets to input port. May be configured as GPIO.

#### **BOOT MODE SELECT PINS**

#### BMS[3:0] Boot Mode Select Inputs

External boot mode select inputs. On nRESET deassertion, these pins provide the boot mode selection.

#### **TIMER (TIO) PINS**

#### TIO[1:0] Timer

Timer I/O ports with 4mA driver. May be configured as GPIO.

#### **PUMPHI** Power Supply Pump High

High side power supply pump output with 16mA driver. May be configured as GPIO. Drives low on reset. Provides control means for operating an external switching power supply.

#### **PUMPLO** Power Supply Pump Low

Low side power supply pump output with 16mA driver. May be configured as GPIO. Drives low on reset. Provides control means for operating an external switching power supply.

#### **PSSYNC** Power Supply Synchronization

Switching power supply synchronization signal with 16mA driver. May be configured as GPIO. Resets to

input port.

# **PWM PROTECTION PINS**

#### PROTECTA0 PWM Temperature Protection Input

PWM temperature protection input with hysteresis. May be configured as GPIO. In this instance, the GPIO pin has a 4mA driver.

# PROTECTB[3:0] PWM Overcurrent Protection Inputs