# CDP1853C/3

March 1997

# High-Reliability CMOS N-Bit 1 of 8 Decoder

#### **Features**

- Provides Direct Control of Up to 7 Input and 7 Output Devices When used with a CDP1800-Series Microprocessor

- CHIP ENABLE (CE) Allows Easy Expansion for Multilevel I/O Systems

## Ordering Information

| PACKAGE | TEMP. RANGE     | 5V         | 10V | PKG.<br>NO. |

|---------|-----------------|------------|-----|-------------|

| SBDIP   | -55°C to +125°C | CDP1853CD3 | -   | D16.3       |

## Description

The CDP1853/3 and CDP1853C/3 are high-reliability 1 of 8 decoders designed for use in general purpose microprocessor systems. These devices, which are functionally identical, are specifically designed for use as gated N-bit decoders and interface directly with the 1800-Series microprocessors without additional components. The CDP1853/3 has a recommended operating voltage range of 4V to 10.5V, and the CDP1853C/3 has a recommended operating voltage range of 4V to 6.5V.

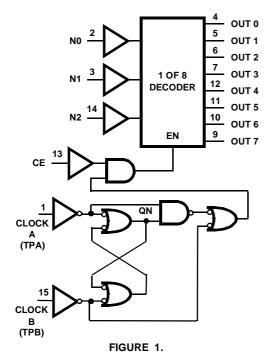

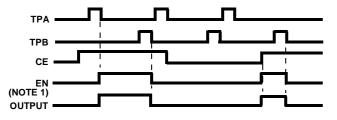

When CHIP ENABLE (CE) is high, the selected output will be true (high) from the trailing edge of CLOCK A (high-to-low transition) to the trailing edge of CLOCK B (high-to-low transition). All outputs will be low when the device is not selected (CE = 0) and during conditions of CLOCK A and CLOCK B as shown in Figure 2. The CDP1853/3 inputs N0, N1, N2, CLOCK A, and CLOCK B are connected to 1800series microprocessor outputs N0, N1, N2, TPA, and TPB respectively, when used to decode I/O commands as shown in Figure 5. The CHIP ENABLE (CE) input provides the capability for multiple levels of decoding as shown in Figure 6.

The CDP1853/3 can also be used as a general purpose 1 of 8 decoder for I/O and memory system applications as shown in Figure 4.

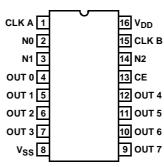

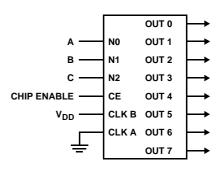

#### **Pinout**

# CDP1853/3 Functional Diagram

#### TRUTH TABLE

| CE | CL A | CL B | EN           |

|----|------|------|--------------|

| 1  | 0    | 0    | Qn-1(Note 2) |

| 1  | 0    | 1    | 1            |

| 1  | 1    | 0    | 0            |

| 1  | 1    | 1    | 1            |

| 0  | Х    | Х    | 0            |

| N2 | N1 | N0 | EN | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|----|----|----|----|---|---|---|---|---|---|---|---|

| 0  | 0  | 0  | 1  | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0  | 0  | 1  | 1  | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0  | 1  | 0  | 1  | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0  | 1  | 1  | 1  | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1  | 0  | 0  | 1  | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1  | 0  | 1  | 1  | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1  | 1  | 0  | 1  | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1  | 1  | 1  | 1  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| Х  | Х  | Х  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### NOTES:

- 1. 1 = High level, 0 = Low level, X = Don't care.

- 2. Qn-1 = Enable remains in previous state.

## **Static Electrical Specifications**

|                              |                             | C                     | CONDITION              | S                      | LIMITS |              |       |      |       |  |

|------------------------------|-----------------------------|-----------------------|------------------------|------------------------|--------|--------------|-------|------|-------|--|

|                              |                             |                       | .,                     | .,                     | -55°C  | -55°C, +25°C |       | 5°C  |       |  |

| PARAMETER                    | SYMBOL                      | ν <sub>ο</sub><br>(۷) | V <sub>IN</sub><br>(V) | V <sub>DD</sub><br>(V) | MIN    | MAX          | MIN   | MAX  | UNITS |  |

| Quiescent Device             | I <sub>SS</sub>             | -                     | 0, 5                   | 5                      | -50    | -            | -100  | -    | μΑ    |  |

| Current                      | (Note 1)                    | -                     | 0, 10                  | 10                     | -500   | -            | -1000 | -    | μΑ    |  |

| Output Low Drive             | I <sub>OL</sub>             | 0.4                   | -                      | 5                      | 2.3    | -            | 1.6   | -    | mA    |  |

| (Sink) Current               |                             | 0.5                   | -                      | 10                     | 3.7    | -            | 2.6   | -    | mA    |  |

| Output High Drive            | loн                         | 4.6                   | -                      | 5                      | -      | -1.7         | -     | -1.2 | mA    |  |

| (Source) Current             |                             | 9.5                   | -                      | 10                     | -      | -3.7         | -     | -2.6 | mA    |  |

| Output Voltage               | V <sub>OL</sub><br>(Note 2) | -                     | 0, 5                   | 5                      | -      | 0.1          | -     | 0.2  | V     |  |

| Low-Level                    |                             | -                     | 0, 10                  | 10                     | -      | 0.1          | -     | 0.2  | V     |  |

| Output Voltage<br>High-Level | V <sub>OH</sub><br>(Note 2) | -                     | 0, 5                   | 5                      | 4.9    | -            | 4.8   | -    | V     |  |

| nigri-Levei                  |                             | -                     | 0, 10                  | 10                     | 9.9    | -            | 9.8   | -    | V     |  |

| Input Low Voltage            | V <sub>IL</sub>             | 0.8, 4.2              | -                      | 5                      | -      | 1.5          | -     | 1.5  | V     |  |

|                              |                             | 1, 9                  | -                      | 10                     | -      | 3            | -     | 3    | V     |  |

| Input High Voltage           | V <sub>IH</sub>             | 0.8, 4.2              | -                      | 5                      | 3.5    | -            | 3.5   | -    | V     |  |

|                              |                             | 1, 9                  | -                      | 10                     | 7      | -            | 7     | -    | V     |  |

| Input Leakage Low            | I <sub>IL</sub>             | -                     | 0                      | 5                      | -1     | -            | -5    | -    | μΑ    |  |

|                              |                             | -                     | 0                      | 10                     | -1     | -            | -5    | -    | μΑ    |  |

| Input Leakage High           | I <sub>IH</sub>             | -                     | 5                      | 5                      | -      | 1            | -     | 5    | μΑ    |  |

|                              |                             | -                     | 10                     | 10                     | -      | 1            | -     | 5    | μΑ    |  |

| Input Capacitance            | C <sub>IN</sub> (Note 2)    | -                     | -                      | -                      | -      | 10           | -     | 10   | pF    |  |

| Output Capacitance           | C <sub>OUT</sub> (Note 2)   | -                     | -                      | -                      | -      | 15           | -     | 15   | pF    |  |

## NOTES:

- 1. The CDP1853C meets all 5V static electrical characteristics of the CDP1853 except quiescent device current for which the limits are:  $I_{SS} = -500\mu A$  at  $-55^{\circ}C$  and  $+25^{\circ}C$  and  $I_{SS} = -1000\mu A$  at  $+125^{\circ}C$ .

- 2. Guaranteed but not tested.

## **Dynamic Electrical Specifications** See Figure 2, $C_L = 100pF$ , $t_R$ , $t_F = 15ns$

|                                 |        |                 | LIMITS |       |     |     |       |

|---------------------------------|--------|-----------------|--------|-------|-----|-----|-------|

|                                 |        | V <sub>DD</sub> | -55°C, | +25°C | +12 | 5°C |       |

| PARAMETER                       | SYMBOL | (V)             | MIN    | MAX   | MIN | MAX | UNITS |

| Propagation Delay Time:         | tEOH   | 5               | -      | 175   | -   | 275 | ns    |

| Chip Enable (CE) to Output High |        | 10              | -      | 90    | -   | 150 | ns    |

**Dynamic Electrical Specifications** See Figure 2,  $C_L = 100pF$ ,  $t_R$ ,  $t_F = 15ns$

|                       |                   |                        | LIMITS              |     |     |     |       |

|-----------------------|-------------------|------------------------|---------------------|-----|-----|-----|-------|

|                       |                   | V                      | -55°C, +25°C +125°C |     | 5°C | 1   |       |

| PARAMETER             | SYMBOL            | V <sub>DD</sub><br>(V) | MIN                 | MAX | MIN | MAX | UNITS |

| Disable to Output Low | tEOL              | 5                      | -                   | 295 | -   | 400 | ns    |

|                       |                   | 10                     | -                   | 200 | -   | 250 | ns    |

| N Input to Output     | t <sub>NO</sub>   | 5                      | -                   | 225 | -   | 315 | ns    |

|                       |                   | 10                     | -                   | 120 | -   | 165 | ns    |

| Clock A to Output Low | t <sub>AO</sub>   | 5                      | -                   | 210 | -   | 300 | ns    |

|                       |                   | 10                     | -                   | 110 | -   | 150 | ns    |

| Clock B to Output Low | t <sub>BO</sub>   | 5                      | -                   | 295 | -   | 400 | ns    |

|                       |                   | 10                     | -                   | 200 | -   | 250 | ns    |

| Pulse Width:          | <sup>t</sup> CACA | 5                      | 50                  | -   | 75  | -   | ns    |

| Clock A               |                   | 10                     | 25                  | -   | 50  | -   | ns    |

| Clock B               | t <sub>CBCB</sub> | 5                      | 50                  | -   | 75  | -   | ns    |

|                       |                   | 10                     | 25                  | -   | 50  | -   | ns    |

$\label{eq:Recommended Operating Conditions} \textbf{At T}_A = \textbf{Full Package Temperature Range. For maximum reliability, operating conditions should be selected so that operation is always within the following ranges:}$

|                            | CDP1            | 853/3           | CDP18           |                 |       |

|----------------------------|-----------------|-----------------|-----------------|-----------------|-------|

| PARAMETER                  | MIN             | MAX             | MIN             | MAX             | UNITS |

| DC Operating Voltage Range | 4               | 10.5            | 4               | 6.5             | V     |

| Input voltage Range        | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V     |

#### **Absolute Maximum Ratings**

#### **Thermal Information**

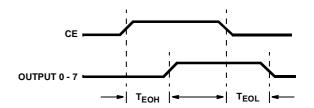

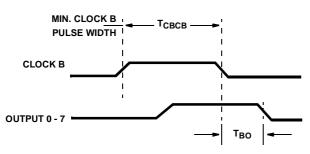

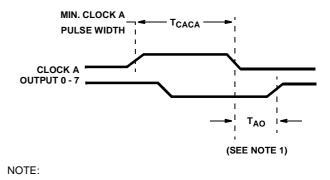

## **Timing Diagrams**

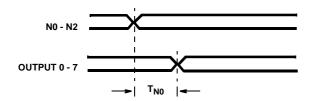

FIGURE 2A. N - INPUTS TO OUTPUTS DELAY TIME

FIGURE 2B. CE TO OUTPUT DELAY TIME

1. 10

1. To measure  $T_{\mbox{AO}}$ , Clock B must be tied low.

FIGURE 2C. CLOCK B TO OUTPUT DELAY TIME FIGURE 2D. CLOCK A TO OUTPUT DELAY TIME FIGURE 2. PROPAGATION DELAY TIME DIAGRAMS

#### NOTE:

1. Output enabled when EN = high. Internal signal shown for reference only (see Figure 1).

FIGURE 3. TIMING DIAGRAM

FIGURE 4. N-BIT DECODER USED AS A 1 OF 8 DECODER

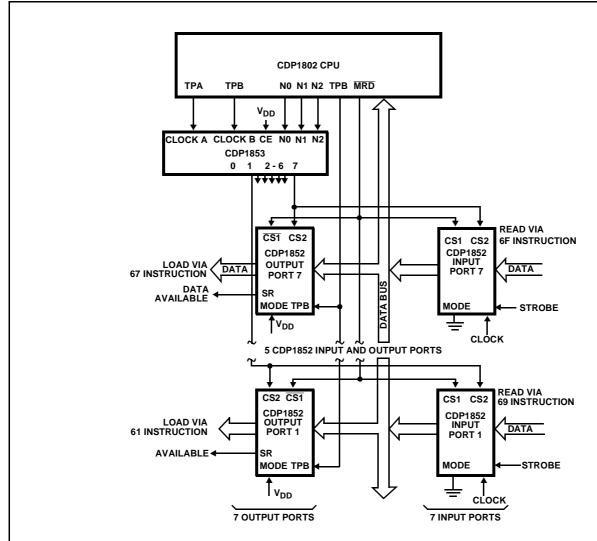

FIGURE 5. N-BIT DECODER IN A ONE LEVEL I/O SYSTEM

#### NOTE:

1. System shown will select up to 56 input and 48 output ports. With additional decoding, the total number of input and output ports can be further expanded.

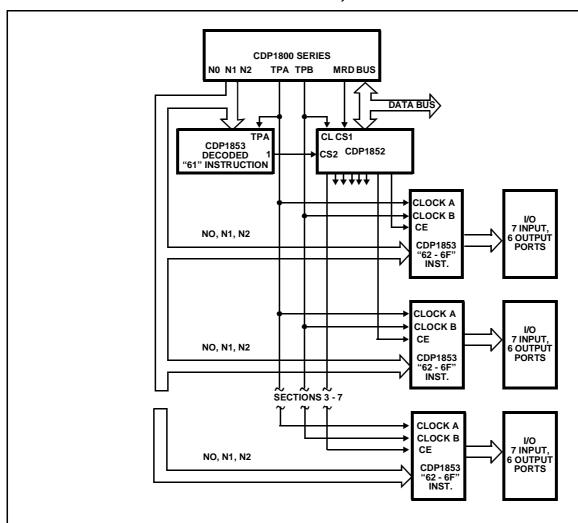

FIGURE 6. TWO LEVEL I/O USING CDP1853 AND CDP1852

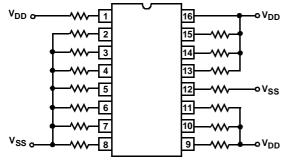

## Bias/Static Burn-In Circuit

| TYPE     | $V_{DD}$ | TEMPERATURE | TIME     |  |

|----------|----------|-------------|----------|--|

| CDP1853C | 7V       | +125°C      | 160 Hrs. |  |

#### NOTE:

1. All resist**്ടി ചർപ്പു** പ്രൂപ്പു പ്രൂപ്വു പ്രൂപ്പു പ്രൂപ്പു പ്രൂപ്പു പ്രൂപ്പു പ്രൂപ്പു പ്രൂപ്പു പ്രൂപ്വു പ്രൂപ്പു പ്രൂപ്വു പ്ര

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time withou notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may resul from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com