Preliminary Data Sheet No. PD60034-J

**IR2151** (NOTE: For new designs, we recommend IR's new products IR2153 and IR21531)

# SELF-OSCILLATING HALF-BRIDGE DRIVER

#### **Features**

- Floating channel designed for bootstrap operation Fully operational to +600V Tolerant to negative transient voltage dV/dt immune

- Undervoltage lockout

- Programmable oscillator frequency

$$f = \frac{1}{1.4 \times (\mathsf{R}_{\mathsf{T}} + 75\Omega) \times \mathsf{C}_{\mathsf{T}}}$$

- Matched propagation delay for both channels

- Low side output in phase with RT

#### Description

The IR2151 is a high voltage, high speed, self-oscillating power MOSFET and IGBT driver with both high and low side referenced output channels. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. The front end features a programmable oscillator which is similar to the 555 timer. The output drivers feature a high pulse current buffer stage and an internal deadtime designed for minimum driver cross-conduction. Propagation delays for the two channels are matched to simplify use in 50% duty cycle applications. The floating channel can be used to drive an N-channel power MOSFET or IGBT in the high side configuration that operates off a high voltage rail up to 600 volts.

#### **Product Summary**

| VOFFSET            | 600V max.       |

|--------------------|-----------------|

| Duty Cycle         | 50%             |

| I <sub>O</sub> +/- | 100 mA / 210 mA |

| Vout               | 10 - 20V        |

| Deadtime (typ.)    | 1.2 µs          |

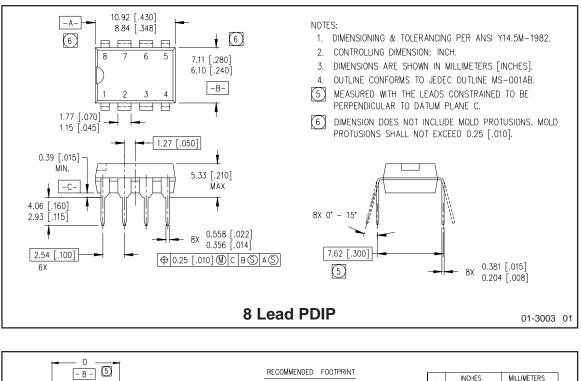

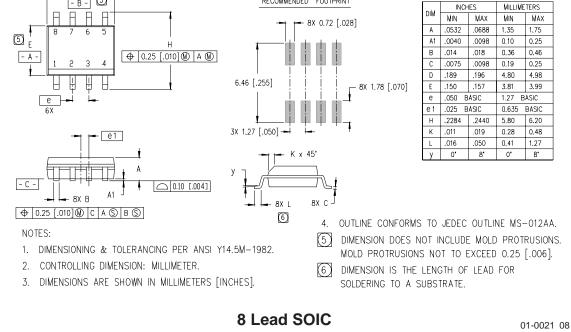

#### Packages

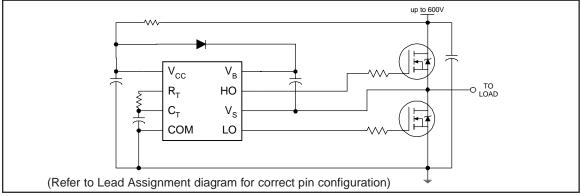

## **Typical Connection**

# IR2151

# International

#### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol              | Definition                                         |                                     | Min.                 | Max.                  | Units |

|---------------------|----------------------------------------------------|-------------------------------------|----------------------|-----------------------|-------|

| VB                  | High side floating supply voltage                  |                                     | -0.3                 | 625                   |       |

| Vs                  | High side floating supply offset voltage           |                                     | V <sub>B</sub> - 25  | V <sub>B</sub> + 0.3  | 1     |

| V <sub>HO</sub>     | High side floating output voltage                  |                                     | V <sub>S</sub> - 0.3 | V <sub>B</sub> +0.3   |       |

| VLO                 | Low side output voltage                            |                                     | -0.3                 | V <sub>CC</sub> + 0.3 | ] ,/  |

| V <sub>RT</sub>     | R <sub>T</sub> voltage                             |                                     | -0.3                 | V <sub>CC</sub> + 0.3 | V     |

| V <sub>CT</sub>     | C <sub>T</sub> voltage                             |                                     | -0.3                 | V <sub>CC</sub> +0.3  | ]     |

| ICC                 | Supply current (note 1)                            |                                     | _                    | 25                    | mA    |

| I <sub>RT</sub>     | R <sub>T</sub> output current                      |                                     | -5                   | 5                     |       |

| dV <sub>s</sub> /dt | Allowable offset supply voltage transient          |                                     | _                    | 50                    | V/ns  |

| PD                  | Package power dissipation @ $T_A \le +25^{\circ}C$ | (8 lead DIP)                        | _                    | 1.0                   | w     |

|                     |                                                    | (8 lead SOIC)                       | _                    | 0.625                 |       |

| R <sub>0JA</sub>    | Thermal resistance, junction to ambient            | (8 lead DIP)                        | _                    | 125                   | °C/W  |

|                     |                                                    | (8 lead SOIC)                       | _                    | 200                   | 0/10  |

| TJ                  | Junction temperature                               |                                     |                      | 150                   |       |

| Ts                  | Storage temperature                                |                                     | -55                  | 150                   | ] °C  |

| TL                  | Lead temperature (soldering, 10 seconds)           | temperature (soldering, 10 seconds) |                      | 300                   |       |

#### **Recommended Operating Conditions**

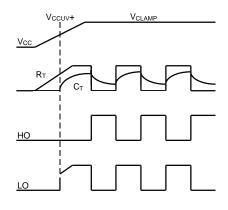

The input/output logic timing diagram is shown in figure 1. For proper operation the device should be used within the recommended conditions. The  $V_S$  offset rating is tested with all supplies biased at 15V differential.

| Symbol          | Definition                                 | Min.    | Max.            | Units |

|-----------------|--------------------------------------------|---------|-----------------|-------|

| VB              | High side sloating supply absolute voltage | Vs + 10 | Vs + 20         |       |

| Vs              | High side floating supply offset voltage   | —       | 600             | .,    |

| V <sub>HO</sub> | High side floating output voltage          | VS      | VB              | V     |

| V <sub>LO</sub> | Low side output voltage                    | 0       | V <sub>CC</sub> |       |

| lcc             | Supply current (note 1)                    | —       | 5               | mA    |

| T <sub>A</sub>  | Ambient temperature                        | -40     | 125             | °C    |

Note 1: Because of the IR2151's application specificity toward off-line supply systems, this IC contains a zener clamp structure between the chip V<sub>CC</sub> and COM which has a nominal breakdown voltage of 15.6V. Therefore, the IC supply voltage is normally derived by forcing current into the supply lead (typically by means of a high value resistor connected between the chip V<sub>CC</sub> and the rectified line voltage and a local decoupling capacitor from V<sub>CC</sub> to COM) and allowing the internal zener clamp circuit to determine the nominal supply voltage. Therefore, this circuit should not be driven by a DC, low impedance power source of greater than V<sub>CLAMP</sub>.

# UC Mall.co

# International **tor** Rectifier

# IR2151

## **Dynamic Electrical Characteristics**

$V_{BIAS}$  (V\_{CC}, V\_{BS}) = 12V, C\_L = 1000 pF and  $T_A$  = 25°C unless otherwise specified.

| Symbol         | Definition                | Min. | Тур. | Max. | Units | <b>Test Conditions</b> |

|----------------|---------------------------|------|------|------|-------|------------------------|

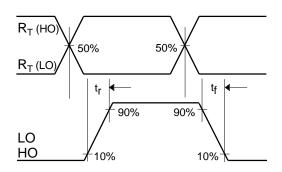

| tr             | Turn-on rise time         | —    | 80   | 120  |       |                        |

| t <sub>f</sub> | Turn-off fall time        | —    | 40   | 70   | ns    |                        |

| DT             | Deadtime                  | 0.50 | 1.20 | 2.25 | μs    |                        |

| D              | R <sub>T</sub> duty cycle | 48   | 50   | 52   | %     |                        |

#### **Static Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 12V,  $C_L$  = 1000 pF,  $C_T$  = 1 nF and  $T_A$  = 25°C unless otherwise specified. The  $V_{IN}$ ,  $V_{TH}$  and  $I_{IN}$  parameters are referenced to COM. The  $V_O$  and  $I_O$  parameters are referenced to COM and are applicable to the respective output leads: HO or LO.

| Symbol             | Definition                                                            | Min. | Тур.  | Max. | Units | <b>Test Conditions</b>                     |

|--------------------|-----------------------------------------------------------------------|------|-------|------|-------|--------------------------------------------|

| fosc               | Oscillator frequency                                                  | 19.4 | 20.0  | 20.6 | kHz   | R <sub>T</sub> = 35.7 kΩ                   |

|                    |                                                                       | 94   | 100   | 106  | KHZ   | R <sub>T</sub> = 7.04 kΩ                   |

| VCLAMP             | V <sub>CC</sub> zener shunt clamp voltage                             | 14.4 | 15.6  | 16.8 |       | $I_{CC} = 5 \text{ mA}$                    |

| V <sub>CT+</sub>   | 2/3 V <sub>CC</sub> threshold                                         | 7.8  | 8.0   | 8.2  | V     |                                            |

| V <sub>CT-</sub>   | 1/3 V <sub>CC</sub> threshold                                         | 3.8  | 4.0   | 4.2  |       |                                            |

| VCTUV              | C <sub>T</sub> undervoltage lockout                                   | _    | 20    | 50   |       | 2.5V <v<sub>CC<v<sub>CCUV+</v<sub></v<sub> |

| V <sub>RT+</sub>   | $R_T$ high level output voltage, $V_{CC}$ - $R_T$                     | _    | 0     | 100  |       | I <sub>RT</sub> = -100 μA                  |

|                    |                                                                       | —    | 200   | 300  |       | I <sub>RT</sub> = -1 mA                    |

| V <sub>RT-</sub>   | R <sub>T</sub> Low Level Output Voltage                               | -    | 20    | 50   |       | I <sub>RT</sub> = 100 μA                   |

|                    |                                                                       | —    | 200   | 300  | mV    | I <sub>RT</sub> = 1 mA                     |

| V <sub>RTUV</sub>  | R <sub>T</sub> Undervoltage Lockout, V <sub>CC</sub> - R <sub>T</sub> | _    | 0     | 100  |       | 2.5V <v<sub>CC<v<sub>CCUV+</v<sub></v<sub> |

| VOH                | High Level Output Voltage, V <sub>BIAS</sub> - V <sub>O</sub>         | _    | _     | 100  |       | $I_{O} = 0A$                               |

| V <sub>OL</sub>    | Low Level Output Voltage, VO                                          | _    | -     | 100  |       | $I_{O} = 0A$                               |

| I <sub>LK</sub>    | Offset Supply Leakage Current                                         | _    | _     | 50   |       | $V_B = V_S = 600V$                         |

| I <sub>QBS</sub>   | Quiescent V <sub>BS</sub> Supply Current                              | _    | 10    | 50   | μA    |                                            |

| IQCC               | Quiescent V <sub>CC</sub> Supply Current                              | _    | 400   | 950  | μ     |                                            |

| ICT                | C <sub>T</sub> Input Current                                          | -    | 0.001 | 1.0  |       |                                            |

| V <sub>CCUV+</sub> | V <sub>CC</sub> Supply Undervoltage Positive Going<br>Threshold       | 7.7  | 8.4   | 9.2  | V     |                                            |

| V <sub>CCUV-</sub> | V <sub>CC</sub> Supply Undervoltage Negative Going<br>Threshold       | 7.4  | 8.1   | 8.9  | v     |                                            |

| Vссиvн             | V <sub>CC</sub> Supply Undervoltage Lockout Hysteresis                | 200  | 500   | _    | mV    |                                            |

| I <sub>O+</sub>    | Output High Short Circuit Pulsed Current                              | 100  | 125   | _    | mA    | $V_{O} = 0V$                               |

| I <sub>O-</sub>    | Output Low Short Circuit Pulsed Current                               | 210  | 250   | _    | 111/4 | V <sub>O</sub> = 15V                       |

# IR2151

# International **tor** Rectifier

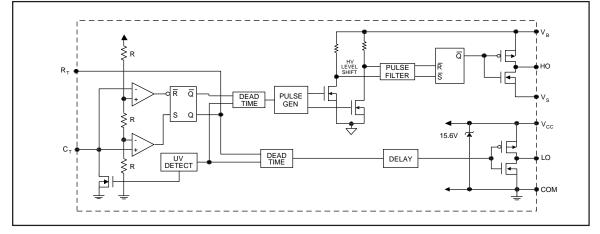

# **Functional Block Diagram**

## **Lead Definitions**

| Symbol          | Description                                                                                      |  |

|-----------------|--------------------------------------------------------------------------------------------------|--|

| R <sub>T</sub>  | Oscillator timing resistor input, in phase with LO for normal IC operation                       |  |

| CT              | Oscillator timing capacitor input, the oscillator frequency according to the following equation: |  |

|                 | $f = \frac{1}{1.4 \times (R_{T} + 75\Omega) \times C_{T}}$                                       |  |

|                 | where $75\Omega$ is the effective impedance of the R <sub>T</sub> output stage                   |  |

| VB              | High side floating supply                                                                        |  |

| НО              | High side gate drive output                                                                      |  |

| VS              | High side floating supply return                                                                 |  |

| V <sub>CC</sub> | Low side and logic fixed supply                                                                  |  |

| LO              | Low side gate drive output                                                                       |  |

| COM             | Low side return                                                                                  |  |

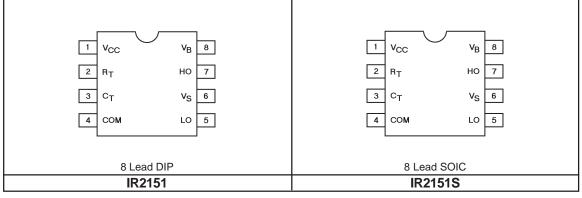

## Lead Assignments

# UC Mall.co 友进芯城

**IR2151**

# International **ICR** Rectifier

# IR2151

International

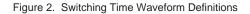

Figure 1. Input/Output Timing Diagram

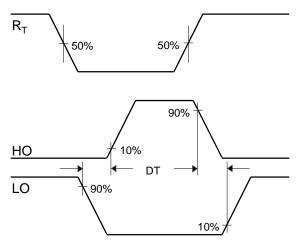

Figure 3. Deadtime Waveform Definitions

International

WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105 http://www.irf.com/ Data and specifications subject to change without notice. 3/30/2001