# EN6360QA 8A PowerSoC

# Step-Down DC-DC Switching Converter with Integrated Inductor

#### **DESCRIPTION**

The EN6360QA is an Intel® Enpirion® Power System on a Chip (PowerSoC) DC-DC converter. It integrates the inductor, MOSFET switches, small-signal circuits and compensation in an advanced 8mm x 11mm x 3mm 68-pin QFN package.

The EN6360QA is AEC-Q100 qualified for automotive applications and is specifically designed to meet the precise voltage and fast transient requirements of high-performance, low-power processor, DSP, FPGA, memory boards and system level applications in distributed power architecture. The EN6360QA features switching frequency synchronization with an external clock or other EN6360QAs for parallel operation. Other features include precision enable threshold, pre-bias monotonic start-up, and programmable soft-start.

Intel Enpirion Power Solutions significantly help in system design and productivity by offering greatly simplified board design, layout and manufacturing requirements. In addition, a reduction in the number of components required for the complete power solution helps to enable an overall system cost saving.

All Enpirion products are RoHS compliant and lead-free manufacturing environment compatible.

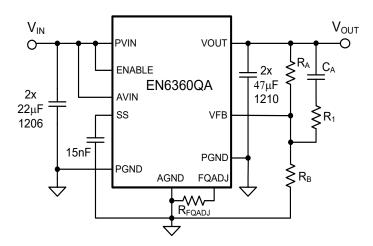

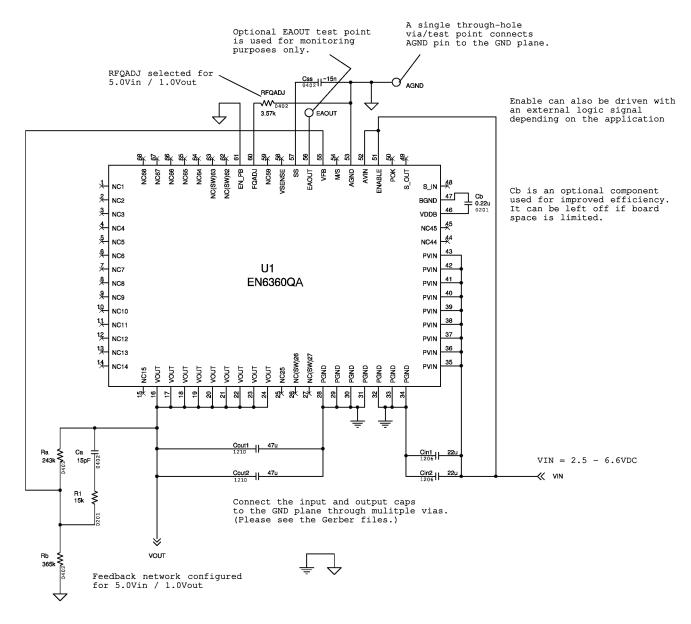

Figure 1: Simplified Applications Circuit

#### **FEATURES**

- High Efficiency (Up to 96%)

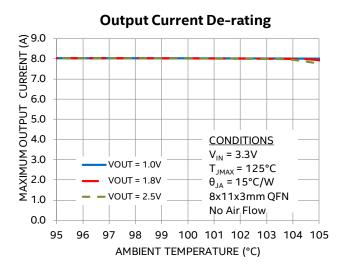

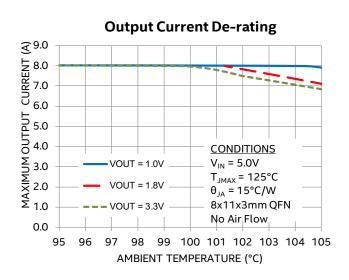

- -40°C to +105°C Ambient Temperature Range

- AEC-Q100 Qualified for Automotive Applications

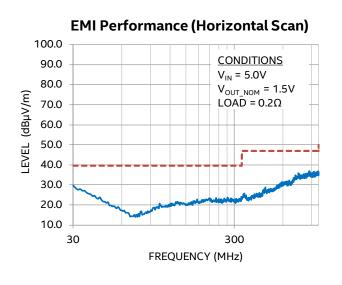

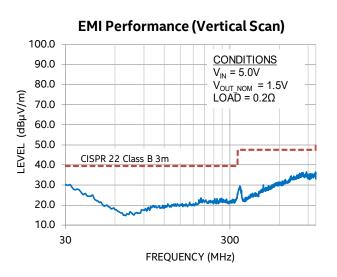

- CISPR 25 §6.6 / ISO11452-5 Compliant

- Excellent Ripple and EMI Performance

- Up to 8A Continuous Operating Current

- Input Voltage Range (2.5V to 6.6V)

- Frequency Synchronization (Clock or Primary)

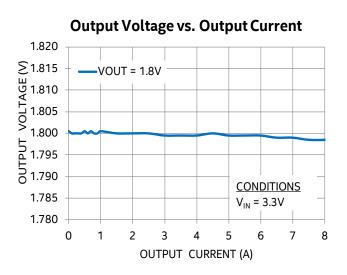

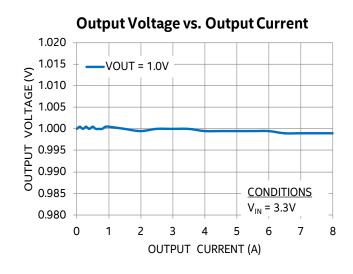

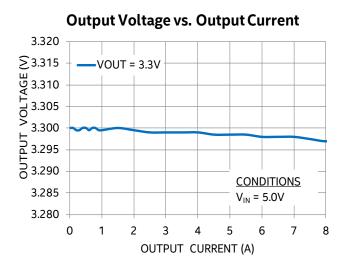

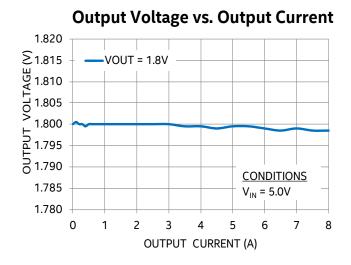

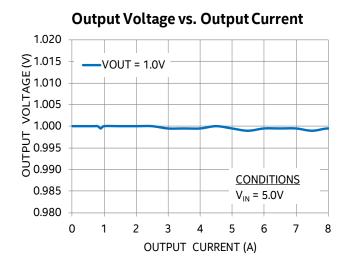

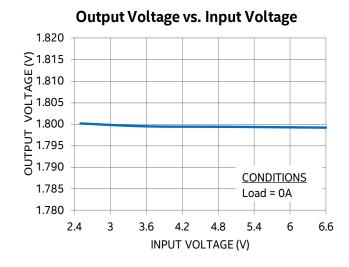

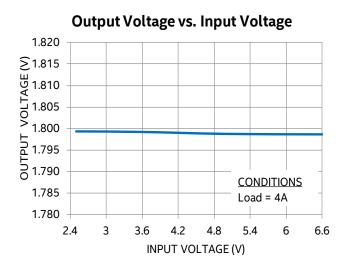

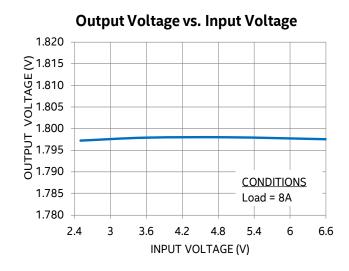

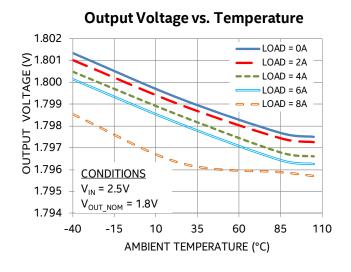

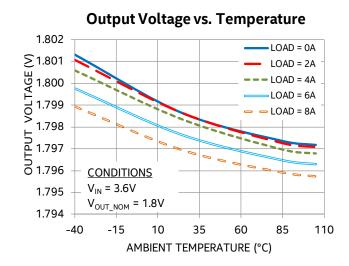

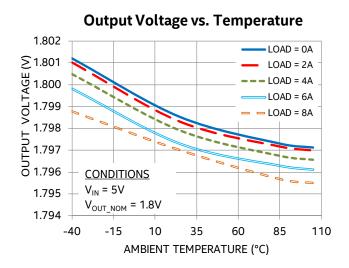

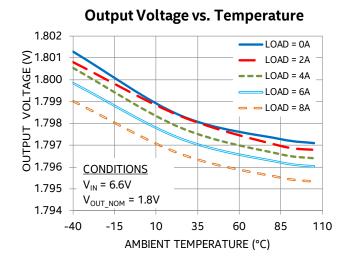

- 2% V<sub>OUT</sub> Accuracy (Over Line/Load/Temperature)

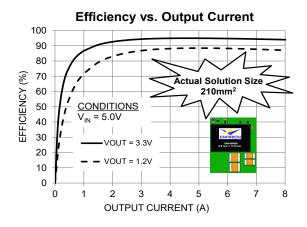

- Optimized Total Solution Size (210mm²)

- Precision Enable Threshold for Sequencing

- Programmable Soft-Start

- Master/Slave Configuration for Parallel Operation

- Thermal Shutdown, Over-Current, Short Circuit, and Under-Voltage Protection

- RoHS Compliant, MSL Level 3, 260°C Reflow

#### **APPLICATIONS**

- Automotive Applications

- Point of Load Regulation for Low-Power, ASICs Multi-Core and Communication Processors, DSPs, FPGAs and Distributed Power Architectures

- Beat Frequency/Noise Sensitive Applications

Figure 2: Highest Efficiency in Smallest Solution Size

#### ORDERING INFORMATION

| Part Number  | Package Markings | T <sub>J</sub> Rating Package Description     |      |

|--------------|------------------|-----------------------------------------------|------|

| EN6360QA     | EN6360QA         | -40°C to +125°C 68-pin (8mm x 11mm x 3mm) QFN |      |

| EVB-EN6360QA | EN6360QA         | QFN Evaluation B                              | oard |

Packing and Marking Information: https://www.inel.com/support/quality-and-reliability/packing.html

#### PIN FUNCTIONS

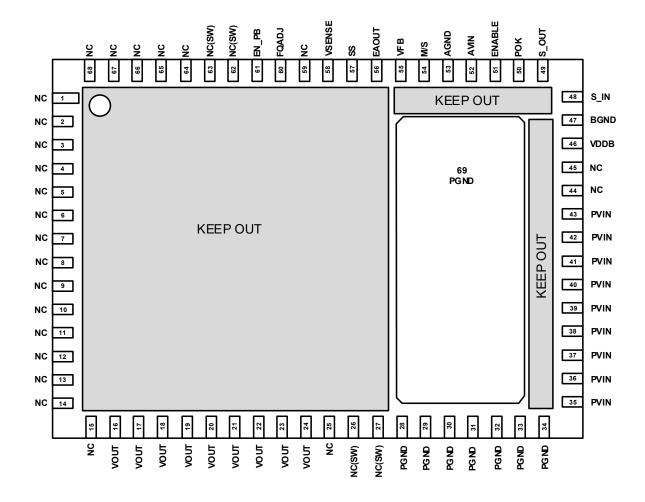

Figure 3: Pin Diagram (Top View)

**NOTE A**: NC pins are not to be electrically connected to each other or to any external signal, ground, or voltage. However, they must be soldered to the PCB. Failure to follow this guideline may result in part malfunction or damage.

**NOTE B**: Shaded area highlights exposed metal below the package that is not to be mechanically or electrically connected to the PCB. Refer to Figure 11 for details.

**NOTE C**: White 'dot' on top left is pin 1 indicator on top of the device package.

# **PIN DESCRIPTIONS**

| PIN                                  | NAME   | TYPE    | FUNCTION                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-15,<br>25, 44-<br>45, 59,<br>64-68 | NC     | -       | No Connect. These pins must be soldered to PCB but not electrically connected to each other or to any external signal, voltage, or ground. These pins may be connected internally. Failure to follow this guideline may result in device damage.                                                                                               |

| 16-24                                | VOUT   | Power   | Regulated converter output. Connect to the load and place output filter capacitor(s) between these pins and PGND pins. Refer to the Layout Recommendation section.                                                                                                                                                                             |

| 26, 27,<br>62, 63                    | NC(SW) | -       | No Connect. These pins are internally connected to the common switching node of the internal MOSFETs. They must be soldered to PCB but not be electrically connected to any external signal, ground, or voltage. Failure to follow this guideline may result in device damage.                                                                 |

| 28-34                                | PGND   | Ground  | Input/Output power ground. Connect to the ground electrode of the input and output filter capacitors. See VOUT and PVIN pin descriptions for more details.                                                                                                                                                                                     |

| 35-43                                | PVIN   | Power   | Input power supply. Connect to input power supply. Decouple with input capacitor to PGND pin. Refer to the Layout Recommendation section.                                                                                                                                                                                                      |

| 46                                   | VDDB   | Power   | Internal regulated voltage used for the internal control circuitry. Decouple with an optional $0.1\mu F$ capacitor to BGND for improved efficiency. This pin may be left floating if board space is limited.                                                                                                                                   |

| 47                                   | BGND   | Power   | Ground for VDDB. Refer to pin 46 description.                                                                                                                                                                                                                                                                                                  |

| 48                                   | S_IN   | Analog  | Digital input. A high level on the M/S pin will make this EN6360QA a Slave and the S_IN will accept the S_OUT signal from another EN6360QA for parallel operation. A low level on the M/S pin will make this device a Master and the switching frequency will be phase locked to an external clock. Leave this pin floating if it is not used. |

| 49                                   | S_OUT  | Analog  | Digital output. A low level on the M/S pin will make this EN6360QA a Master and the internal switching PWM signal is output on this pin. This output signal is connected to the S_IN pin of another EN6360QA device for parallel operation. Leave this pin floating if it is not used.                                                         |

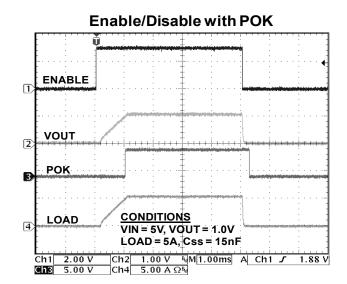

| 50                                   | РОК    | Digital | POK is a logic level high when VOUT is within -10% to +20% of the programmed output voltage ( $0.9V_{OUT\_NOM} \le V_{OUT} \le 1.2V_{OUT\_NOM}$ ). This pin has an internal pull-up resistor to AVIN with a nominal value of $94k\Omega$ .                                                                                                     |

| 51                                   | ENABLE | Analog  | Device enable pin. A high level or floating this pin enables the device while a low level disables the device. A voltage ramp from another power converter may be applied for precision enable. Refer to Power Up Sequencing                                                                                                                   |

| 52                                   | AVIN   | Power   | Analog input voltage for the control circuits. Connect this pin to the input power supply (PVIN) at a quiet point. Can also be connected to an auxiliary supply within a voltage range that is sequencing.                                                                                                                                     |

| PIN | NAME   | TYPE   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53  | AGND   | Power  | The quiet ground for the control circuits. Connect to the ground plane with a via right next to the pin.                                                                                                                                                                                                                                                                                             |

| 54  | M/S    | Analog | Ternary (three states) input pin. Floating this pin disables parallel operation. A low level configures the device as Master and a high level configures the device as a Slave. A $R_{\text{EXT}}$ resistor is recommended to pulling M/S high. Refer to Ternary Pin description in the Functional Description section for $R_{\text{EXT}}$ values. Also refer to S_IN and S_OUT pin descriptions.   |

| 55  | VFB    | Analog | This is the external feedback input pin. A resistor divider connects from the output to AGND. The mid-point of the resistor divider is connected to VFB. A feed-forward capacitor ( $C_A$ ) and resistor (R1) are required parallel to the upper feedback resistor ( $R_A$ ). The output voltage regulation is based on the VFB node voltage equal to 0.600V. For Slave devices, leave VFB floating. |

| 56  | EAOUT  | Analog | Error amplifier output. Allows for customization of the control loop. May be left floating.                                                                                                                                                                                                                                                                                                          |

| 57  | SS     | Analog | A soft-start capacitor is connected between this pin and AGND. The value of the capacitor controls the soft-start interval. Refer to Soft-Start Operation in the Functional Description section for more details.                                                                                                                                                                                    |

| 58  | VSENSE | Analog | This pin senses output voltage when the device is in pre-bias (or backfeed) mode. Connect VSENSE to VOUT when EN_PB is high or floating. Leave floating when EN_PB is low.                                                                                                                                                                                                                           |

| 60  | FQADJ  | Analog | Frequency adjust pin. This pin must have a resistor to AGND which sets the free running frequency of the internal oscillator.                                                                                                                                                                                                                                                                        |

| 61  | EN_PB  | Analog | Enable pre-bias input. When this pin is pulled high, the device will support monotonic start-up under a pre-biased load. VSENSE must be tied to VOUT for EN_PB to function. This pin is pulled high internally. Enable pre-bias feature is not available for parallel operations.                                                                                                                    |

| 69  | PGND   | Ground | Power ground thermal pad. Not a perimeter pin. Connect thermal pad to the system GND plane for heat-sinking purposes. Refer to the Layout Recommendation section.                                                                                                                                                                                                                                    |

### **ABSOLUTE MAXIMUM RATINGS**

**CAUTION**: Absolute Maximum ratings are stress ratings only. Functional operation beyond the recommended operating conditions is not implied. Stress beyond the absolute maximum ratings may impair device life. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

# **Absolute Maximum Pin Ratings**

| PARAMETER                                  | SYMBOL | MIN  | MAX                  | UNITS    |

|--------------------------------------------|--------|------|----------------------|----------|

| PVIN, AVIN, VOUT                           |        | -0.3 | 7.0                  | <b>V</b> |

| ENABLE, POK, M/S                           |        | -0.3 | V <sub>IN</sub> +0.3 | V        |

| VFB, EXTREF, EAOUT, SS, S_IN, S_OUT, FQADJ |        | -0.3 | 2.5                  | V        |

# **Absolute Maximum Thermal Ratings**

| PARAMETER                              | CONDITION                      | MIN | MAX  | UNITS |

|----------------------------------------|--------------------------------|-----|------|-------|

| Maximum Operating Junction Temperature |                                |     | +150 | °C    |

| Storage Temperature Range              |                                | -65 | +150 | °C    |

| Reflow Peak Body<br>Temperature        | (10 Sec) MSL3 JEDEC J-STD-020A |     | +260 | °C    |

# **Absolute Maximum ESD Ratings**

| PARAMETER                  | CONDITION | MIN   | MAX | UNITS |

|----------------------------|-----------|-------|-----|-------|

| HBM (Human Body Model)     |           | ±2000 |     | V     |

| CDM (Charged Device Model) |           | ±500  |     | V     |

### RECOMMENDED OPERATING CONDITIONS

| PARAMETER                           | SYMBOL           | MIN | MAX                     | UNITS |

|-------------------------------------|------------------|-----|-------------------------|-------|

| Input Voltage Range                 | $V_{IN}$         | 2.7 | 6.6                     | >     |

| Output Voltage Range                | V <sub>OUT</sub> | 0.6 | $V_{IN} - V_{DO}^{(1)}$ | V     |

| Output Current Range                | I <sub>OUT</sub> |     | 8                       | Α     |

| Operating Ambient Temperature Range | T <sub>A</sub>   | -40 | +105                    | °C    |

| Operating Junction Temperature      | ΤJ               | -40 | +125                    | °C    |

# THERMAL CHARACTERISTICS

| PARAMETER                                           | SYMBOL             | TYPICAL | UNITS |

|-----------------------------------------------------|--------------------|---------|-------|

| Thermal Shutdown                                    | T <sub>SD</sub>    | 150     | °C    |

| Thermal Shutdown Hysteresis                         | T <sub>SDHYS</sub> | 20      | °C    |

| Thermal Resistance: Junction to Ambient (0 LFM) (2) | $\theta_{JA}$      | 15      | °C/W  |

| Thermal Resistance: Junction to Case (0 LFM)        | θις                | 1.0     | °C/W  |

<sup>(1)</sup>  $V_{DO}$  (dropout voltage) is defined as ( $I_{LOAD}$  x Droput Resistance). Please refer to Electrical Characteristics Table.

<sup>(2)</sup> Based on 2oz. external copper layers and proper thermal design in line with EIJ/JEDEC JESD51-7 standard for high thermal conductivity boards.

# **ELECTRICAL CHARACTERISTICS**

NOTE:  $V_{IN}$  = 6.6V, Minimum and Maximum values are over operating ambient temperature range unless otherwise noted. Typical values are at  $T_A$  = 25°C.

| PARAMETER                                            | SYMBOL                 | TEST CONDITIONS                                                            | MIN                 | TYP             | MAX                 | UNITS |

|------------------------------------------------------|------------------------|----------------------------------------------------------------------------|---------------------|-----------------|---------------------|-------|

| Operating Input<br>Voltage                           | $V_{IN}$               |                                                                            | 2.5                 |                 | 6.6                 | V     |

| Feedback Pin Voltage                                 | $V_{FB}$               | Internal Voltage Reference at:<br>$V_{IN} = 5V$ , ILOAD = 0, $T_A = 25$ °C | 0.594               |                 | 0.606               | V     |

| VFB Pin Voltage<br>(Line, Load and<br>Temperature)   | $V_{VFB}$              | $2.5V \le V_{IN} \le 6.6V$<br>$0A \le I_{LOAD} \le 8A$                     | 0.588               | 0.600           | 0.612               | V     |

| Feedback pin Input<br>Leakage Current <sup>(3)</sup> | $I_{VFB}$              | VFB pin input leakage current                                              | -10                 |                 | 10                  | nA    |

| Shut-Down Supply<br>Current                          | I <sub>S</sub>         | Power Supply Current with ENABLE=0                                         |                     | 1.5             |                     | mA    |

| Under Voltage Lock-<br>Out – V <sub>IN</sub> Rising  | $V_{\sf UVLOR}$        | Voltage above which UVLO is not asserted                                   |                     | 2.2             |                     | V     |

| Under Voltage Lock-<br>Out – V <sub>IN</sub> Falling | $V_{\sf UVLOF}$        | Voltage below which UVLO is asserted                                       |                     | 2.1             |                     | V     |

| Drop-Out Voltage                                     | $V_{DO}$               | V <sub>INMIN</sub> - V <sub>OUT</sub> at full load                         |                     | 400             | 800                 | mV    |

| Drop-Out Resistance                                  | $R_{DO}$               | Input to output resistance                                                 |                     | 50              | 100                 | mΩ    |

| Continuous Output<br>Current                         | I <sub>OUT_SRC</sub>   | (Subject to De-rating)                                                     | 0                   |                 | 8                   | А     |

| Over Current Trip Level                              | I <sub>OCP</sub>       | Sourcing Current                                                           |                     | 16              |                     | Α     |

| Switching Frequency                                  | Fsw                    | $R_{FADJ} = 4.42 \text{ k}\Omega, V_{IN} = 5V$                             | 0.9                 | 1.2             | 1.5                 | MHz   |

| External SYNC Clock<br>Frequency Lock Range          | F <sub>PLL_LOCK</sub>  | SYNC Clock Input Frequency<br>Range                                        | 0.9*F <sub>sw</sub> | F <sub>sw</sub> | 1.1*F <sub>sw</sub> | MHz   |

| S_IN Clock Amplitude –<br>Low                        | $V_{s\_IN\_LO}$        | SYNC Clock Logic Low                                                       | 0                   |                 | 0.8                 | V     |

| S_IN Clock Amplitude –<br>High                       | $V_{\text{S\_IN\_HI}}$ | SYNC Clock Logic High                                                      | 1.8                 |                 | 2.5                 | V     |

| S_IN Clock Duty Cycle<br>(PLL)                       | $DC_{S\_INPLL}$        | M/S Pin Float or Low                                                       | 20                  |                 | 80                  | %     |

| PARAMETER                                                        | SYMBOL                   | TEST CONDITIONS                                                                                                                                                                                                                         | MIN | TYP             | MAX             | UNITS |

|------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|-----------------|-------|

| S_IN Clock Duty Cycle<br>(PWM)                                   | DC <sub>S_INPWM</sub>    | M/S Pin High                                                                                                                                                                                                                            | 10  |                 | 90              | %     |

| Pre-Bias Level                                                   | V <sub>PB</sub>          | Allowable Pre-bias as a<br>Fraction of Programmed<br>Output Voltage for Monotonic<br>start up. Minimum Pre-bias<br>Voltage = 300mV.                                                                                                     | 20  |                 | 75              | %     |

| Non-Monotonicity                                                 | $V_{PB\_NM}$             | Allowable Non-monotonicity<br>Under Pre-bias Startup                                                                                                                                                                                    |     | 100             |                 | mV    |

| V <sub>OUT</sub> Range for P <sub>OK</sub> = High <sup>(4)</sup> |                          | Range of Output Voltage as a Fraction of Programmed Value When P <sub>OK</sub> is Asserted.                                                                                                                                             | 90  |                 | 120             | %     |

| Р <sub>ок</sub> Deglitch Delay                                   |                          | Falling Edge Deglitch Delay<br>After Output Crossing 90%<br>level. F <sub>SW</sub> =1.2 MHz                                                                                                                                             |     | 213             |                 | μs    |

| V <sub>POK</sub> Logic Low level                                 |                          | With 4mA Current Sink into P <sub>OK</sub> Pin                                                                                                                                                                                          |     |                 | 0.4             | V     |

| V <sub>POK</sub> Logic high level                                |                          |                                                                                                                                                                                                                                         |     | V <sub>IN</sub> |                 | V     |

| POK Internal pull-up resistor                                    |                          |                                                                                                                                                                                                                                         |     | 94              |                 | kΩ    |

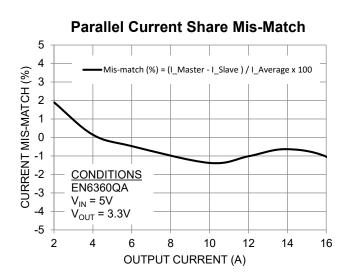

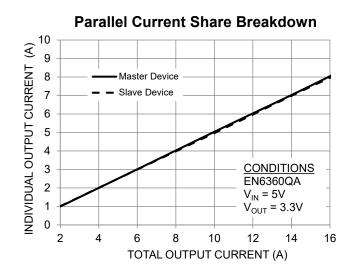

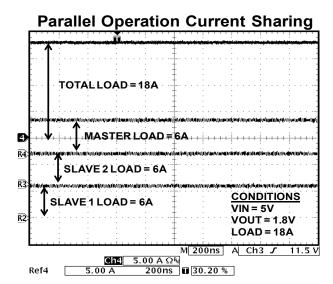

| Current Balance                                                  | $\Delta l_{	extsf{OUT}}$ | With 2 to 4 Converters in Parallel, the Difference Between Nominal and Actual Current Levels. $\Delta V_{\text{IN}} < 50 \text{mV};  R_{\text{TRACE}} < 10  \text{m}\Omega, \\ I_{\text{load}} = \#  \text{Converter*}  I_{\text{MAX}}$ |     | +/-10           |                 | %     |

| V <sub>OUT</sub> Rise Time<br>Accuracy <sup>(3)</sup>            | $\DeltaT_{RISE}$         | $t_{RISE}$ [ms] = $C_{SS}$ [nF] x 0.065;<br>10nF $\leq C_{SS} \leq 30$ nF <sup>(5)</sup> (6)                                                                                                                                            | -25 |                 | +25             | %     |

| ENABLE Logic High                                                | V <sub>ENABLE_HIGH</sub> | 2.5V ≤ V <sub>IN</sub> ≤ 6.6V                                                                                                                                                                                                           | 1.2 |                 | V <sub>IN</sub> | V     |

| ENABLE Logic Low                                                 | V <sub>ENABLE_LOW</sub>  |                                                                                                                                                                                                                                         | 0   |                 | 0.8             | V     |

| ENABLE Pin Current                                               | I <sub>EN</sub>          | VIN = 6.6V                                                                                                                                                                                                                              |     | 50              |                 | μΑ    |

| M/S Ternary Pin Logic<br>Low                                     | $V_{T-LOW}$              | Tie M/S Pin to GND                                                                                                                                                                                                                      | 0   |                 | 0.7             | V     |

| M/S Ternary Pin Logic<br>Float                                   | V <sub>T-FLOAT</sub>     | M/S Pin is Open                                                                                                                                                                                                                         | 1.1 |                 | 1.4             | V     |

| PARAMETER                                    | SYMBOL                  | TEST CONDITIONS                                                                                    | MIN | TYP | MAX       | UNITS    |

|----------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------|-----|-----|-----------|----------|

| M/S Ternary Pin Logic<br>High <sup>(7)</sup> | $V_{T-HIGH}$            | Pull Up to VIN through an external resistor R <sub>EXT</sub> . Refer to Figure 7.                  | 1.8 |     |           | <b>V</b> |

| Ternary Pin Input<br>Current                 | I <sub>TERN</sub>       | $2.5V \le V_{IN} \le 4V$ , $R_{EXT} = 15k\Omega$<br>$4V < V_{IN} \le 6.6V$ , $R_{EXT} = 51k\Omega$ |     |     | 117<br>88 | μΑ       |

| Binary Pin Logic Low<br>Threshold            | $V_{\text{B-LOW}}$      | ENABLE, S_IN                                                                                       |     |     | 0.8       | V        |

| Binary Pin Logic High<br>Threshold           | V <sub>B-HIGH</sub>     | ENABLE, S_IN                                                                                       | 1.8 |     |           | V        |

| S_OUT Low Level                              | V <sub>S_OUT_LOW</sub>  |                                                                                                    |     |     | 0.4       | V        |

| S_OUT High Level                             | V <sub>S_OUT_HIGH</sub> |                                                                                                    | 2.0 |     |           | V        |

- (3) Parameter not production tested but is guaranteed by design.

- (4) POK threshold when VOUT is rising is nominally 92%. This threshold is 90% when VOUT is falling. After crossing the 90% level, there is a 256 clock cycle ( $\sim$ 213 $\mu$ s at 1.2 MHz) delay before POK is de-asserted. The 90% and 92% levels are nominal values. Expect these thresholds to vary by  $\pm$ 3%.

- (5) Rise time calculation begins when AVIN > VUVLO and ENABLE = HIGH.

- (6) VOUT Rise Time Accuracy does not include soft-start capacitor tolerance.

- (7) M/S pin is ternary. Ternary pins have three logic levels: high, float, and low. This pin is meant to be strapped to VIN through an external resistor, strapped to GND, or left floating. The state cannot be changed while the device is on.

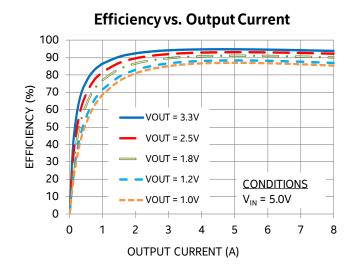

### **TYPICAL PERFORMANCE CURVES**

# **TYPICAL PERFORMANCE CURVES (CONTINUED)**

# **TYPICAL PERFORMANCE CURVES (CONTINUED)**

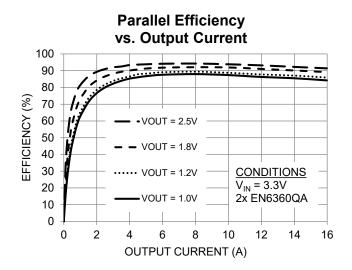

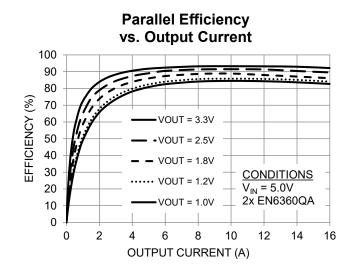

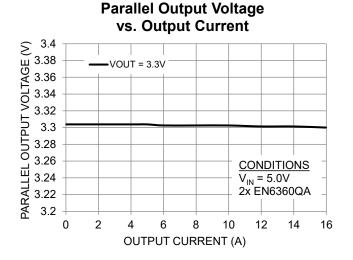

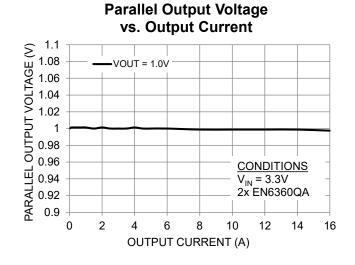

### TYPICAL PARALLEL PERFORMACE CHARACTERISTICS

#### TYPICAL PERFORMANCE CHARACTERISTICS

# **TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)**

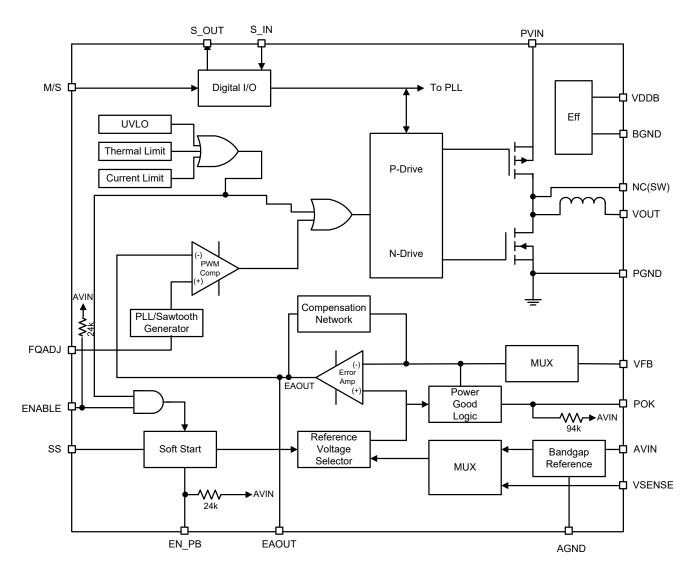

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 4: Functional Block Diagram

#### **FUNCTIONAL DESCRIPTION**

# Synchronous DC-DC Step-Down PowerSoC

The EN6360QA is a synchronous, programmable buck power supply with integrated power MOSFET switches and integrated inductor. The switching supply uses voltage mode control and a low noise PWM topology. This provides superior impedance matching to ICs processed in sub 90nm process technologies. The nominal input voltage range is 2.5 - 6.6 volts. The output voltage is programmed using an external resistor divider network. The feedback control loop incorporates a type IV voltage mode control design. Type IV voltage mode control maximizes control loop bandwidth and maintains excellent phase margin to improve transient performance. The EN6360QA is designed to support up to 8A continuous output current operation. The operating switching frequency is between 0.9MHz and 1.5MHz and enables the use of small-size input and output capacitors.

The power supply has the following features:

- Precision Enable Threshold

- Soft-Start

- Pre-bias Start-Up

- Resistor Programmable Switching Frequency

- Phase-Lock Frequency Synchronization

- Parallel Operation

- Power OK

- Over-Current/Short Circuit Protection

- Thermal Shutdown with Hysteresis

- Under-Voltage Lockout

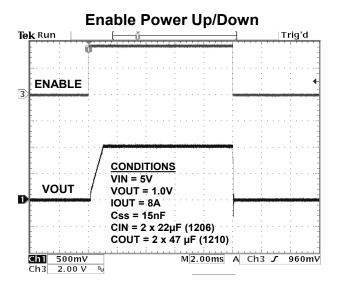

# **Precision Enable Operation**

The ENABLE threshold is a precision analog voltage rather than a digital logic threshold. A precision voltage reference and a comparator circuit are kept powered up even when ENABLE is de-asserted. The narrow voltage gap between ENABLE Logic Low and ENABLE Logic High allows the device to turn on at a precise enable voltage level. With the enable threshold pinpointed, a proper choice of soft-start capacitor helps to accurately sequence multiple power supplies in a system as desired. There is an ENABLE lockout time of 2ms that prevents the device from re-enabling immediately after it is disabled.

# **Soft-Start Operation**

The SS pin in conjunction with a small external capacitor between this pin and AGND provides a soft-start function to limit in-rush current during device power-up. When the part is initially powered up, the output voltage is gradually ramped to its final value. The gradual output ramp is achieved by increasing the reference voltage to the error amplifier. A constant current flowing into the soft-start capacitor provides the reference voltage ramp. When the voltage on the soft-start capacitor reaches 0.60V, the output has reached its programmed voltage. Once the output voltage has reached nominal voltage the soft-start capacitor will continue to charge to 1.5V (Typical). The output rise time can be controlled by the choice of soft-start capacitor value.

The rise time is defined as the time from when the ENABLE signal crosses the threshold and the input voltage crosses the upper UVLO threshold to the time when the output voltage reaches 95% of the programmed value. The rise time ( $t_{RISE}$ ) is given by the following equation:

$$t_{RISE}$$

[ms] =  $C_{ss}$  [nF] x 0.065

The rise time ( $t_{RISE}$ ) is in milliseconds and the soft-start capacitor ( $C_{SS}$ ) is in nano-Farads. The soft-start capacitor should be between 10nF and 100nF.

# **Pre-Bias Start-up**

The EN6360QA supports startup into a pre-biased load. A proprietary circuit ensures the output voltage rises up from the pre-bias value to the programmed output voltage. Start-up is guaranteed to be monotonic for pre-bias voltages in the range of 20% to 75% of the programmed output voltage with a minimum pre-bias voltage of 300mV. Outside of the 20% to 75% range, the output voltage rise will not be monotonic. The Pre-Bias feature is automatically engaged with an internal pull-up resistor.

For this feature to work properly,  $V_{IN}$  must be ramped up prior to ENABLE turning on the device. Tie VSENSE to VOUT if Pre-Bias is used. Tie EN\_PB to ground and leave VSENSE floating to disable the Pre-Bias feature. Pre-Bias is supported for external clock synchronization, but not supported for parallel operations.

# **Resistor Programmable Frequency**

The operation of the EN6360QA can be optimized by a proper choice of the  $R_{FQADJ}$  resistor. The frequency can be tuned to optimize dynamic performance and efficiency. Refer to Table 1 for recommended  $R_{FQADJ}$  values.

| Vout<br>V <sub>IN</sub> | 0.8V | 1.2V | 1.5V | 1.8V | 2.5V | 3.3V |

|-------------------------|------|------|------|------|------|------|

| 3.3V ±10%               | 3.57 | 3.57 | 4.99 | 5.49 | 5.49 | NA   |

| 5.0V ±10%               | 3.57 | 3.57 | 4.99 | 5.49 | 5.49 | 4.99 |

| 6.0V ±10%               | 3.57 | 3.57 | 4.99 | 5.49 | 5.49 | 5.49 |

Table 1: Recommended  $R_{FQADJ}$  ( $k\Omega$ )

# **Phase-Lock Operation**

The EN6360QA can be phase-locked to an external clock signal to synchronize its switching frequency. The M/S pin can be left floating or pulled to ground to allow the device to synchronize with an external clock signal using the S\_IN pin. When a clock signal is present at S\_IN, an activity detector recognizes the presence of the clock signal and the internal oscillator phase locks to the external clock. The external clock could be the system clock or the output of another EN6360QA. The phase locked clock is then output at S\_OUT. Refer to Table 2 for recommended clock frequencies.

| V <sub>OUT</sub> | 0.8V | 1.2V | 1.5V | 1.8V | 2.5V | 3.3V |

|------------------|------|------|------|------|------|------|

| 3.3V ±10%        | 1.15 | 1.15 | 1.30 | 1.35 | 1.35 | NA   |

| 5.0V ±10%        | 1.15 | 1.15 | 1.30 | 1.35 | 1.35 | 1.30 |

| 6.0V ±10%        | 1.15 | 1.15 | 1.30 | 1.35 | 1.35 | 1.35 |

Table 2: Recommended Clock fsw (MHz)±10%

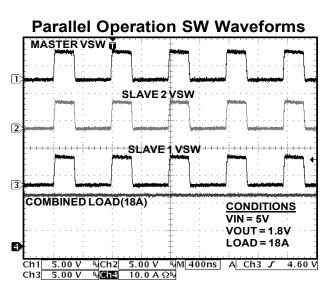

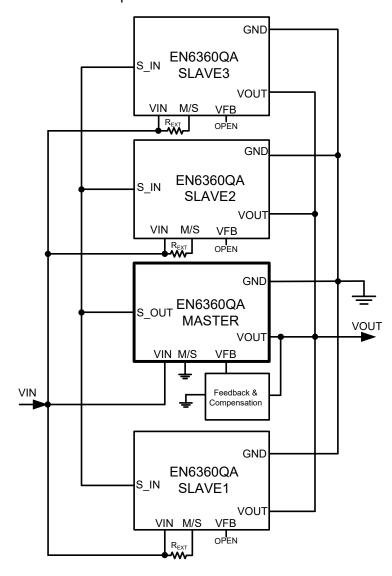

# Master / Slave (Parallel) Operation and Frequency Synchronization

Multiple EN6360QA devices may be connected in a Master/Slave configuration to handle larger load currents. The device is placed in Master mode by pulling the M/S pin low or in Slave mode by pulling M/S pin high. When the M/S pin is in float state, parallel operation is not possible. In Master mode, a version of the internal switching PWM signal is output on the S\_OUT pin. This PWM signal from the Master is fed to the Slave device at its S\_IN pin. The Slave device acts like an extension of the power FETs in the Master and inherits the PWM frequency and duty cycle. The inductor in the Slave prevents crow-bar currents from Master to Slave due to timing delays. The Master device's switching clock may be phase-locked to an external clock source or another EN6360QA to move the entire parallel operation frequency away from sensitive frequencies. The feedback network for the Slave device may be left open.

Additional Slave devices may be paralleled together with the Master by connecting the S\_OUT of the Master to the S\_IN of all other Slave devices. Refer to Figure 5 for details.

Careful attention is needed in the layout for parallel operation. The VIN, VOUT and GND of the paralleled devices should have low impedance connections between each other. Maximize the amount of copper used to connect these pins and use as many vias as possible when using multiple layers. Place the Master device between all other Slaves and closest to the point of load.

Figure 5: Master/Slave Parallel Operation Diagram POK Operation

# **POK Operation**

The POK signals that the output voltage is within the specified range. The POK signal is asserted high when the rising output voltage crosses 92% (nominal) of the programmed output voltage. If the output voltage falls outside the range of 90% to 120%, POK remains asserted for the de-glitch time (213 $\mu$ s at 1.2MHz). After the de-glitch time, POK is de-asserted. POK is also de-asserted if the output voltage exceeds 120% of the programmed output voltage.

# **Over-Current Protection (OCP)**

The current limit function is achieved by sensing the current flowing through a sense P-FET. When the sensed current exceeds the current limit, both power FETs are turned off for the rest of the switching cycle. If the over-current condition is removed, the over-current protection circuit will reenable PWM operation. If the over-current condition persists, the circuit will continue to protect the load. The OCP trip point is nominally set as specified in the Electrical Characteristics table. In the event the OCP circuit trips consistently in normal operation, the device enters a hiccup mode.

The device is disabled for 27ms and restarted with a normal soft-start. This cycle can continue indefinitely as long as the over current condition persists.

#### **Thermal Protection**

Temperature sensing circuits in the controller will disable operation when the junction temperature exceeds approximately 150°C. Once the junction temperature drops by approx 20°C, the converter will re-start with a normal soft-start.

# Input Under-Voltage Lock-Out (UVLO)

When the input voltage is below a required voltage level ( $V_{UVHI}$ ) for normal operation, the converter switching is inhibited. The lock-out threshold has hysteresis to prevent chatter. Thus when the device is operating normally, the input voltage has to fall below the lower threshold ( $V_{UVLO}$ ) for the device to stop switching.

#### APPLICATION INFORMATION

# **Output Voltage Programming and loop Compensation**

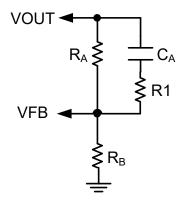

The EN6360QA output voltage is programmed using a simple resistor divider network. A phase lead capacitor plus a resistor are required for stabilizing the loop. Figure 6 shows the required components and the equations to calculate their values.

The EN6360QA output voltage is determined by the voltage presented at the VFB pin. This voltage is set by way of a resistor divider between VOUT and AGND with the midpoint going to VFB.

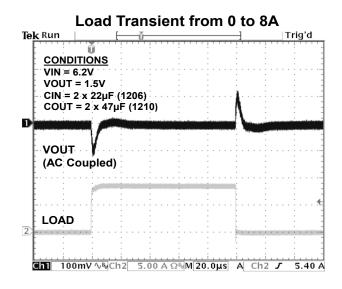

The EN6360QA uses a type IV compensation network. Most of this network is integrated. However, a phase lead capacitor and a resistor are required in parallel with upper resistor of the external feedback network (Refer to Figure 6). Total compensation is optimized for use with two  $47\mu\text{F}$  output capacitance and will result in a wide loop bandwidth and excellent load transient performance for most applications. Additional capacitance may be placed beyond the voltage sensing point outside the control loop. Voltage mode operation provides high noise immunity at light load. Furthermore, voltage mode control provides superior impedance matching to ICs processed in sub 90nm technologies.

In some cases modifications to the compensation or output capacitance may be required to optimize device performance such as transient response, ripple, or hold-up time. The EN6360QA provides the capability to modify the control loop response to allow for customization for such applications.

Figure 6: External Feedback/Compensation Network

The feedback and compensation network values depend on the input voltage and output voltage. Calculate the external feedback and compensation network values with the equations below.

$R_A[\Omega] = 48,400 \times V_{IN}[V]$

$R_B[\Omega] = (V_{FB} \times R_A) / (V_{OUT} - V_{FB}) [V]$

$V_{FB} = 0.6V \text{ nominal}$

\*Round RA & RB to closest standard value

$C_A[F] = 3.83 \times 10^{-6} / R_A[\Omega]$

\*Round C<sub>A</sub> down to closest standard value

$R1 = 15k\Omega$

The feedback resistor network should be sensed at the last output capacitor close to the device. Keep the trace to VFB pin as short as possible. Whenever possible, connect  $R_B$  directly to the AGND pin instead of going through the GND plane.

# **Input Capacitor Selection**

The EN6360QA has been optimized for use with two  $22\mu F$  1206 case size input capacitors. Low ESR ceramic capacitors are required with X7R dielectric formulation. Y5V or equivalent dielectric formulations must not be used as these lose capacitance with frequency, temperature and bias voltage.

In some applications, lower value ceramic capacitors may be needed in parallel with the larger capacitors in order to provide high frequency decoupling. The capacitors shown in the table below are typical input capacitors. Other capacitors with similar characteristics may also be used.

| Description             | MFG         | P/N               |  |

|-------------------------|-------------|-------------------|--|

| 22μF, 10V, X7R,<br>1206 | Murata      | GRM31CR71A226ME15 |  |

|                         | Taiyo Yuden | LMK316AB7226KL-TR |  |

|                         | AVX         | 1206ZC226KAT2A    |  |

**Table 3: Recommended Input Capacitors**

# **Output Capacitor Selection**

The EN6360QA has been optimized for use with two 47 $\mu$ F 1210 case size output capacitors. Low ESR, X7R ceramic capacitors are recommended as the primary choice. Y5V or equivalent dielectric formulations must not be used as these lose capacitance with frequency, temperature and bias voltage. The capacitors shown in the Recommended Output Capacitors table are typical output capacitors. Other capacitors with similar characteristics may also be used. Additional bulk capacitance from 100 $\mu$ F to 1000 $\mu$ F may be placed beyond the voltage sensing point outside the control loop. The external compensation (CA, R1) does not need to be modified. This additional bulk capacitance should have a minimum ESR of 6m $\Omega$  to ensure stable operation. Most tantalum capacitors will have more than 6m $\Omega$  of ESR and may be used without special care. Adding distance in layout may help increase the ESR between the feedback sense point and the bulk capacitors.

Description **MFG** P/N Murata GRM32ER70J476ME20 47μF, 6.3V, X7R, 1210 Taiyo Yuden LMK325B7476KM-TR Murata GRM31CR71A226ME15 22μF, 10V, Taiyo Yuden LMK316AB7226KL-TR X7R, 1206 AVX 1206ZC226KAT2A Murata GRM21BR71A106KE51 10μF, 10V, LMK212AB7106MG-T Taiyo Yuden X7R, 0805 AVX 0805ZC106KAT2A

**Table 4: Recommended Output Capacitors**

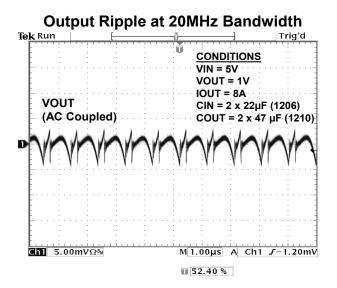

Output ripple voltage is primarily determined by the aggregate output capacitor impedance. Placing multiple capacitors in parallel reduces the impedance and hence will result in lower ripple voltage.

$$\frac{1}{Z_{Total}} = \frac{1}{Z_1} + \frac{1}{Z_2} + \dots + \frac{1}{Z_n}$$

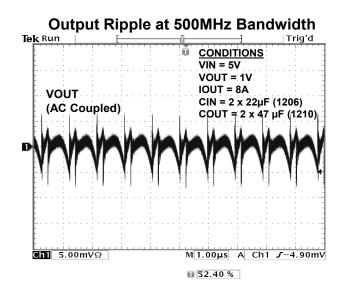

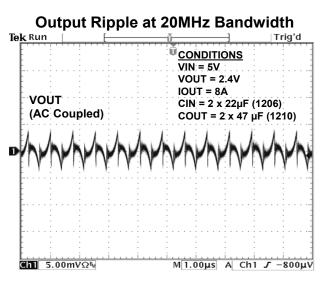

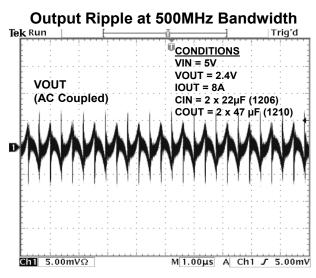

**Table 5: Typical Ripple Voltages**

| Output Capacitor Configuration | Typical Output Ripple (mVp-p) |

|--------------------------------|-------------------------------|

| 2 x 47 μF                      | <10mV                         |

<sup>&</sup>lt;sup>†</sup> 20 MHz bandwidth limit measured on Evaluation Board

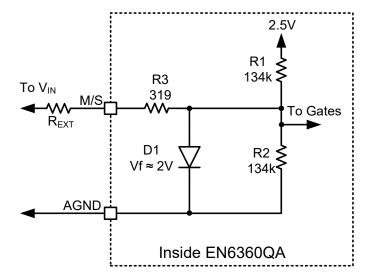

# M/S - Ternary Pin

M/S is a ternary pin. This pin can assume 3 states – A low state (0V to 0.7V), a high state (1.8V to VIN) and a float state (1.1V to 1.4V). Device operation is controlled by the state of the pin. The pins may be pulled to ground or left floating without any special care. When pulling high to VIN, a series resistor is recommended. The resistor value may be optimized to reduce the current drawn by the pin. The resistance should not be too high as in that case the pin may not recognize the high state. The recommend resistance ( $R_{\text{EXT}}$ ) value is given in the following table.

Table 6: Recommended R<sub>EXT</sub> Resistor

| V <sub>IN</sub> (V) | I <sub>MAX</sub> (μA) | R <sub>EXT</sub> (kΩ) |  |

|---------------------|-----------------------|-----------------------|--|

| 2.5 – 4.0           | 117                   | 15                    |  |

| 4.0 – 6.6           | 88                    | 51                    |  |

Figure 7: Selection of REXT to Connect M/S pin to VIN

Table 7: M/S (Master/Slave) Pin States

| M/S Pin                    | Function                                                                                                                                                                                                                                                   |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low<br>(0V to 0.7V)        | M/S pin is pulled to ground directly. This is the Master mode. Switching PWM phase will lock onto S_IN external clock if a signal is available. S_OUT outputs a version of the internal switching PWM signal.                                              |

| Float<br>(1.1V to<br>1.4V) | M/S pin is left floating. Parallel operation is not feasible. Switching PWM phase will lock onto S_IN external clock if a signal is available. S_OUT outputs a version of the internal switching PWM signal.                                               |

| High<br>(>1.8V)            | M/S pin is pulled to VIN with $R_{\text{EXT}}$ . This is the Slave mode. The S_IN signal of the Slave should connect to the S_OUT of the Master device. This signal synchronizes the switching frequency and duty cycle of the Master to the Slave device. |

# **Power-Up Sequencing**

During power-up, ENABLE should not be asserted before PVIN, and PVIN should not be asserted before AVIN. Tying all three pins together meets these requirements.

#### THERMAL CONSIDERATIONS

Thermal considerations are important power supply design facts that cannot be avoided in the real world. Whenever there are power losses in a system, the heat that is generated by the power dissipation needs to be accounted for. The intel Enpirion PowerSoC helps alleviate some of those concerns.

The intel Enpirion EN6360QA DC-DC converter is packaged in an 8x11x3mm 68-pin QFN package. The QFN package is constructed with copper lead frames that have exposed thermal pads. The exposed thermal pad on the package should be soldered directly on to a copper ground pad on the printed circuit board (PCB) to act as a heat sink. The recommended maximum junction temperature for continuous operation is 125°C. Continuous operation above 125°C may reduce long-term reliability. The device has a thermal overload protection circuit designed to turn off the device at an approximate junction temperature value of 150°C.

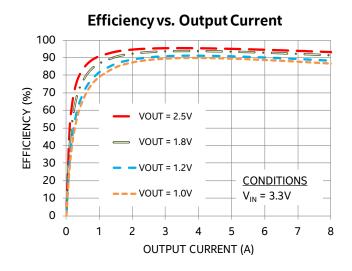

The following example and calculations illustrate the thermal performance of the EN6360QA.

#### Example:

$V_{IN} = 5V$

$V_{OUT} = 3.3V$

$I_{OUT} = 8A$

First calculate the output power.

$P_{OUT} = 3.3 V \times 8A = 26.4 W$

Next, determine the input power based on the efficiency ( $\eta$ ) shown in Figure 8.

#### **Efficiency vs. Output Current** 100 90 94% 80 70 EFFICIENCY (%) 60 50 40 30 20 **CONDITIONS** VOUT = 3.3V10 $V_{IN} = 5.0V$ 0 2 3 6 7 8 0 1 4 5 **OUTPUT CURRENT (A)**

**Figure 8: Efficiency vs. Output Current**

For

$$V_{IN}$$

= 5V,  $V_{OUT}$  = 3.3V at 8A,  $\eta \approx 94\%$

$$\eta = P_{OUT} / P_{IN} = 94\% = 0.94$$

$$P_{IN} = P_{OUT} / \eta$$

$$P_{IN} \approx 26.4W / 0.94 \approx 28.085W$$

The power dissipation ( $P_D$ ) is the power loss in the system and can be calculated by subtracting the output power from the input power.

$$P_D = P_{IN} - P_{OUT}$$

$$\approx 28.085W - 26.4W \approx 1.685W$$

With the power dissipation known, the temperature rise in the device may be estimated based on the theta JA value ( $\theta_{JA}$ ). The  $\theta_{JA}$  parameter estimates how much the temperature will rise in the device for every watt of power dissipation. The EN6360QA has a  $\theta_{JA}$  value of 15 °C/W without airflow.

Determine the change in temperature ( $\Delta T$ ) based on  $P_D$  and  $\theta_{JA}$ .

$$\Delta T = P_D \times \theta_{JA}$$

$$\Delta T \approx 1.685 \text{W x } 15^{\circ}\text{C/W} = 25.28^{\circ}\text{C} \approx 25.3^{\circ}\text{C}$$

The junction temperature ( $T_{J}$ ) of the device is approximately the ambient temperature ( $T_{A}$ ) plus the change in temperature. We assume the initial ambient temperature to be 25°C.

$$T_J = T_A + \Delta T$$

$$T_1 \approx 25^{\circ}\text{C} + 25.3^{\circ}\text{C} \approx 50.3^{\circ}\text{C}$$

With 1.685W dissipated into the device, the T<sub>J</sub> will be 50.3°C.

The maximum operating junction temperature ( $T_{JMAX}$ ) of the device is 125°C, so the device can operate at a higher ambient temperature. The maximum ambient temperature ( $T_{AMAX}$ ) allowed can be calculated.

$$T_{AMAX} = T_{JMAX} - P_D \times \theta_{JA}$$

$\approx 125^{\circ}C - 25.3^{\circ}C \approx 99.7^{\circ}C$

The ambient temperature can actually rise by another 74.7°C, bringing it to 99.7°C before the device will reach  $T_{JMAX}$ . This indicates that the EN6360QA can support the full 8A output current range up to approximately 99.7°C ambient temperature given the input and output voltage conditions. Note that the efficiency will be slightly lower at higher temperatures and this estimate will be slightly lower.

#### **ENGINEERING SCHEMATIC**

**Figure 9: Engineering Schematic with Engineering Notes**

#### LAYOUT RECOMMENDATIONS

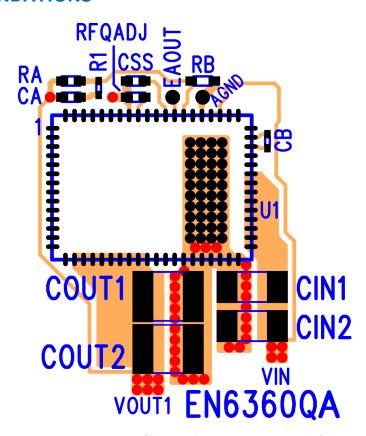

Figure 10: Top Layout with Critical Components Only (Top View)

This layout only shows the critical components and top layer traces for minimum footprint in single-supply mode with ENABLE tied to AVIN. Alternate circuit configurations & other low-power pins need to be connected and routed according to customer application. Please see the Gerber files at <a href="http://www.intel.com/enpirion">http://www.intel.com/enpirion</a> for details on all layers.

**Recommendation 1**: Input and output filter capacitors should be placed on the same side of the PCB, and as close to the EN6360QA package as possible. They should be connected to the device with very short and wide traces. Do not use thermal reliefs or spokes when connecting the capacitor pads to the respective nodes. The +V and GND traces between the capacitors and the EN6360QA should be as close to each other as possible so that the gap between the two nodes is minimized, even under the capacitors.

**Recommendation 2**: The PGND connections for the input and output capacitors on layer 1 need to have a slit between them in order to provide some separation between input and output current loops.

**Recommendation 3**: The system ground plane should be the first layer immediately below the surface layer. This ground plane should be continuous and un-interrupted below the converter and the input/output capacitors.

**Recommendation 4**: The thermal pad underneath the component must be connected to the system ground plane through as many vias as possible. The drill diameter of the vias should be 0.33mm, and the vias must have at least 1 oz. copper plating on the inside wall, making the finished hole size around 0.20-0.26mm. Do not use thermal reliefs or spokes to connect the vias to the ground plane. This connection provides the path for heat dissipation from the converter.

**Recommendation 5**: Multiple small vias (the same size as the thermal vias discussed in recommendation 4) should be used to connect ground terminal of the input capacitor and output capacitors to the system ground plane. It is preferred to put these vias along the edge of the GND copper closest to the +V copper. These vias connect the input/output filter capacitors to the GND plane, and help reduce parasitic inductances in the input and output current loops.

**Recommendation 6**: AVIN is the power supply for the small-signal control circuits. It should be connected to the input voltage at a quiet point. In Figure 10 this connection is made at the input capacitor.

**Recommendation 7**: The layer 1 metal under the device must not be more than shown in Figure 10. Refer to the section regarding Exposed Metal on Bottom of Package. As with any switch-mode DC-DC converter, try not to run sensitive signal or control lines underneath the converter package on other layers.

**Recommendation 8**: The  $V_{OUT}$  sense point should be just after the last output filter capacitor. Keep the sense trace short in order to avoid noise coupling into the node.

**Recommendation 9**: Keep  $R_A$ ,  $C_A$ ,  $R_B$ , and  $R_1$  close to the VFB pin (Refer to Figure 10). The VFB pin is a high-impedance, sensitive node. Keep the trace to this pin as short as possible. Whenever possible, connect  $R_B$  directly to the AGND pin instead of going through the GND plane.

**Recommendation 10**: Follow all the layout recommendations as close as possible to optimize performance. Intel provides schematic and layout reviews for all customer designs.

### **DESIGN CONSIDERATIONS FOR LEAD-FRAME BASED MODULES**

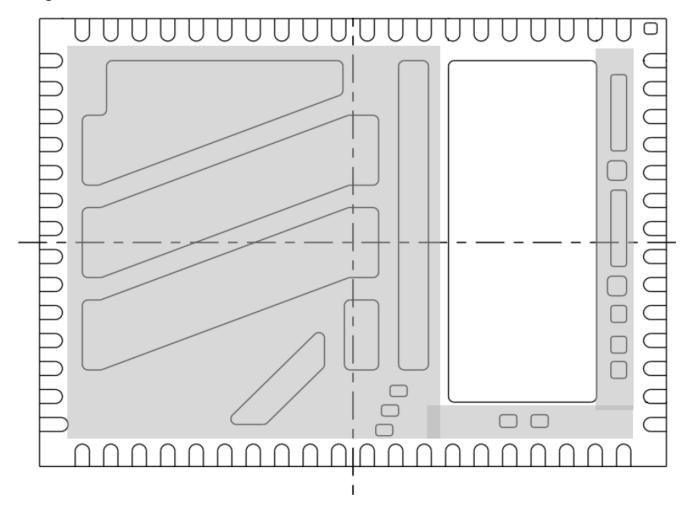

# **Exposed Metal on Bottom of Package**

Lead-frames offer many advantages in thermal performance, in reduced electrical lead resistance, and in overall foot print. However, they do require some special considerations.

In the assembly process lead frame construction requires that, for mechanical support, some of the lead-frame cantilevers be exposed at the point where wire-bond or internal passives are attached. This results in several small pads being exposed on the bottom of the package, as shown in Figure 11.

Only the thermal pad and the perimeter pads are to be mechanically or electrically connected to the PC board. The PCB top layer under the EN6360QA should be clear of any metal (copper pours, traces, or vias) except for the thermal pad. The "shaded-out" area in Figure 11 represents the area that should be clear of any metal on the top layer of the PCB. Any layer 1 metal under the shaded-out area runs the risk of undesirable shorted connections even if it is covered by soldermask.

The solder stencil aperture should be smaller than the PCB ground pad. This will prevent excess solder from causing bridging between adjacent pins or other exposed metal under the package. Please consult General Soldering Guidelines for more details and recommendations.

Figure 11: Lead-Frame exposed metal (Bottom View)

Shaded area highlights exposed metal that is not to be mechanically or electrically connected to the PCB.

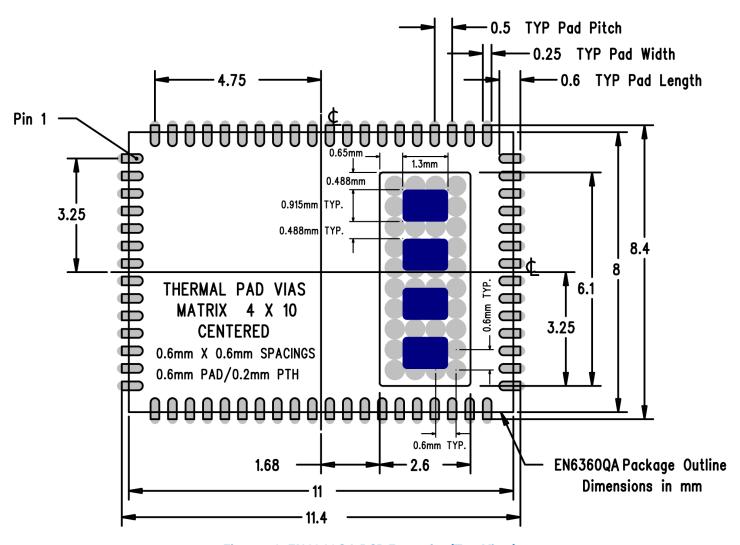

Figure 12: EN6360QA PCB Footprint (Top View)

The solder stencil aperture for the thermal pad is shown in blue and is based on Enpirion power product manufacturing specifications.

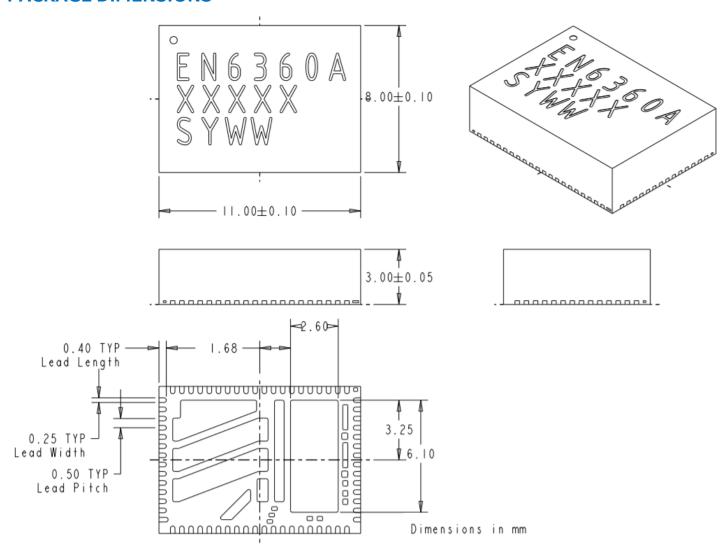

# **PACKAGE DIMENSIONS**

Figure 13: EN6360QA Package Dimensions (Bottom View)

Packing and Marking Information: https://www.intel.com/support/quality-and-reliability/packing.html

### **REVISION HISTORY**

| Rev | Date     | Change(s)                                                                         |

|-----|----------|-----------------------------------------------------------------------------------|

| Α   | Oct 2014 | Introductory production datasheet                                                 |

| В   | Jan 2017 | Changed VFB leakage current specification in the Electrical Characteristics Table |

| С   | Aug 2018 | Changed datasheet into Intel format                                               |

| D   | Dec 2018 | Updated EN6360QA Package                                                          |

#### WHERE TO GET MORE INFORMATION

For more information about Intel® and Enpirion® PowerSoCs, visit:

www.intel.com/enpirion

© 2017 Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS, and STRATIX words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Other marks and brands may be claimed as the property of others. Intel reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\* Other marks and brands may be claimed as the property of others.