### Eight Output Differential Buffer for PCI Express (50-200MHz)

### ICS9DB801C

### Description

The 9DB801C is a DB800 Version 2.0 Yellow Cover part with PCI Express support. It can be used in PC or embedded systems to provide outputs that have low cycle-to-cycle jitter (50ps), low output-to-output skew (100ps), and are PCI Express gen 1 compliant. The 9DB801C supports a 1 to 8 output configuration, taking a spread or non spread differential HCSL input from a CK410(B) main clock such as 954101 and 932S401, or any other differential HCSL pair. 9DB801C can generate HCSL or LVDS outputs from 50 to 200MHz in PLL mode or 0 to 400Mhz in bypass mode. There are two de-jittering modes available selectable through the HIGH\_BW# input pin, high bandwidth mode provides de-jittering for spread inputs and low bandwidth mode provides extra de-jittering for non-spread inputs. The SRC\_STOP#, PD#, and individual OE# real-time input pins provide completely programmable power management control.

### **Output Features**

- 8 0.7V current-mode differential output pairs

- Supports zero delay buffer mode and fanout mode

- Bandwidth programming available

### Features/Benefits

- Spread spectrum modulation tolerant, 0 to -0.5% down spread and +/- 0.25% center spread.

- Supports undriven differential outputs in PD# and SRC\_STOP# modes for power management.

- Supports polarity inversion to the output enables, SRC\_STOP and PD.

### **Key Specifications**

- Outputs cycle-cycle jitter < 50ps</li>

- Outputs skew: 50ps

- 50 200MHz operation

- Extended frequency range in bypass mode to 400 MHz

- PCI Express Gen I compliant

- Real time PLL lock detect output pin

- 48-pin SSOP/TSSOP package

- Available in RoHS compliant packaging

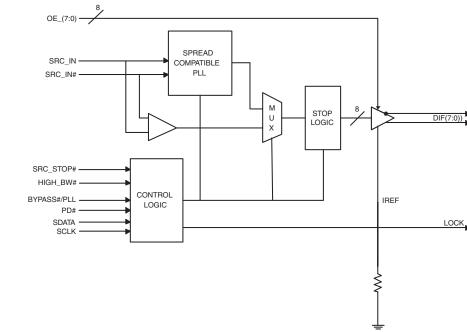

#### **Funtional Block Diagram**

Note: Polarities shown for OE\_INV = 0.

| ICS9DB801C                                                   |  |

|--------------------------------------------------------------|--|

| Eight Output Differential Buffer for PCI Express (50-200MHz) |  |

### **Pin Configuration**

| •           |                                  |                                  |           | -           |                                  |    |          |

|-------------|----------------------------------|----------------------------------|-----------|-------------|----------------------------------|----|----------|

| SRC_DIV#    | 1                                | 48                               | VDDA      | SRC_DIV#    |                                  | 48 | VDDA     |

| VDD         | 2                                | 47                               | GNDA      | VDD         | 2                                | 47 | GNDA     |

| GND         | 3                                | 46                               | IREF      | GND         | 3                                | 46 | IREF     |

| SRC_IN      | 4                                | 45                               | LOCK      | SRC_IN      | 4                                | 45 | LOCK     |

| SRC_IN#     | 5                                | 44                               | OE_7      | SRC_IN#     | 5                                | 44 | OE7#     |

| OE_0        | 6                                | 43                               | OE_4      | OE0#        | 6                                |    | OE4#     |

| OE_3        | 7                                | 42                               | DIF_7     | OE3#        |                                  | 42 | DIF_7    |

| DIF_0       | 8                                | <b>8</b> 41                      | DIF_7#    | DIF_0       | 8                                | 41 | DIF_7#   |

| DIF_0#      | 9                                | 41<br>40<br>39<br>38<br>37<br>36 | OE_INV    | DIF_0#      | 9                                | 40 | OE_INV   |

| GND         | <sup>10</sup> 5                  | <b>H</b> 39                      | VDD       | GND         | <sup>10</sup> 5                  | 39 | VDD      |

| VDD         | 11 <b>0</b>                      | <b>16</b> 38                     | DIF_6     | VDD         | 11 🙀                             | 38 | DIF_6    |

| DIF_1       | 10<br>11<br>12<br>13<br>14<br>15 | S 37                             | DIF_6#    | DIF_1       | 10<br>11<br>12<br>13<br>14<br>15 | 37 | DIF_6#   |

| DIF_1#      | 13 <b>D</b>                      | <b>Y</b> 36                      | OE_6      | DIF_1#      | <sup>13</sup> <b>6</b>           | 36 | OE6#     |

| OE_1        | 14 <b>Ö</b>                      | <b>se</b> 35                     | OE_5      | OE1#        | 14 <b>ഗ്</b>                     | 35 | OE5#     |

| OE_2        | 15 <b>O</b>                      | <b>u</b> 34                      | DIF_5     | OE2#        |                                  | 34 | DIF_5    |

| DIF_2       | 16                               | <b>34</b><br>33<br>32<br>31      | DIF_5#    | DIF_2       | 16                               |    | DIF_5#   |

| DIF_2#      | 17                               | <b>ഗ്ഗ്</b> 32                   | GND       | DIF_2#      | 17                               | 32 | GND      |

| GND         | 18                               | <b>3</b> 1                       | VDD       | GND         | 18                               | 31 | VDD      |

| VDD         | 19                               | 30                               | DIF_4     | VDD         | 19                               | 30 | DIF_4    |

| DIF_3       | 20                               | 29                               | DIF_4#    | DIF_3       |                                  |    | DIF_4#   |

| DIF_3#      | 21                               | 28                               | HIGH_BW#  | DIF_3#      | 21                               | 28 | HIGH_BW# |

| BYPASS#/PLL | 22                               | 27                               | SRC_STOP# | BYPASS#/PLL | 22                               | 27 | SRC_STOP |

| SCLK        |                                  |                                  | PD#       | SCLK        |                                  |    | PD       |

| SDATA       | 24                               | 25                               | GND       | SDATA       | 24                               | 25 | GND      |

| •           | OE_IN                            |                                  |           |             | OE_INV = <sup>·</sup>            | 1  |          |

|             | _                                |                                  |           |             |                                  |    |          |

### **Polarity Inversion Pin List Table**

|      | OE_INV    |          |  |  |  |  |

|------|-----------|----------|--|--|--|--|

| Pins | 0         | 1        |  |  |  |  |

| 6    | OE_0      | OE0#     |  |  |  |  |

| 7    | OE_3      | OE3#     |  |  |  |  |

| 14   | OE_1      | OE1#     |  |  |  |  |

| 15   | OE_2      | OE2#     |  |  |  |  |

| 26   | PD#       | PD       |  |  |  |  |

| 27   | DIF_STOP# | DIF_STOP |  |  |  |  |

| 35   | OE_5      | OE5#     |  |  |  |  |

| 36   | OE_6      | OE6#     |  |  |  |  |

| 43   | OE_4      | OE4#     |  |  |  |  |

| 44   | OE_7      | OE7#     |  |  |  |  |

| PIN # | PIN NAME    | PIN TYPE | DESCRIPTION                                                                                  |

|-------|-------------|----------|----------------------------------------------------------------------------------------------|

| 1     | SRC_DIV#    | INPUT    | Active low Input for determining SRC output frequency SRC or SRC/2. $0 = $ SRC/2, $1 = $ SRC |

| 2     | VDD         | POWER    | Power supply, nominal 3.3V                                                                   |

| 3     | GND         | POWER    | Ground pin.                                                                                  |

| 4     | SRC_IN      | INPUT    | 0.7 V Differential SRC TRUE input                                                            |

| 5     | SRC_IN#     | INPUT    | 0.7 V Differential SRC COMPLEMENTARY input                                                   |

| 6     | OE_0        | INPUT    | Active high input for enabling outputs.                                                      |

|       | 02_0        |          | 0 = tri-state outputs, 1= enable outputs                                                     |

| 7     | OE_3        | INPUT    | Active high input for enabling outputs.                                                      |

| /     |             |          | 0 = tri-state outputs, 1= enable outputs                                                     |

| 8     | DIF_0       | OUTPUT   | 0.7V differential true clock outputs                                                         |

| 9     | DIF_0#      | OUTPUT   | 0.7V differential complement clock outputs                                                   |

| 10    | GND         | POWER    | Ground pin.                                                                                  |

| 11    | VDD         | POWER    | Power supply, nominal 3.3V                                                                   |

| 12    | DIF_1       | OUTPUT   | 0.7V differential true clock outputs                                                         |

| 13    | DIF_1#      | OUTPUT   | 0.7V differential complement clock outputs                                                   |

| 14    | OE_1        | INPUT    | Active high input for enabling outputs.                                                      |

| 14    |             | INFUT    | 0 = tri-state outputs, 1= enable outputs                                                     |

| 15    |             | INPUT    | Active high input for enabling outputs.                                                      |

| 15    | OE_2        | INPUT    | 0 = tri-state outputs, 1= enable outputs                                                     |

| 16    | DIF_2       | OUTPUT   | 0.7V differential true clock outputs                                                         |

| 17    | DIF_2#      | OUTPUT   | 0.7V differential complement clock outputs                                                   |

| 18    | GND         | POWER    | Ground pin.                                                                                  |

| 19    | VDD         | POWER    | Power supply, nominal 3.3V                                                                   |

| 20    | DIF_3       | OUTPUT   | 0.7V differential true clock outputs                                                         |

| 21    | DIF_3#      | OUTPUT   | 0.7V differential complement clock outputs                                                   |

| 22    | BYPASS#/PLL | INPUT    | Input to select Bypass(fan-out) or PLL (ZDB) mode                                            |

|       |             |          | 0 = Bypass mode, 1= PLL mode                                                                 |

| 23    | SCLK        | INPUT    | Clock pin of SMBus circuitry, 5V tolerant.                                                   |

| 24    | SDATA       | I/O      | Data pin for SMBus circuitry, 5V tolerant.                                                   |

IDT<sup>™</sup>/ICS<sup>™</sup> Eight Output Differential Buffer for PCI Express (50-200MHz)

| PIN # | PIN NAME  | PIN TYPE | DESCRIPTION                                                     |

|-------|-----------|----------|-----------------------------------------------------------------|

| 25    | GND       | POWER    | Ground pin.                                                     |

|       |           |          | Asynchronous active low input pin, with 120Kohm internal pull-  |

| 26    | PD#       | INPUT    | up resistor, used to power down the device. The internal clocks |

|       |           |          | are disabled and the VCO and the crystal are stopped.           |

| 27    | SRC_STOP# | INPUT    | Active low input to stop SRC outputs.                           |

| 00    |           | INPUT    | 3.3V input for selecting PLL Band Width                         |

| 28    | HIGH_BW#  | INPUT    | 0 = High, 1 = Low                                               |

| 29    | DIF_4#    | OUTPUT   | 0.7V differential complement clock outputs                      |

| 30    | DIF_4     | OUTPUT   | 0.7V differential true clock outputs                            |

| 31    | VDD       | POWER    | Power supply, nominal 3.3V                                      |

| 32    | GND       | POWER    | Ground pin.                                                     |

| 33    | DIF_5#    | OUTPUT   | 0.7V differential complement clock outputs                      |

| 34    | DIF_5     | OUTPUT   | 0.7V differential true clock outputs                            |

| 35    | OE_5      | INPUT    | Active high input for enabling outputs.                         |

| - 30  | 0E_5      | INFUT    | 0 = tri-state outputs, 1= enable outputs                        |

| 36    |           | INPUT    | Active high input for enabling outputs.                         |

| 30    | OE_6      | INFUT    | 0 = tri-state outputs, 1= enable outputs                        |

| 37    | DIF_6#    | OUTPUT   | 0.7V differential complement clock outputs                      |

| 38    | DIF_6     | OUTPUT   | 0.7V differential true clock outputs                            |

| 39    | VDD       | POWER    | Power supply, nominal 3.3V                                      |

| 40    | OE INV    | INPUT    | This latched input selects the polarity of the OE pins.         |

| 40    |           | INFOT    | 0 = OE pins active high, 1 = OE pins active low (OE#)           |

| 41    | DIF_7#    | OUTPUT   | 0.7V differential complement clock outputs                      |

| 42    | DIF_7     | OUTPUT   | 0.7V differential true clock outputs                            |

| 43    | OE_4      | INPUT    | Active high input for enabling outputs.                         |

| 40    | 0L_4      |          | 0 = tri-state outputs, 1= enable outputs                        |

| 44    | OE_7      | INPUT    | Active high input for enabling outputs.                         |

|       | 0L_/      |          | 0 = tri-state outputs, 1= enable outputs                        |

| 45    | LOCK      | OUTPUT   | 3.3V output indicating PLL Lock Status. This pin goes high      |

| 40    | LOOK      | 0011 01  | when lock is achieved.                                          |

|       |           |          | This pin establishes the reference current for the differential |

| 46    | IREF      | INPUT    | current-mode output pairs. This pin requires a fixed precision  |

| 40    | 11 1∟1    |          | resistor tied to ground in order to establish the appropriate   |

|       |           |          | current. 475 ohms is the standard value.                        |

| 47    | GNDA      | POWER    | Ground pin for the PLL core.                                    |

| 48    | VDDA      | POWER    | 3.3V power for the PLL core.                                    |

| PIN # | PIN NAME    | <b>PIN TYPE</b> | DESCRIPTION                                                  |

|-------|-------------|-----------------|--------------------------------------------------------------|

|       |             |                 | Active low Input for determining SRC output frequency SRC or |

| 1     | SRC_DIV#    | INPUT           | SRC/2.                                                       |

|       |             |                 | 0 = SRC/2, 1= SRC                                            |

| 2     | VDD         | POWER           | Power supply, nominal 3.3V                                   |

| 3     | GND         | POWER           | Ground pin.                                                  |

| 4     | SRC_IN      | INPUT           | 0.7 V Differential SRC TRUE input                            |

| 5     | SRC_IN#     | INPUT           | 0.7 V Differential SRC COMPLEMENTARY input                   |

| 6     | OE0#        | INPUT           | Active low input for enabling DIF pair 0.                    |

| 0     | OE0#        | INFOT           | 1 = tri-state outputs, 0 = enable outputs                    |

| 7     | OE3#        | INPUT           | Active low input for enabling DIF pair 3.                    |

| 1     | 0L3#        |                 | 1 = tri-state outputs, 0 = enable outputs                    |

| 8     | DIF_0       | OUTPUT          | 0.7V differential true clock outputs                         |

| 9     | DIF_0#      | OUTPUT          | 0.7V differential complement clock outputs                   |

| 10    | GND         | POWER           | Ground pin.                                                  |

| 11    | VDD         | POWER           | Power supply, nominal 3.3V                                   |

| 12    | DIF_1       | OUTPUT          | 0.7V differential true clock outputs                         |

| 13    | DIF_1#      | OUTPUT          | 0.7V differential complement clock outputs                   |

| 14    | OE1#        | INPUT           | Active low input for enabling DIF pair 1.                    |

| 14    | UE1#        | INFOT           | 1 = tri-state outputs, 0 = enable outputs                    |

| 15    | OE2#        | INPUT           | Active low input for enabling DIF pair 2.                    |

| 15    | UE2#        | INFOT           | 1 = tri-state outputs, 0 = enable outputs                    |

| 16    | DIF_2       | OUTPUT          | 0.7V differential true clock outputs                         |

| 17    | DIF_2#      | OUTPUT          | 0.7V differential complement clock outputs                   |

| 18    | GND         | POWER           | Ground pin.                                                  |

| 19    | VDD         | POWER           | Power supply, nominal 3.3V                                   |

| 20    | DIF_3       | OUTPUT          | 0.7V differential true clock outputs                         |

| 21    | DIF_3#      | OUTPUT          | 0.7V differential complement clock outputs                   |

| 22    | BYPASS#/PLL | INPUT           | Input to select Bypass(fan-out) or PLL (ZDB) mode            |

|       | DIFA00#/FLL |                 | 0 = Bypass mode, 1= PLL mode                                 |

| 23    | SCLK        | INPUT           | Clock pin of SMBus circuitry, 5V tolerant.                   |

| 24    | SDATA       | I/O             | Data pin for SMBus circuitry, 5V tolerant.                   |

| PIN # | PIN NAME | <b>PIN TYPE</b> | DESCRIPTION                                                     |

|-------|----------|-----------------|-----------------------------------------------------------------|

| 25    | GND      | PWR             | Ground pin.                                                     |

|       |          |                 | Asynchronous active high input pin used to power down the       |

| 26    | PD       | IN              | device. The internal clocks are disabled and the VCO is         |

|       |          |                 | stopped.                                                        |

| 27    | SRC_STOP | IN              | Active high input to stop SRC outputs.                          |

| 28    | HIGH_BW# | IN              | 3.3V input for selecting PLL Band Width                         |

| 20    |          |                 | 0 = High, 1= Low                                                |

| 29    | DIF_4#   | OUT             | 0.7V differential complement clock outputs                      |

| 30    | DIF_4    | OUT             | 0.7V differential true clock outputs                            |

| 31    | VDD      | PWR             | Power supply, nominal 3.3V                                      |

| 32    | GND      | PWR             | Ground pin.                                                     |

| 33    | DIF_5#   | OUT             | 0.7V differential complement clock outputs                      |

| 34    | DIF_5    | OUT             | 0.7V differential true clock outputs                            |

| 35    | OE5#     | IN              | Active low input for enabling DIF pair 5.                       |

| - 55  | 013#     | IIN             | 1 = tri-state outputs, 0 = enable outputs                       |

| 36    | OE6#     | IN              | Active low input for enabling DIF pair 6.                       |

| - 50  |          |                 | 1 = tri-state outputs, 0 = enable outputs                       |

| 37    | DIF_6#   | OUT             | 0.7V differential complement clock outputs                      |

| 38    | DIF_6    | OUT             | 0.7V differential true clock outputs                            |

| 39    | VDD      | PWR             | Power supply, nominal 3.3V                                      |

| 40    | OE_INV   | IN              | This latched input selects the polarity of the OE pins.         |

| 40    |          |                 | 0 = OE pins active high, 1 = OE pins active low (OE#)           |

| 41    | DIF_7#   | OUT             | 0.7V differential complement clock outputs                      |

| 42    | DIF_7    | OUT             | 0.7V differential true clock outputs                            |

| 43    | OE4#     | IN              | Active low input for enabling DIF pair 4                        |

| 43    | 024#     | IIN             | 1 = tri-state outputs, 0 = enable outputs                       |

| 44    | OE7#     | IN              | Active low input for enabling DIF pair 7.                       |

| 44    | 02/#     | IIN             | 1 = tri-state outputs, 0 = enable outputs                       |

| 45    | LOCK     | OUT             | 3.3V output indicating PLL Lock Status. This pin goes high      |

| 45    | LUCK     | 001             | when lock is achieved.                                          |

|       |          |                 | This pin establishes the reference current for the differential |

| 46    | IREF     | IN              | current-mode output pairs. This pin requires a fixed precision  |

| 40    |          | IIN             | resistor tied to ground in order to establish the appropriate   |

|       |          |                 | current. 475 ohms is the standard value.                        |

| 47    | GNDA     | PWR             | Ground pin for the PLL core.                                    |

| 48    | VDDA     | PWR             | 3.3V power for the PLL core.                                    |

#### **Absolute Max**

| Symbol          | Parameter                 | Min     | Max            | Units |

|-----------------|---------------------------|---------|----------------|-------|

| VDD_A           | 3.3V Core Supply Voltage  |         | 4.6            | V     |

| VDD_In          | 3.3V Logic Supply Voltage |         | 4.6            | V     |

| VIL             | Input Low Voltage         | GND-0.5 |                | V     |

| V <sub>IH</sub> | Input High Voltage        |         | $V_{DD}$ +0.5V | V     |

| Ts              | Storage Temperature       | -65     | 150            | °C    |

| Tambient        | Ambient Operating Temp    | 0       | 70             | °C    |

| Tcase           | Case Temperature          |         | 115            | О°    |

|                 | Input ESD protection      |         |                |       |

| ESD prot        | human body model          | 2000    |                | V     |

# Electrical Characteristics - Input/Supply/Common Output Parameters T<sub>A</sub> = 0 - 70°C; Supply Voltage V<sub>DD</sub> = 3.3 V +/-5%

| PARAMETER                        | SYMBOL                   | CONDITIONS                                                                                                   | MIN       | TYP                                   | MAX                   | UNITS | NOTES |

|----------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|-----------------------|-------|-------|

| Input High Voltage               | V <sub>IH</sub>          | 3.3 V +/-5%                                                                                                  | 2         |                                       | V <sub>DD</sub> + 0.3 | V     |       |

| Input Low Voltage                | V <sub>IL</sub>          | 3.3 V +/-5%                                                                                                  | GND - 0.3 |                                       | 0.8                   | V     |       |

| Input High Current               | I <sub>IH</sub>          | $V_{IN} = V_{DD}$                                                                                            | -5        |                                       | 5                     | uA    |       |

|                                  | I <sub>IL1</sub>         | V <sub>IN</sub> = 0 V; Inputs with no pull-<br>up resistors                                                  | -5        |                                       |                       | uA    |       |

| Input Low Current                | I <sub>IL2</sub>         | V <sub>IN</sub> = 0 V; Inputs with pull-up<br>resistors                                                      | -200      |                                       |                       | uA    |       |

| One wating Council Coursent      | I <sub>DD3.3PLL</sub>    |                                                                                                              |           | 175                                   | 200                   | mA    |       |

| Operating Supply Current         | I <sub>DD3.3ByPass</sub> | Full Active, $C_L = Full load;$                                                                              |           | 160                                   | 175                   | mA    |       |

| Powerdown Current                |                          | all diff pairs driven                                                                                        |           | 50                                    | 70                    | mA    |       |

| Powerdown Current                | DD3.3PD                  | all differential pairs tri-stated                                                                            |           | 1                                     | 4                     | mA    |       |

| Input Frequency                  | F <sub>iPLL</sub>        | PLL Mode                                                                                                     | 50        |                                       | 200                   | MHz   |       |

| Input Frequency                  | F <sub>iBypass</sub>     | Bypass Mode (Revision<br>B/REV ID = 1H)                                                                      | 0         |                                       | 333.33                | MHz   |       |

| Input Frequency                  | F <sub>iBypass</sub>     | Bypass Mode (Revision<br>C/REV ID = 2H)                                                                      | 0         |                                       | 400                   | MHz   |       |

| Pin Inductance <sup>1</sup>      | L <sub>pin</sub>         |                                                                                                              |           |                                       | 7                     | nH    | 1     |

|                                  | C <sub>IN</sub>          | Logic Inputs                                                                                                 | 1.5       |                                       | 4                     | pF    | 1     |

| Input Capacitance <sup>1</sup>   | C <sub>OUT</sub>         | Output pin capacitance                                                                                       |           |                                       | 4                     | pF    | 1     |

|                                  |                          | PLL Bandwidth when<br>PLL_BW=0                                                                               | 2.4       | 3                                     | 3.4                   | MHz   | 1     |

| PLL Bandwidth                    | BW                       | PLL Bandwidth when<br>PLL_BW=1                                                                               | 0.7       | 1                                     | 1.4                   | MHz   | 1     |

| Clk Stabilization <sup>1,2</sup> | T <sub>STAB</sub>        | From V <sub>DD</sub> Power-Up and after<br>input clock stabilization or de-<br>assertion of PD# to 1st clock |           | 0.5                                   | 1                     | ms    | 1,2   |

| Modulation Frequency             | fMOD                     | Triangular Modulation                                                                                        | 30        | · · · · · · · · · · · · · · · · · · · | 33                    | kHz   | 1     |

| Tdrive_SRC_STOP#                 |                          | DIF output enable after<br>SRC_Stop# de-assertion                                                            |           | 10                                    | 15                    | ns    | 1,3   |

| Tdrive_PD#                       |                          | DIF output enable after<br>PD# de-assertion                                                                  |           |                                       | 300                   | us    | 1,3   |

| Tfall                            |                          | Fall time of PD# and<br>SRC_STOP#                                                                            |           |                                       | 5                     | ns    | 1     |

| Trise                            |                          | Rise time of PD# and<br>SRC_STOP#                                                                            |           |                                       | 5                     | ns    | 2     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup>See timing diagrams for timing requirements.

<sup>3</sup>Time from deassertion until outputs are >200 mV

IDT<sup>™</sup>/ICS<sup>™</sup> Eight Output Differential Buffer for PCI Express (50-200MHz)

### **Electrical Characteristics - Clock Input Parameters**

| $T_A = 0.70$ C; Supply Voltage $v_{DD} = 3.3 \text{ V} + 7.5\%$ |                       |                                                   |                       |      |       |       |  |  |  |

|-----------------------------------------------------------------|-----------------------|---------------------------------------------------|-----------------------|------|-------|-------|--|--|--|

| PARAMETER                                                       | SYMBOL                | CONDITIONS                                        | MIN                   | MAX  | UNITS | NOTES |  |  |  |

| Differential Input High Voltage                                 | V <sub>IHDIF</sub>    | Differential inputs<br>(single-ended measurement) | 600                   | 1150 | mV    | 1     |  |  |  |

| Differential Input Low Voltage                                  | V <sub>ILDIF</sub>    | Differential inputs<br>(single-ended measurement) | V <sub>SS</sub> - 300 | 300  | mV    | 1     |  |  |  |

| Input Slew Rate - DIF_IN                                        | dv/dt                 | Measured differentially                           | 0.4                   | 8    | V/ns  | 2     |  |  |  |

| Input Leakage Current                                           | I <sub>IN</sub>       | $V_{IN} = V_{DD}, V_{IN} = GND$                   | -5                    | 5    | uA    | 1     |  |  |  |

| Input Duty Cycle                                                | d <sub>tin</sub>      | Measurement from differential<br>wavefrom         | 45                    | 55   | %     | 1     |  |  |  |

| Input SRC Jitter - Cycle to<br>Cycle                            | SRCJ <sub>C2CIn</sub> | Differential Measurement                          |                       | 125  | ps    | 1     |  |  |  |

$T_A = 0 - 70^{\circ}C$ ; Supply Voltage  $V_{DD} = 3.3 \text{ V} \pm -5\%$

<sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup>Slew rate measured through Vswing centered around differential zero

### Electrical Characteristics - DIF 0.7V Current Mode Differential Pair

| PARAMETER                          | SYMBOL                | CONDITIONS                                                        | MIN  | TYP | MAX  | UNITS | NOTES |

|------------------------------------|-----------------------|-------------------------------------------------------------------|------|-----|------|-------|-------|

| Current Source Output<br>Impedance | Zo <sup>1</sup>       | $V_{O} = V_{x}$                                                   | 3000 |     |      | Ω     | 1     |

| Voltage High                       | VHigh                 | Statistical measurement on single ended signal using oscilloscope | 660  |     | 850  | mV    | 1,3   |

| Voltage Low                        | VLow                  | math function.                                                    | -150 |     | 150  | IIIV  | 1,3   |

| Max Voltage                        | Vovs                  | Measurement on single ended                                       |      |     | 1150 | mV    | 1     |

| Min Voltage                        | Vuds                  | signal using absolute value.                                      | -300 |     |      | 111V  | 1     |

| Crossing Voltage (abs)             | Vcross(abs)           |                                                                   | 250  |     | 550  | mV    | 1     |

| Crossing Voltage (var)             | d-Vcross              | Variation of crossing over all<br>edges                           |      |     | 140  | mV    | 1     |

| Long Accuracy                      | ppm                   | see Tperiod min-max values                                        |      |     | 0    | ppm   | 1,2   |

| Rise Time                          | t <sub>r</sub>        | $V_{OL} = 0.175V, V_{OH} = 0.525V$                                | 175  |     | 700  | ps    | 1     |

| Fall Time                          | t <sub>f</sub>        | $V_{OH} = 0.525 V V_{OL} = 0.175 V$                               | 175  |     | 700  | ps    | 1     |

| Rise Time Variation                | d-t <sub>r</sub>      |                                                                   |      |     | 125  | ps    | 1     |

| Fall Time Variation                | d-t <sub>f</sub>      |                                                                   |      |     | 125  | ps    | 1     |

| Duty Cycle                         | d <sub>t3</sub>       | Measurement from differential<br>wavefrom                         | 45   |     | 55   | %     | 1     |

| Skew                               | t <sub>sk3</sub>      | $V_{T} = 50\%$                                                    |      |     | 50   | ps    | 1     |

| Jitter, Cycle to cycle             | t <sub>jcyc-cyc</sub> | PLL mode,<br>Measurement from differential<br>wavefrom            |      |     | 50   | ps    | 1     |

|                                    |                       | BYPASS mode as additive jitter                                    |      |     | 50   | ps    | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that the input clock complies with CK409/CK410 accuracy requirements

${}^{3}I_{REF} = V_{DD}/(3xR_{R})$ . For  $R_{R} = 475\Omega$  (1%),  $I_{REF} = 2.32mA$ .  $I_{OH} = 6 \times I_{REF}$  and  $V_{OH} = 0.7V @ Z_{O} = 50\Omega$ .

#### ICS9DB801C Eight Output Differential Buffer for PCI Express (50-200MHz)

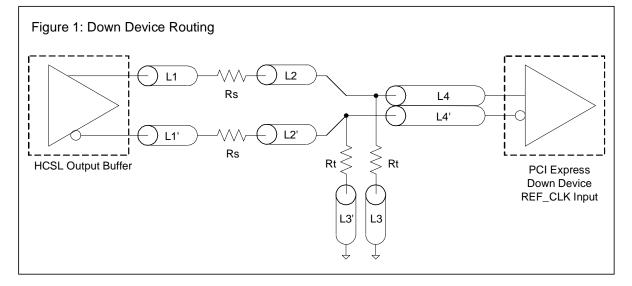

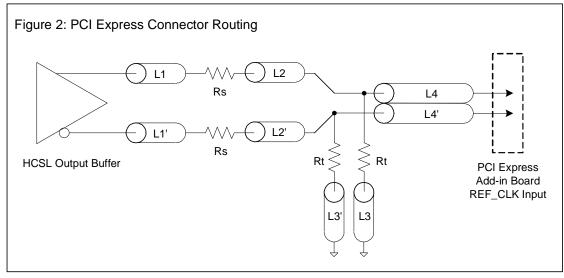

| SRC Reference Clock                                                |         |      |   |  |  |  |  |  |  |

|--------------------------------------------------------------------|---------|------|---|--|--|--|--|--|--|

| Common Recommendations for Differential Routing Dimension or Value |         |      |   |  |  |  |  |  |  |

| L1 length, route as non-coupled 50ohm trace                        | 0.5 max | inch | 1 |  |  |  |  |  |  |

| L2 length, route as non-coupled 50ohm trace                        | 0.2 max | inch | 1 |  |  |  |  |  |  |

| L3 length, route as non-coupled 50ohm trace                        | 0.2 max | inch | 1 |  |  |  |  |  |  |

| Rs                                                                 | 33      | ohm  | 1 |  |  |  |  |  |  |

| Rt                                                                 | 49.9    | ohm  | 1 |  |  |  |  |  |  |

| Down Device Differential Routing                                 |                     |      |   |

|------------------------------------------------------------------|---------------------|------|---|

| L4 length, route as coupled microstrip 100ohm differential trace | 2 min to 16 max     | inch | 1 |

| L4 length, route as coupled stripline 100ohm differential trace  | 1.8 min to 14.4 max | inch | 1 |

| Differential Routing to PCI Express Connector                    |                       |      |   |

|------------------------------------------------------------------|-----------------------|------|---|

| L4 length, route as coupled microstrip 100ohm differential trace | 0.25 to 14 max        | inch | 2 |

| L4 length, route as coupled stripline 100ohm differential trace  | 0.225 min to 12.6 max | inch | 2 |

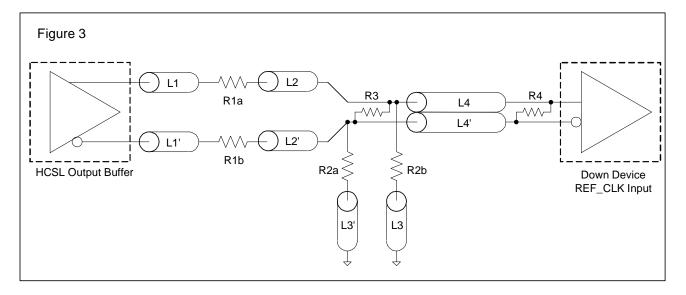

#### ICS9DB801C Eight Output Differential Buffer for PCI Express (50-200MHz)

|                                 | Alternative Termination for LVDS and other Common Differential Signals (figure 3) |      |    |      |      |      |                                |  |  |  |

|---------------------------------|-----------------------------------------------------------------------------------|------|----|------|------|------|--------------------------------|--|--|--|

| Vdiff Vp-p Vcm R1 R2 R3 R4 Note |                                                                                   |      |    |      |      | Note |                                |  |  |  |

| 0.45v                           | 0.22v                                                                             | 1.08 | 33 | 150  | 100  | 100  |                                |  |  |  |

| 0.58                            | 0.28                                                                              | 0.6  | 33 | 78.7 | 137  | 100  |                                |  |  |  |

| 0.80                            | 0.40                                                                              | 0.6  | 33 | 78.7 | none | 100  | ICS874003i-02 input compatible |  |  |  |

| 0.60                            | 0.3                                                                               | 1.2  | 33 | 174  | 140  | 100  | Standard LVDS                  |  |  |  |

| $R_{12} - R_{12}$               |                                                                                   |      |    |      |      |      |                                |  |  |  |

R1a = R1b = R1

R2a = R2b = R2

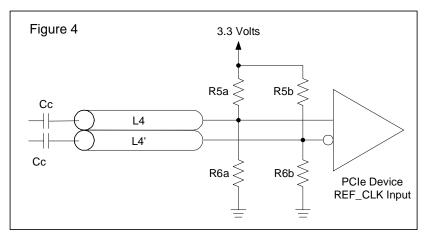

| Cable Connected AC Coupled Application (figure 4) |             |      |  |  |  |  |  |  |

|---------------------------------------------------|-------------|------|--|--|--|--|--|--|

| Component                                         | Value       | Note |  |  |  |  |  |  |

| R5a, R5b                                          | 8.2K 5%     |      |  |  |  |  |  |  |

| R6a, R6b                                          | 1K 5%       |      |  |  |  |  |  |  |

| Cc                                                | 0.1 µF      |      |  |  |  |  |  |  |

| Vcm                                               | 0.350 volts |      |  |  |  |  |  |  |

### General SMBus serial interface information for the ICS9DB801C

### How to Write:

- Controller (host) sends a start bit.

- Controller (host) sends the write address DC (h)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will *acknowledge*

- Controller (host) sends the data byte count = X

- ICS clock will *acknowledge*

- Controller (host) starts sending Byte N through Byte N + X -1

- ICS clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

### How to Read:

- Controller (host) will send start bit.

- Controller (host) sends the write address DC (h)

- ICS clock will *acknowledge*

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) will send a separate start bit.

- Controller (host) sends the read address DD (h)

- ICS clock will acknowledge

- ICS clock will send the data byte count = X

- ICS clock sends **Byte N + X -1**

- ICS clock sends Byte 0 through byte X (if X<sub>(h)</sub> was written to byte 8).

- Controller (host) will need to acknowledge each byte

- Controllor (host) will send a not acknowledge bit

- Controller (host) will send a stop bit

| Ind   | Index Block Write Ope       |                      |     |  |  |  |  |  |  |

|-------|-----------------------------|----------------------|-----|--|--|--|--|--|--|

| Coi   | ntroller (Host)             | ICS (Slave/Receiver) |     |  |  |  |  |  |  |

| Т     | starT bit                   |                      |     |  |  |  |  |  |  |

| Slav  | e Address DC <sub>(h)</sub> |                      |     |  |  |  |  |  |  |

| WR    | WRite                       |                      |     |  |  |  |  |  |  |

|       |                             |                      | ACK |  |  |  |  |  |  |

| Begi  | inning Byte = N             |                      |     |  |  |  |  |  |  |

|       |                             |                      | ACK |  |  |  |  |  |  |

| Data  | Byte Count = X              |                      |     |  |  |  |  |  |  |

|       |                             |                      | ACK |  |  |  |  |  |  |

| Begir | nning Byte N                |                      |     |  |  |  |  |  |  |

|       |                             |                      | ACK |  |  |  |  |  |  |

|       | <b>\$</b>                   | Byte                 |     |  |  |  |  |  |  |

|       | $\diamond$                  |                      | ○   |  |  |  |  |  |  |

|       | $\diamond$                  | $\times$             | ○   |  |  |  |  |  |  |

|       |                             | Ι                    | ○   |  |  |  |  |  |  |

| Byt   | e N + X - 1                 |                      |     |  |  |  |  |  |  |

|       |                             |                      | ACK |  |  |  |  |  |  |

| Р     | stoP bit                    |                      |     |  |  |  |  |  |  |

| Ind      | Index Block Read Operation  |          |                    |  |  |  |  |  |  |  |

|----------|-----------------------------|----------|--------------------|--|--|--|--|--|--|--|

| Con      | troller (Host)              | ICS      | S (Slave/Receiver) |  |  |  |  |  |  |  |

| Т        | starT bit                   |          |                    |  |  |  |  |  |  |  |

| Slave    | e Address DC <sub>(h)</sub> |          |                    |  |  |  |  |  |  |  |

| WR       | WRite                       |          |                    |  |  |  |  |  |  |  |

|          |                             |          | ACK                |  |  |  |  |  |  |  |

| Begii    | nning Byte = N              |          |                    |  |  |  |  |  |  |  |

|          |                             |          | ACK                |  |  |  |  |  |  |  |

| RT       | Repeat starT                |          |                    |  |  |  |  |  |  |  |

| Slave    | e Address DD <sub>(h)</sub> |          |                    |  |  |  |  |  |  |  |

| RD       | ReaD                        |          |                    |  |  |  |  |  |  |  |

|          |                             | ACK      |                    |  |  |  |  |  |  |  |

|          |                             |          |                    |  |  |  |  |  |  |  |

|          |                             | Da       | ata Byte Count = X |  |  |  |  |  |  |  |

|          | ACK                         |          |                    |  |  |  |  |  |  |  |

|          |                             |          | Beginning Byte N   |  |  |  |  |  |  |  |

|          | ACK                         |          |                    |  |  |  |  |  |  |  |

|          |                             | X Byte   | 0                  |  |  |  |  |  |  |  |

|          | $\diamond$                  | б.       | $\diamond$         |  |  |  |  |  |  |  |

|          | 0                           | $\times$ | <b>O</b>           |  |  |  |  |  |  |  |

| <b>Q</b> |                             |          |                    |  |  |  |  |  |  |  |

|          |                             |          | Byte N + X - 1     |  |  |  |  |  |  |  |

| N        | Not acknowledge             |          |                    |  |  |  |  |  |  |  |

| Р        | stoP bit                    |          |                    |  |  |  |  |  |  |  |

| Ву    | rte 0     | Pin # | Name      | Control Function       | Туре | 0        | 1      | PWD |

|-------|-----------|-------|-----------|------------------------|------|----------|--------|-----|

| Bit 7 | -         |       | PD_Mode   | PD# drive mode         | RW   | driven   | Hi-Z   | 0   |

| Bit 6 | -         |       | STOP_Mode | SRC_Stop# drive mode   | RW   | driven   | Hi-Z   | 0   |

| Bit 5 | -         |       | Reserved  | Reserved               | RW   | Reserved |        | Х   |

| Bit 4 | -         |       | Reserved  | Reserved               | RW   | Reserved |        | Х   |

| Bit 3 | -         |       | Reserved  | Reserved               | RW   | Rese     | erved  | Х   |

| Bit 2 | -         |       | PLL_BW#   | Select PLL BW          | RW   | High BW  | Low BW | 1   |

| Bit 1 | - BYPASS# |       | BYPASS#   | BYPASS#/PLL            | RW   | fan-out  | ZDB    | 1   |

| Bit 0 | -         |       | SRC_DIV#  | SRC Divide by 2 Select | RW   | x/2      | 1x     | 1   |

#### SMBus Table: Frequency Select Register, READ/WRITE ADDRESS (DC/DD)

#### SMBus Table: Output Control Register

| Ву    | te 1 | Pin # | Name  | Control Function | Туре | 0       | 1      | PWD |

|-------|------|-------|-------|------------------|------|---------|--------|-----|

| Bit 7 | 42,  | ,41   | DIF_7 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 6 | 38,  | ,37   | DIF_6 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 5 | 34,  | ,33   | DIF_5 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 4 | 30,  | ,29   | DIF_4 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 3 | 20,  | ,21   | DIF_3 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 2 | 16,  | ,17   | DIF_2 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 1 | 12,  | ,13   | DIF_1 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 0 | 8,   | ,9    | DIF_0 | Output Control   | RW   | Disable | Enable | 1   |

#### SMBus Table: Output Control Register

| Ву    | te 2 | Pin # | Name  | Control Function | Туре | 0        | 1         | PWD |

|-------|------|-------|-------|------------------|------|----------|-----------|-----|

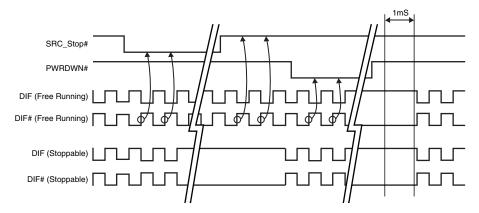

| Bit 7 | 42,  | 41    | DIF_7 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 6 | 38,  | 37    | DIF_6 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 5 | 34,  | 33    | DIF_5 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 4 | 30,  | 29    | DIF_4 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 3 | 20,  | 21    | DIF_3 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 2 | 16,  | 17    | DIF_2 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 1 | 12,  | 13    | DIF_1 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 0 | 8,   | 9     | DIF_0 | Output Control   | RW   | Free-run | Stoppable | 0   |

#### SMBus Table: Output Control Register

| Byte 3 | Pin # | Name | Control Function | Туре | 0    | 1     | PWD |

|--------|-------|------|------------------|------|------|-------|-----|

| Bit 7  |       |      | Reserved         |      | Rese | erved | Х   |

| Bit 6  |       |      | Reserved         |      | Rese | erved | Х   |

| Bit 5  |       |      | Reserved         | RW   | Rese | erved | Х   |

| Bit 4  |       |      | Reserved         |      | Rese | erved | Х   |

| Bit 3  |       |      | Reserved         | RW   | Rese | erved | Х   |

| Bit 2  |       |      | Reserved         | RW   | Rese | erved | Х   |

| Bit 1  |       |      | Reserved         | RW   | Rese | erved | Х   |

| Bit 0  |       |      | Reserved         | RW   | Rese | erved | Х   |

**IDT<sup>™</sup>/ICS<sup>™</sup>** Eight Output Differential Buffer for PCI Express (50-200MHz)

| Ву    | te 4 Pin | # Name | Control Function | Туре | 0 | 1 | PWD |

|-------|----------|--------|------------------|------|---|---|-----|

| Bit 7 | -        | RID3   | REVISION ID -    | R    | - | - | Х   |

| Bit 6 | -        | RID2   |                  | R    | - | - | Х   |

| Bit 5 | -        | RID1   | REVISION ID      | R    | - | - | Х   |

| Bit 4 | -        | RID0   |                  | R    | - | - | Х   |

| Bit 3 | -        | VID3   |                  | R    | - | - | 0   |

| Bit 2 | -        | VID2   | VENDOR ID        | R    | - | - | 0   |

| Bit 1 | -        | VID1   | VENDOR ID        | R    | - | - | 0   |

| Bit 0 | -        | VID0   |                  | R    | - | - | 1   |

#### SMBus Table: Vendor & Revision ID Register

#### SMBus Table: DEVICE ID

| Ву    | te 5                | Pin #                    | Name                   | Control Function | Туре  | 0        | 1 | PWD |

|-------|---------------------|--------------------------|------------------------|------------------|-------|----------|---|-----|

| Bit 7 | -                   |                          | Dev                    | vice ID 7 (MSB)  | R     | Reserved |   | 1   |

| Bit 6 | -                   |                          |                        | Device ID 6      | R     | Reserved |   | 0   |

| Bit 5 | -                   |                          |                        | Device ID 5      | R     | Reserved |   | 0   |

| Bit 4 | 4 - Device ID 4 R R |                          | Rese                   | erved            | 0     |          |   |     |

| Bit 3 | t 3 - Device ID 3   |                          | R                      | Rese             | erved | 0        |   |     |

| Bit 2 | -                   | - Device ID 2 R Reserved |                        | 0                |       |          |   |     |

| Bit 1 | -                   |                          | Device ID 1 R Reserved |                  | 0     |          |   |     |

| Bit 0 | -                   | Device ID 0 R Reserved   |                        | 1                |       |          |   |     |

#### SMBus Table: Byte Count Register

| By    | te 6 | Pin # | Name | Control Function   | Туре | 0 | 1 | PWD |

|-------|------|-------|------|--------------------|------|---|---|-----|

| Bit 7 | -    |       | BC7  |                    | RW   | - | - | 0   |

| Bit 6 | -    |       | BC6  |                    | RW   | - | - | 0   |

| Bit 5 | -    |       | BC5  |                    | RW   | - | - | 0   |

| Bit 4 | -    |       | BC4  |                    | RW   | - | - | 0   |

| Bit 3 | -    | -     | BC3  | will be read back. | RW   | - | - | 0   |

| Bit 2 | -    |       | BC2  |                    | RW   | - | - | 1   |

| Bit 1 | -    |       | BC1  |                    | RW   | - | - | 1   |

| Bit 0 | -    |       | BC0  |                    | RW   | - | - | 1   |

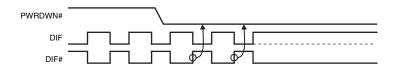

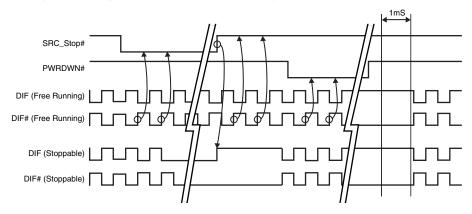

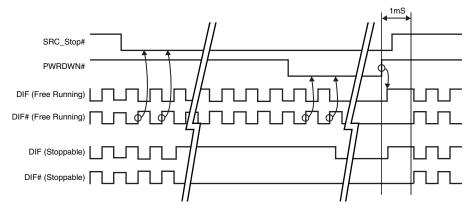

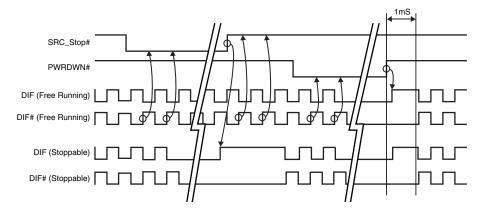

Note: Polarities in timing diagrams are shown  $OE_{INV} = 0$ . They are similar to  $OE_{INV} = 1$ .

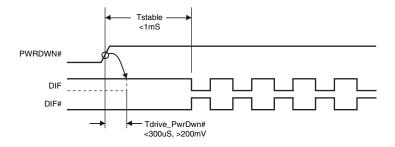

#### PD#, Power Down

The PD# pin cleanly shuts off all clocks and places the device into a power saving mode. PD# must be asserted before shutting off the input clock or power to insure an orderly shutdown. PD is asynchronous active-low input for both powering down the device and powering up the device. When PD# is asserted, all clocks will be driven high, or tri-stated (depending on the PD# drive mode and Output control bits) before the PLL is shut down.

#### **PD# Assertion**

When PD# is sampled low by two consecutive rising edges of DIF#, all DIF outputs must be held High, or tri-stated (depending on the PD# drive mode and Output control bits) on the next High-Low transition of the DIF# outputs. When the PD# drive mode bit is set to '0', all clock outputs will be held with DIF driven High with 2 x IREF and DIF# tri-stated. If the PD# drive mode bit is set to '1', both DIF and DIF# are tri-stated.

#### **PD# De-assertion**

Power-up latency is less than 1 ms. This is the time from de-assertion of the PD# pin, or VDD reaching 3.3V, or the time from valid SRC\_IN clocks until the time that stable clocks are output from the device (PLL Locked). If the PD# drive mode bit is set to '1', all the DIF outputs must driven to a voltage of >200 mV within 300 us of PD# de-assertion.

#### SRC\_STOP#

The SRC\_STOP# signal is an active-low asynchronous input that cleanly stops and starts the DIF outputs. A valid clock must be present on SRC\_IN for this input to work properly. The SRC\_STOP# signal is de-bounced and must remain stable for two consecutive rising edges of DIF# to be recognized as a valid assertion or de-assertion.

#### SRC\_STOP# - Assertion

Asserting SRC\_STOP# causes all DIF outputs to stop after their next transition (if the control register settings allow the output to stop). When the SRC\_STOP# drive bit is '0', the final state of all stopped DIF outputs is DIF = High and DIF# = Low. There is no change in output drive current. DIF is driven with  $6x_{REF}$  DIF# is not driven, but pulled low by the termination. When the SRC\_STOP# drive bit is '1', the final state of all DIF output pins is Low. Both DIF and DIF# are not driven.

#### SRC\_STOP# - De-assertion (transition from '0' to '1')

All stopped differential outputs resume normal operation in a glitch-free manner. The de-assertion latency to active outputs is 2-6 DIF clock periods, with all DIF outputs resuming simultaneously. If the SRC\_STOP# drive control bit is '1' (tri-state), all stopped DIF outputs must be driven High (>200 mV) within 10 ns of de-assertion.

#### SRC\_STOP\_1 (SRC\_Stop = Driven, PD = Driven)

#### SRC\_STOP\_2 (SRC\_Stop =Tristate, PD = Driven)

**IDT<sup>™</sup>/ICS<sup>™</sup>** Eight Output Differential Buffer for PCI Express (50-200MHz)

#### SRC\_STOP\_3 (SRC\_Stop = Driven, PD = Tristate)

SRC\_STOP\_4 (SRC\_Stop = Tristate, PD = Tristate)

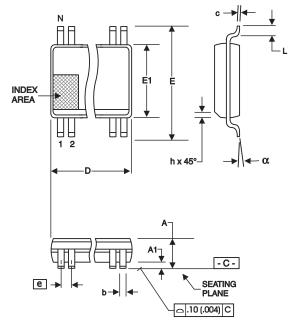

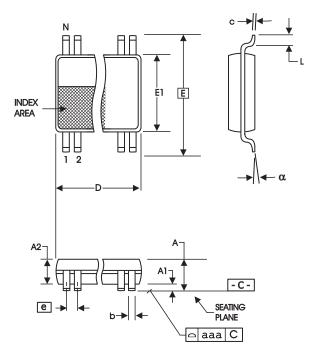

|        | In Millimeters    |         | In Inches         |      |  |

|--------|-------------------|---------|-------------------|------|--|

| SYMBOL | COMMON DIMENSIONS |         | COMMON DIMENSIONS |      |  |

|        | MIN               | MAX     | MIN               | MAX  |  |

| A      | 2.41              | 2.80    | .095              | .110 |  |

| A1     | 0.20              | 0.40    | .008              | .016 |  |

| b      | 0.20              | 0.34    | .008 .0135        |      |  |

| С      | 0.13              | 0.25    | .005              | .010 |  |

| D      | SEE VARIATIONS    |         | SEE VARIATIONS    |      |  |

| E      | 10.03             | 10.68   | .395              | .420 |  |

| E1     | 7.40              | 7.60    | .291              | .299 |  |

| е      | 0.635 I           | BASIC   | 0.025 BASIC       |      |  |

| h      | 0.38              | 0.64    | .015              | .025 |  |

| L      | 0.50              | 1.02    | .020              | .040 |  |

| N      | SEE VAR           | IATIONS | SEE VARIATIONS    |      |  |

| α      | 0°                | 8°      | 0°                | 8°   |  |

#### VARIATIONS

D (inch)

MAX

.630

MIN

.620

MIN MAX 48 15.75 16.00

D mm.

Reference Doc.: JEDEC Publication 95, MO-118

10-0034

Ν

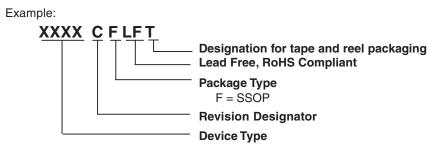

### **Ordering Information**

#### 9DB801CFLFT

**IDT<sup>™</sup>/ICS<sup>™</sup>** Eight Output Differential Buffer for PCI Express (50-200MHz)

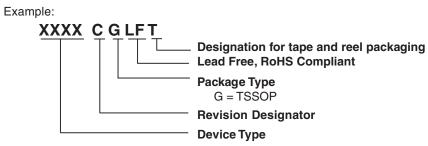

| 48-Lead, 6.10 mm. | Body, 0.50 mm. Pitch TSSOP |

|-------------------|----------------------------|

| (240 mil)         | (20 mil)                   |

|        | In Millimeters                |          | In Inches         |      |  |

|--------|-------------------------------|----------|-------------------|------|--|

| SYMBOL | COMMON DIMENSIONS             |          | COMMON DIMENSIONS |      |  |

|        | MIN                           | MAX      | MIN               | MAX  |  |

| A      |                               | 1.20     |                   | .047 |  |

| A1     | 0.05                          | 0.15     | .002              | .006 |  |

| A2     | 0.80                          | 1.05     | .032 .041         |      |  |

| b      | 0.17                          | 0.27     | .007 .011         |      |  |

| С      | 0.09                          | 0.20     | .0035             | .008 |  |

| D      | SEE VAF                       | RIATIONS | SEE VARIATIONS    |      |  |

| E      | 8.10 E                        | BASIC    | 0.319 BASIC       |      |  |

| E1     | 6.00                          | 6.20     | .236              | .244 |  |

| е      | 0.50 E                        | BASIC    | 0.020 BASIC       |      |  |

| L      | 0.45                          | 0.75     | .018              | .030 |  |

| N      | SEE VARIATIONS SEE VARIATIONS |          | RIATIONS          |      |  |

| а      | 0°                            | 8°       | 0°                | 8°   |  |

| aaa    |                               | 0.10     | 004               |      |  |

#### VARIATIONS

| Ν  | D mm. |       | D (inch) |      |

|----|-------|-------|----------|------|

|    | MIN   | MAX   | MIN      | MAX  |

| 48 | 12.40 | 12.60 | .488     | .496 |

Reference Doc.: JEDEC Publication 95, MO-153

10-0039

### **Ordering Information**

### 9DB801CGLFT

**IDT<sup>™</sup>/ICS<sup>™</sup>** Eight Output Differential Buffer for PCI Express (50-200MHz)

#### **Revision History**

| Rev. | Issue Date | Description                                                     | Page # |

|------|------------|-----------------------------------------------------------------|--------|

| Α    | 4/8/2005   | Release to Final                                                |        |

|      |            | 1. Added Polarity Table.                                        |        |

|      |            | 2. Updated Electrical Characteristics.                          |        |

|      |            | 3. Updated LF Ordering Information from "Annealed Lead Free" to | 1, 7,  |

| В    | 9/7/2006   | "RoHS Compliant".                                               | 16-17  |

| С    | 2/29/2008  | Added Input Clock Specs                                         | 8      |

| D    | 12/3/2008  | Removed ICS prefix from ordering information.                   | 17-18  |

| E    | 1/27/2011  | Updated terminaton Figure 4.                                    | 10     |

### Innovate with IDT and accelerate your future networks. Contact:

#### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

#### For Tech Support

408-284-6578 pcclockhelp@idt.com

#### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

#### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### Europe

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

IDT (Integrated Device Technology):

<u>9DB801BGLFT</u> <u>9DB801BFLF</u> <u>9DB801BGLF</u> <u>9DB801CGLFT</u> <u>9DB801CFLF</u> <u>9DB801CFLF</u> <u>9DB801CFLFT</u>