# TPS929120-Q1 12-Channel Automotive 40-V High-Side LED Driver with FlexWire

# 1 Features

- AEC-Q100-qualified for automotive applications: Temperature grade 1: -40°C to +125°C, T<sub>A</sub>

- **Functional Safety-Capable**

- Documentation available to aid functional safety system design

- 12-Channel precision high-side current output:

- Supply voltage 4.5 V to 40 V

- Up to 75 mA channel current set by resistor

- 2-Bit global, 6-bit independent current setting

- High current accuracy < ±5% at 5 mA to 75 mA</li>

- High current accuracy < ±10% at 1 mA</li>

- Low voltage drop 500 mV at 50 mA

- 12-Bit independent PWM dimming

- Programmable PWM frequency up to 20 kHz

- Linear and exponential dimming method \_

- FlexWire control interface

- Up to 1-MHz clock frequency

- Maximum 16 devices on one FlexWire bus

- Up to 8 bytes data transaction in one frame

- 5-V LDO output to supply CAN transceiver

- Diagnostic and protection:

- Programmable fail-safe state

- LED open-circuit detection

- LED short-circuit detection

- Single-LED short-circuit diagnostic

- Programmable low-supply detection

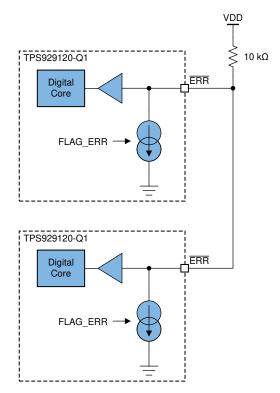

- Open-drain ERR for fault indication

- Watchdog and CRC for FlexWire interface

- 8-Bit ADC for pin voltage measurement

- Overtemperature protection

## 2 Applications

- Automotive exterior rear light

- Automotive exterior headlight

- Automotive interior ambient light

- Automotive cluster display

### **3 Description**

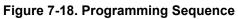

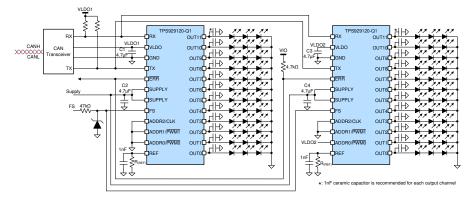

With increasing demand for animation in automotive lighting, LEDs must be controlled independently. Therefore, LED drivers with digital interfaces are essential to effectively drive pixel-controlled lighting applications. In exterior lighting, multiple lamp functions are typically located on different PCB boards with off-board wires connected to each other. It is difficult for a traditional single-ended interface to meet the strict EMC requirements. By using an industrialstandard CAN physical layer, the UART-based FlexWire interface of the TPS929120-Q1 easily accomplishes long distance off-board communication without impacting EMC.

The TPS929120-Q1 is a 12-channel, 40-V high-side LED driver that controls the 8-bit output current and 12-bit PWM duty cycles. The device meets multiple regulation requirements with LED open-circuit, shortto-ground, and single LED short-circuit diagnostics. A configurable watchdog also automatically sets failsafe states when the MCU connection is lost, and, with programmable EEPROM, TPS929120-Q1 can flexibly be set for different application scenarios.

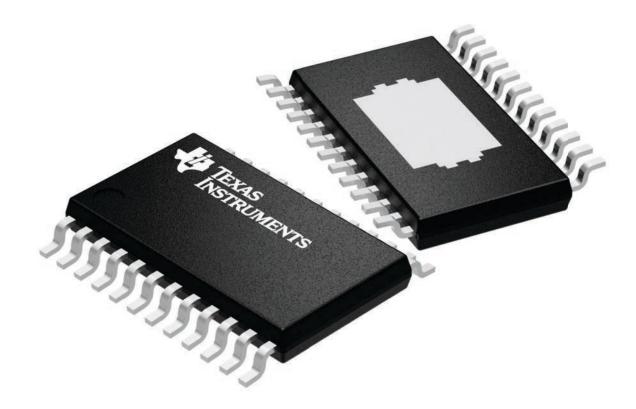

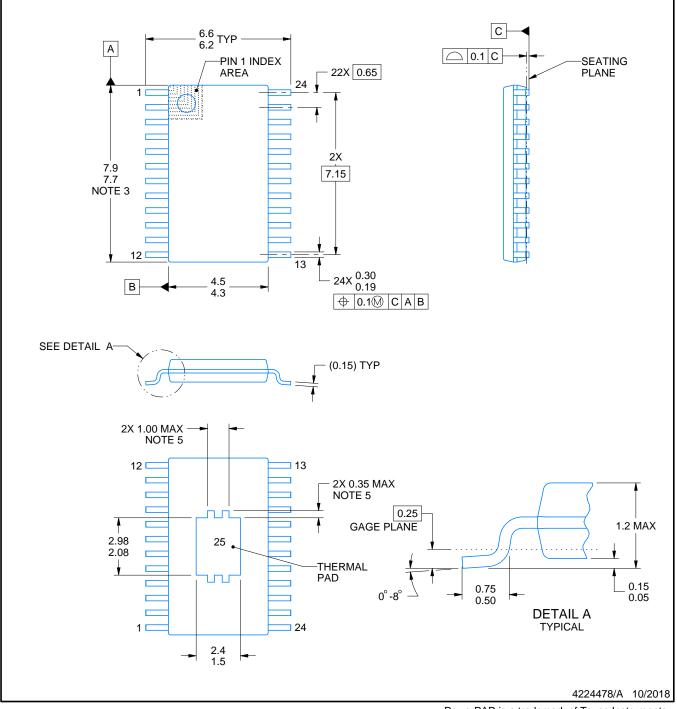

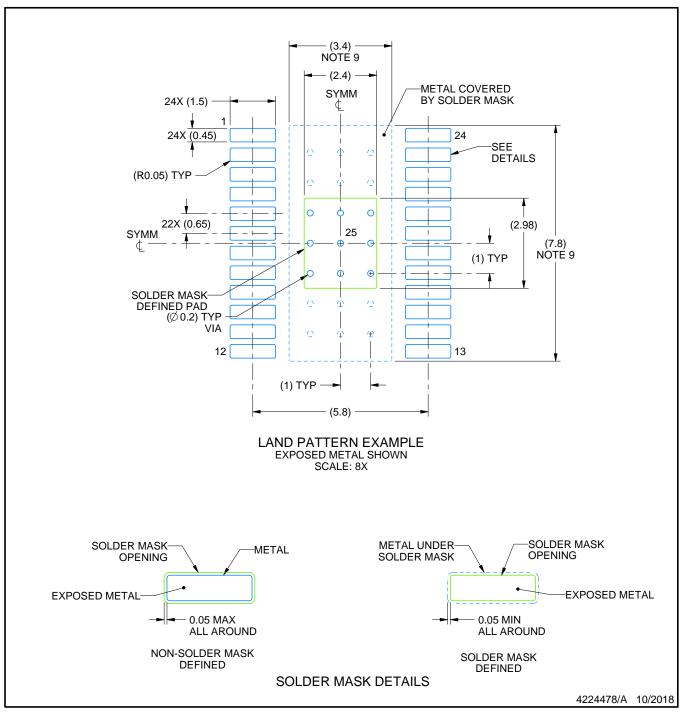

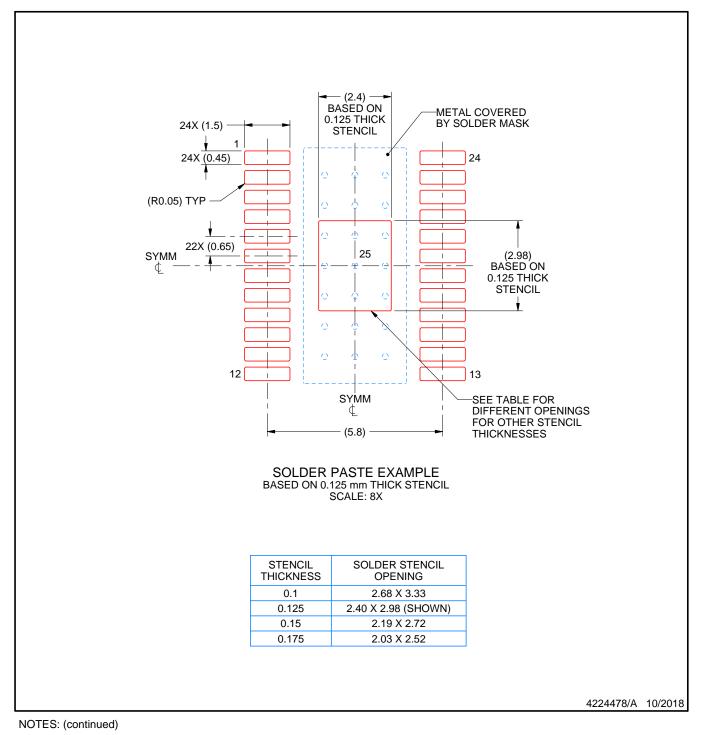

| Device | Information | (1) |

|--------|-------------|-----|

|--------|-------------|-----|

| PART NUMBER  | PACKAGE     | BODY SIZE (NOM)   |

|--------------|-------------|-------------------|

| TPS929120-Q1 | HTSSOP (24) | 7.80 mm × 4.40 mm |

For all available packages, see the orderable addendum at (1) the end of the data sheet.

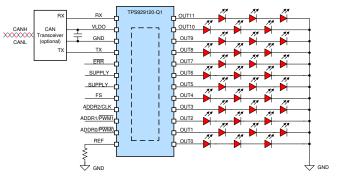

Typical Application Diagram

# **Table of Contents**

| 1 Features                           | 1              |

|--------------------------------------|----------------|

| 2 Applications                       | 1              |

| 3 Description                        | 1              |

| 4 Revision History                   |                |

| 5 Pin Configuration and Functions    | 4              |

| 6 Specifications                     | <mark>5</mark> |

| 6.1 Absolute Maximum Ratings         | <mark>5</mark> |

| 6.2 ESD Ratings                      | <mark>5</mark> |

| 6.3 Recommended Operating Conditions | 5              |

| 6.4 Thermal Information              | 6              |

| 6.5 Electrical Characteristics       | 6              |

| 6.6 Timing Requirements              | <mark>8</mark> |

| 6.7 Typical Characteristics          | 9              |

| 7 Detailed Description               | 14             |

| 7.1 Overview                         | 14             |

| 7.2 Functional Block Diagram         | 15             |

| 7.3 Feature Description.             |                |

| 7.4 Device Functional Modes          | 33             |

|                                      |                |

| 7.5 Programming                                      | 37    |

|------------------------------------------------------|-------|

| 7.6 Register Maps                                    |       |

| 8 Application and Implementation                     | . 154 |

| 8.1 Application Information                          |       |

| 8.2 Typical Application                              | . 154 |

| 9 Power Supply Recommendations                       |       |

| 10 Layout                                            | 158   |

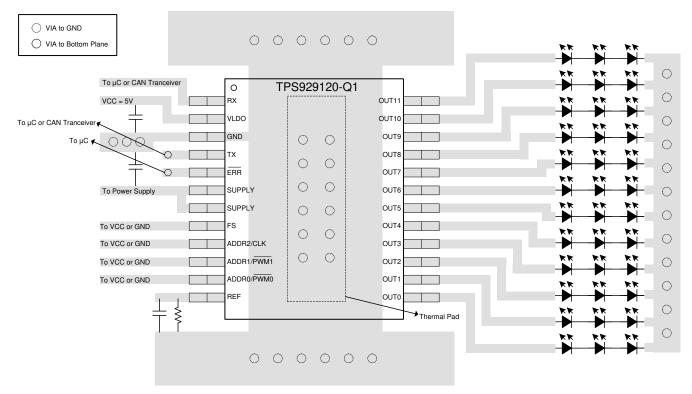

| 10.1 Layout Guidelines                               | . 158 |

| 10.2 Layout Example                                  | . 158 |

| 11 Device and Documentation Support                  | . 159 |

| 11.1 Receiving Notification of Documentation Updates | s 159 |

| 11.2 Support Resources                               | . 159 |

| 11.3 Trademarks                                      | . 159 |

| 11.4 Electrostatic Discharge Caution                 |       |

| 11.5 Glossary                                        | . 159 |

| 12 Mechanical, Packaging, and Orderable              |       |

| Information                                          | . 159 |

|                                                      |       |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | nanges from Revision A (February 2020) to Revision B (February 2021)                               | Page |

|----|----------------------------------------------------------------------------------------------------|------|

| •  | Updated the numbering format for tables, figures and cross-references throughout the document      | 1    |

| •  | Changed the bullet "Functional safety capable" to "Functional Safety-Capable" in the Features list | 1    |

| •  | Change to "CONF_ODPW=0h" from "CONF_ODPW=4h" in <i>Timing Requirements</i> table                   | 5    |

| •  | Change to "80-mA" from "50-mA"                                                                     | 15   |

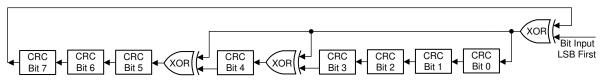

| •  | Add "LSB first" to CRC Algorithm Diagram                                                           | 27   |

| •  | Change "Supply UVLO" row to "Constant pulled down" from "No action"                                | 28   |

| •  | Change "Supply UVLO" row to "Constant pulled down" from "No action"                                | 32   |

| •  | Add description for TPS929120A version                                                             | 38   |

| •  | Add "All EEPROM shadow registers need to be written to target value before burning."               | 42   |

| •  | Change default value of register FLAG7 to "B3h" from "EFh"                                         | 45   |

| •  | Add note for default value of register FLAG7 for TPS929120A version                                | 45   |

| •  | Change default value of register EEPM7 to "A7h" from "07h"                                         |      |

| •  | Add note for default value of EEPROM register EEPM6 for TPS929120A version                         | 45   |

| •  | Add note for default value of EEPROM register EEPM15 for TPS929120A version                        | 45   |

| •  | Change reset value for CONF_AUTOSS to "0h" from "X"                                                |      |

| •  | Change to "FlexWire" from "FlexLED" in CONF_MISC2 register description                             |      |

| •  | Change to "19 V" from "20 V" in CONF_MISC2 register description                                    | 50   |

| •  | Add "Fh = 20 V" in CONF_MISC2 register description                                                 |      |

| •  | Add "automatically reset to 0" in CONF_FORCEERR register description                               | 50   |

| •  | Change to "Configuration" from "Miscellanous" in CONF_LOCK register description                    | 50   |

| •  | Change to "B3h" from "EFh" for FLAG7 register reset value                                          |      |

| •  | Add "Reset value is 09h for TPS929120A version" in FLAG7 register description                      |      |

| •  | Change to "CONFx" from "EEPROM" for FLAG8 register description                                     |      |

| •  | Add "Reset value is 8h for TPS929120A version" in EEPM6 register description                       |      |

| •  | Change to "19 V" from "20 V" in EEPM8 register description                                         |      |

| •  | Add "Fh = 20 V" in EEPM8 register description                                                      |      |

| •  | Change to "B3h" from "23h" for EEPM15 register reset value                                         | 50   |

### TPS929120-Q1 SLVSE03B – APRIL 2019 – REVISED FEBRUARY 2021

| • | Add 09h for EEPM15 manufacture default value for TPS929120A version      |      |  |  |  |  |

|---|--------------------------------------------------------------------------|------|--|--|--|--|

| С | hanges from Revision Original (April 2019) to Revision A (February 2020) | Page |  |  |  |  |

| • | Change from Advance Information to Production Data                       | 1    |  |  |  |  |

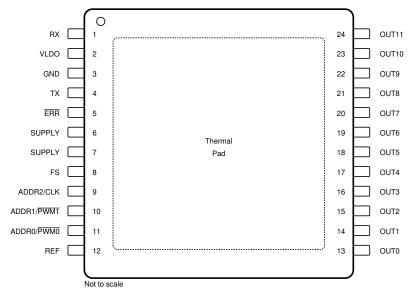

# **5** Pin Configuration and Functions

#### Table 5-1. Pin Functions

| PIN  |             | I/O   | DESCRIPTION                                                                                                                     |

|------|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------|

| NO.  | NAME        |       | DESCRIPTION                                                                                                                     |

| 1    | RX          | I     | FlexWire RX                                                                                                                     |

| 2    | VLDO        | Power | 5-V regulator output                                                                                                            |

| 3    | GND         | GND   | Device ground                                                                                                                   |

| 4    | ТХ          | 0     | FlexWire TX                                                                                                                     |

| 5    | ERR         | I/O   | Open-drain error output                                                                                                         |

| 6, 7 | SUPPLY      | Power | Power supply                                                                                                                    |

| 8    | FS          | I     | Fail-safe state selection. 0: Fail-safe state 0 ; 1: Fail-safe state 1                                                          |

| 9    | ADDR2/CLK   | I     | Function as device address 2 in external address mode; Function as PWM clock input internal address mode when CONF_EXTCLK is 1. |

| 10   | ADDR1/ PWM1 | I     | Function as device address 1 in external address mode; Function as PWM input channel for OUT6-11 in internal address mode.      |

| 11   | ADDR0/ PWM0 | I     | Function as device address 0 in external address mode; Function as PWM input channel for OUT0-5 in internal address mode.       |

| 12   | REF         | I/O   | Device reference current setting, EEPROM programming chip-selection input                                                       |

| 13   | OUT0        | 0     | Output channel 0                                                                                                                |

| 14   | OUT1        | 0     | Output channel 1                                                                                                                |

| 15   | OUT2        | 0     | Output channel 2                                                                                                                |

| 16   | OUT3        | 0     | Output channel 3                                                                                                                |

| 17   | OUT4        | 0     | Output channel 4                                                                                                                |

| 18   | OUT5        | 0     | Output channel 5                                                                                                                |

| 19   | OUT6        | 0     | Output channel 6                                                                                                                |

| 20   | OUT7        | 0     | Output channel 7                                                                                                                |

| 21   | OUT8        | 0     | Output channel 8                                                                                                                |

| 22   | OUT9        | 0     | Output channel 9                                                                                                                |

| 23   | OUT10       | 0     | Output channel 10                                                                                                               |

| 24   | OUT11       | 0     | Output channel 11                                                                                                               |

# **6** Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                     |                       | MIN  | MAX                         | UNIT |

|-----------------------------------------------------|-----------------------|------|-----------------------------|------|

| SUPPLY                                              | Device supply voltage | -0.3 | 45                          | V    |

| FS                                                  | High-voltage input    | -0.3 | V <sub>(SUPPLY)</sub> + 0.3 | V    |

| OUT0 - 11                                           | High-voltage outputs  | -0.3 | V <sub>(SUPPLY)</sub> + 0.3 | V    |

| ERR                                                 | High-voltage output   | -0.3 | 22                          | V    |

| ADDR2/CLK,<br>ADDR1/PWM1,<br>ADDR0/PWM0,<br>REF, RX | Low-voltage input     | -0.3 | 5.5                         | V    |

| VLDO, TX                                            | Low-voltage output    | -0.3 | 5.5                         | V    |

| TJ                                                  | Junction temperature  | -40  | 150                         | °C   |

| T <sub>stg</sub>                                    | Storage temperature   | -65  | 150                         | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|  |  |  |                                                         |            | VALUE | UNIT |

|--|--|--|---------------------------------------------------------|------------|-------|------|

|  |  |  | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> |            | ±2000 |      |

|  |  |  | Corner pins (RX, REF, OUT0,<br>OUT11)                   | ±750       | V     |      |

|  |  |  |                                                         | Other pins | ±500  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                           |                                                      | MIN | NOM MA              | K UNIT          |

|-------------------------------------------|------------------------------------------------------|-----|---------------------|-----------------|

| SUPPLY                                    | Device supply voltage                                | 4.5 | 3                   | 6 V             |

| IOUT0-IOUT11                              | Channel output current                               | 0.5 | 7                   | 5 mA            |

| FS                                        | External fail-safe selection input                   | 0   | V <sub>(SUPPL</sub> | <sup>()</sup> V |

| ТХ                                        | FlexWire TX output                                   | 0   |                     | 5 V             |

| RX                                        | FlexWire RX input                                    | 0   |                     | 5 V             |

| VLDO                                      | Internal 5V LDO output                               | 0   |                     | 5 V             |

| I <sub>(VLDO)</sub>                       | LDO external current load                            | 0   | 8                   | 0 mA            |

| ADDR2/CLK, ADDR1/<br>PWM1, ADDR0/<br>PWM0 | Device address selection and external CLK/PWM inputs | 0   |                     | 5 V             |

| REF                                       | Current reference setting                            | 0   |                     | 5 V             |

| ERR                                       | Error feedback open-drain output                     | 0   | 2                   | 0 V             |

| t <sub>(r_RX)</sub>                       | RX risetime                                          |     | 5%/f <sub>CL</sub>  | к               |

| t <sub>(f_RX)</sub>                       | RX falltime                                          |     | 5%/f <sub>CL</sub>  | к               |

| f <sub>CLK</sub>                          | FlexWire frequency                                   | 10  | 100                 | 0 kHz           |

| D <sub>SYNC</sub>                         | Synchronization pulse dutycycle                      | 45  | 50 5                | 5 %             |

| T <sub>A</sub>                            | Ambient temperature                                  | -40 | 12                  | 5 °C            |

# 6.3 Recommended Operating Conditions (continued)

over operating free-air temperature range (unless otherwise noted)

|    |                      | MIN | NOM | MAX | UNIT |

|----|----------------------|-----|-----|-----|------|

| TJ | Junction temperature | -40 |     | 150 | °C   |

### **6.4 Thermal Information**

|                       |                                              | TPS929120-Q1 |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | HTSSOP (PWP) | UNIT |

|                       |                                              | 24 PINS      |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 35           | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 26.1         | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 13.7         | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.4          | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 13.6         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.4          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.5 Electrical Characteristics**

T<sub>J</sub> = -40°C to 150°C, V<sub>(SUPPLY)</sub> = 5-40 V, For digital outputs, C<sub>(LOAD)</sub> = 20 pF, (unless otherwise noted).

| PARAMETER                      |                                               | TEST CONDITIONS                                                              | MIN   | TYP   | MAX   | UNIT |

|--------------------------------|-----------------------------------------------|------------------------------------------------------------------------------|-------|-------|-------|------|

| BIAS                           |                                               |                                                                              |       |       | I     |      |

| V <sub>(SUPPLY)</sub>          | Operating input voltage                       |                                                                              | 4.5   | 12    | 40    | V    |

| I <sub>Q(ON)</sub>             | Quiescent current, all-channels-on            | $V_{(SUPPLY)}$ = 12 V, $R_{(REF)}$ =31.6 k $\Omega$ , all-<br>output ON      |       |       | 10    | mA   |

| I <sub>Q(OFF)</sub>            | Quiescent current, all-channels-off           | $V_{(SUPPLY)}$ = 12 V, $R_{(REF)}$ = 31.6 k $\Omega$ , all-output OFF        |       |       | 3.5   | mA   |

| I <sub>(FAULT)</sub>           | Quiescent current, fail-safe state fault mode | V <sub>(SUPPLY)</sub> = 12 V, fail-safe state, all-<br>output OFF, ERR = LOW |       | 2.5   | 2.85  | mA   |

| V <sub>(POR_rising)</sub>      | Power-on-reset rising threshold               |                                                                              | 4     | 4.2   | 4.4   | V    |

| V <sub>(POR_falling)</sub>     | Power-on-reset falling threshold              |                                                                              | 3.8   | 4     | 4.2   | V    |

| V                              | LDO output voltage                            | V <sub>(SUPPLY)</sub> > 5.6 V, I <sub>(LDO)</sub> = 40 mA,<br>CONF_LDO = 0b  | 4.75  | 5     | 5.25  | V    |

| V <sub>(LDO)</sub>             |                                               | V <sub>(SUPPLY)</sub> > 5.6 V, I <sub>(LDO)</sub> = 40 mA,<br>CONF_LDO = 1b  | 4.18  | 4.4   | 4.62  | V    |

| I <sub>(LDO)</sub>             | LDO output current capability                 |                                                                              |       |       | 80    | mA   |

| I(LDO_LIMIT)                   | LDO output current limit                      |                                                                              | 100   |       |       | mA   |

| V <sub>(LDO_DROP)</sub>        | LDO maximum dropout voltage                   | I <sub>(LDO)</sub> = 80 mA                                                   |       | 0.5   | 0.9   | V    |

| V <sub>(LDO_DROP)</sub>        | LDO maximum dropout voltage                   | I <sub>(LDO)</sub> = 50 mA                                                   |       | 0.3   | 0.6   | V    |

| V <sub>(LDO_POR_rising)</sub>  | LDO power-on-reset rising threshold           |                                                                              | 2.75  | 3     | 3.25  | V    |

| V <sub>(LDO_POR_falling)</sub> | LDO power-on-reset falling threshold          |                                                                              | 2.5   | 2.75  | 3     | V    |

| C <sub>(LDO)</sub>             | Supported LDO loading capacitance range       |                                                                              | 1     |       | 10    | μF   |

| f <sub>(OSC)</sub>             | Internal oscillator frequency                 |                                                                              | -2.5% | 32.15 | +2.5% | MHz  |

| ERR                            | •                                             |                                                                              |       |       | I     |      |

| V <sub>IL(ERR)</sub>           | Input logic low voltage, ERR                  |                                                                              |       |       | 0.7   | V    |

| V <sub>IH(ERR)</sub>           | Input logic high voltage, ERR                 |                                                                              | 2     |       |       | V    |

| I(pd_ERR)                      | ERR pull-down current capability              | V <sub>(ERR)</sub> = 0.4 V                                                   | 3     | 6     | 9     | mA   |

# 6.5 Electrical Characteristics (continued)

$T_J = -40^{\circ}C$  to 150°C,  $V_{(SUPPLY)} = 5-40$  V, For digital outputs,  $C_{(LOAD)} = 20$  pF, (unless otherwise noted).

|                         | PARAMETER                                                                                                 | TEST CONDITIONS                                                                                 | MIN               | TYP  | MAX              | UNIT |

|-------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------|------|------------------|------|

| lkg(ERR)                | ERR leakage current                                                                                       |                                                                                                 |                   |      | 1                | μA   |

| FLEXWIRE INT            | ERFACE                                                                                                    |                                                                                                 |                   |      | •                |      |

| V <sub>IL(RX)</sub>     | Input logic low voltage, RX                                                                               |                                                                                                 |                   |      | 0.7              | V    |

| V <sub>IH(RX)</sub>     | Input logic high voltage, RX                                                                              |                                                                                                 | 2                 |      |                  | V    |

| V <sub>OL(TX)</sub>     | Low-level output voltage TX,                                                                              | I <sub>sink</sub> = 5 mA,                                                                       | 0                 |      | 0.3              | V    |

| V <sub>OH(TX)</sub>     | High-level output voltage TX,                                                                             | I <sub>source</sub> = 5 mA, V <sub>pull-up</sub> = 5 V                                          | 4.7               |      | 5                | V    |

| l <sub>ikg</sub>        | TX, RX                                                                                                    |                                                                                                 | -1                |      | 1                | μA   |

| ADDRESS, FS             |                                                                                                           | 1                                                                                               |                   |      | I                |      |

| V <sub>IL(IO)</sub>     | Input logic low voltage, ADDR2/CLK,<br>ADDR1/PWM1, ADDR0/PWM0, FS                                         |                                                                                                 |                   |      | 0.7              | V    |

| V <sub>IH(IO)</sub>     | Input logic high voltage, ADDR2/CLK, ADDR1/PWM1, ADDR0/PWM0, FS                                           |                                                                                                 | 2                 |      |                  | V    |

| R <sub>(PD_ADDR)</sub>  | Internal pull down resistance, ADDR2/<br>CLK, ADDR1/PWM1, ADDR0/PWM0                                      |                                                                                                 |                   | 100  |                  | kΩ   |

| R <sub>(PD_FS)</sub>    | Internal pull down resistance, FS                                                                         |                                                                                                 |                   | 100  |                  | kΩ   |

| ADC                     |                                                                                                           |                                                                                                 |                   |      |                  |      |

| DNL                     | Differential nonlinearity                                                                                 |                                                                                                 | -1 <sup>(1)</sup> |      | 1 <sup>(1)</sup> | LSB  |

| INL                     | Integral nonlinearity                                                                                     |                                                                                                 | -2 <sup>(1)</sup> |      | 2 <sup>(1)</sup> | LSB  |

| OUTPUT DRIV             | ERS                                                                                                       |                                                                                                 |                   |      | I                |      |

| f <sub>(PWM_200)</sub>  |                                                                                                           | 200-Hz selection                                                                                |                   | 200  |                  | Hz   |

| f<br>(PWM_1000)         |                                                                                                           | 1-kHz selection                                                                                 |                   | 1000 |                  | Hz   |

|                         | Device-to-device accuracy ΔI <sub>(OUT_d2d)</sub><br>= 1- I <sub>avg(OUT)</sub> / I <sub>ideal(OUT)</sub> | R <sub>(REF)</sub> = 8.45 kOhm,<br>CONF_REFRANGE = 11b, DC=63                                   | -5                | 0    | 5                |      |

| A1                      |                                                                                                           | R <sub>(REF)</sub> = 8.45 kOhm,<br>CONF_REFRANGE = 10b, DC=63                                   | -5                | 0    | 5                | %    |

| $\Delta I_{(OUT_d2d)}$  |                                                                                                           | R <sub>(REF)</sub> = 8.45 kOhm,<br>CONF_REFRANGE = 01b, DC=63                                   | -5                | 0    | 5                |      |

|                         |                                                                                                           | R <sub>(REF)</sub> = 8.45 kOhm,<br>CONF_REFRANGE = 00b, DC=63                                   | -5                | 0    | 5                |      |

|                         |                                                                                                           | R <sub>(REF)</sub> = 8.45 kOhm,<br>CONF_REFRANGE = 11b, DC=63                                   | -3                | 0    | 3                |      |

| ΔI <sub>(OUT_c2c)</sub> | Channel-to-channel accuracy                                                                               | R <sub>(REF)</sub> = 8.45 kOhm,<br>CONF_REFRANGE = 10b, DC=31                                   | -3                | 0    | 3                | %    |

| <u>     (001_c2c)</u>   | $\Delta I_{(OUT\_c2c)} = 1 - I_{(OUTx)} / I_{avg(OUT)}$                                                   | R <sub>(REF)</sub> = 8.45 kOhm,<br>CONF_REFRANGE = 01b, DC=15                                   | -5                | 0    | 5                | ,,,  |

|                         |                                                                                                           | R <sub>(REF)</sub> = 31.6 kOhm,<br>CONF_REFRANGE = 01b, DC=12                                   | -7                | 0    | 7                |      |

| I <sub>(OUT_75mA)</sub> |                                                                                                           | R <sub>(REF)</sub> = 8.45 kOhm,<br>CONF_REFRANGE = 11b, DC=63                                   |                   | 75   |                  | mA   |

| I <sub>(OUT_50mA)</sub> |                                                                                                           | R <sub>(REF)</sub> = 12.7 kOhm,<br>CONF_REFRANGE = 11b, DC=63                                   |                   | 50   |                  | mA   |

| (OUT_20mA)              |                                                                                                           | R <sub>(REF)</sub> = 31.6 kOhm,<br>CONF_REFRANGE = 11b, DC=63                                   |                   | 20   |                  | mA   |

| I(OUT_1mA)              |                                                                                                           | R <sub>(REF)</sub> = 31.6 kOhm,<br>CONF_REFRANGE = 01b, DC = 12                                 |                   | 1    |                  | mA   |

| V <sub>(OUT_drop)</sub> | output dropout voltage                                                                                    | $R_{(REF)} = 8.45 \text{ kOhm},$<br>CONF_REFRANGE = 11b, DC=38,<br>$I_{(OUTx)} = 45 \text{ mA}$ |                   | 400  | 700              | mV   |

# 6.5 Electrical Characteristics (continued)

$T_J = -40^{\circ}C$  to 150°C,  $V_{(SUPPLY)} = 5-40$  V, For digital outputs,  $C_{(LOAD)} = 20$  pF, (unless otherwise noted).

|                                | PARAMETER                                 | TEST CONDITIONS                                                                               | MIN  | TYP   | MAX  | UNIT |

|--------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------|------|-------|------|------|

| V <sub>(OUT_drop)</sub>        | output dropout voltage                    | R <sub>(REF)</sub> = 8.45 kOhm,<br>CONF_REFRANGE = 11b, DC=63,<br>I <sub>(OUTx)</sub> = 75 mA |      | 600   | 1000 | mV   |

| R <sub>(REF)</sub>             |                                           |                                                                                               | 1    |       | 50   | kΩ   |

| C <sub>(REF)</sub>             |                                           |                                                                                               | 0    |       | 4.7  | nF   |

| V <sub>(REF)</sub>             |                                           |                                                                                               |      | 1.235 |      | V    |

| K <sub>(REF_11)</sub>          |                                           | CONF_REFRANGE = 11b                                                                           |      | 512   |      |      |

| K <sub>(REF_10)</sub>          |                                           | CONF_REFRANGE = 10b                                                                           |      | 256   |      |      |

| K <sub>(REF_01)</sub>          |                                           | CONF_REFRANGE = 01b                                                                           |      | 128   |      |      |

| K <sub>(REF_00)</sub>          |                                           | CONF_REFRANGE = 00b                                                                           |      | 64    |      |      |

| I(REF_OPEN_th)                 |                                           |                                                                                               |      | 10    |      | μA   |

| V <sub>(REF_SHORT_th)</sub>    |                                           |                                                                                               |      | 0.6   |      | V    |

| DIAGNOSTICS                    |                                           |                                                                                               |      |       | •    |      |

| V <sub>(OPEN_th_rising)</sub>  | LED open rising threshold                 | V <sub>(SUPPLY)</sub> - V <sub>(OUTx)</sub>                                                   | 200  | 400   | 600  | mV   |

| V <sub>(OPEN_th_falling)</sub> | LED open falling threshold                | V <sub>(SUPPLY)</sub> - V <sub>(OUTx)</sub>                                                   | 300  | 500   | 700  | mV   |

| V <sub>(OPEN_th_hyst)</sub>    |                                           |                                                                                               |      | 100   |      | mV   |

| V <sub>(SG_th_rising)</sub>    | Short-to-ground rising threshold          |                                                                                               | 0.8  | 0.9   | 1    | V    |

| $V_{(SG_th_falling)}$          | Short-to-ground falling threshold         |                                                                                               | 1.1  | 1.2   | 1.3  | V    |

| V <sub>(SG_th_hyst)</sub>      | Short-to-ground<br>hysteresis             |                                                                                               |      | 0.3   |      | V    |

| EEPROM                         |                                           | 1                                                                                             |      |       |      |      |

| N <sub>(EEP)</sub>             | Number of programming cycles.             | V <sub>(SUPPLY)</sub> = 12 V                                                                  | 1000 |       |      |      |

| MISC                           |                                           |                                                                                               |      |       |      |      |

| T <sub>(PRETSD)</sub>          | Pre-thermal warning threshold             |                                                                                               |      | 135   |      | °C   |

| T <sub>(PRETSD_HYS)</sub>      | Pre-thermal warning hysteresis            |                                                                                               |      | 5     |      | °C   |

| T <sub>(TSD)</sub>             | Over-temperature<br>protection threshold  |                                                                                               | 160  | 175   | 190  | °C   |

| T <sub>(TSD_HYS)</sub>         | Over-temperature<br>protection hysteresis |                                                                                               |      | 15    |      | °C   |

(1) Guaranteed by design only

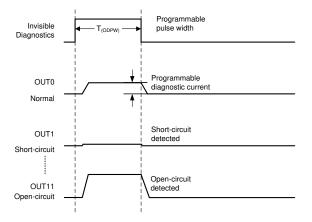

# 6.6 Timing Requirements

|                          |                                           | MIN | NOM | MAX | UNIT |

|--------------------------|-------------------------------------------|-----|-----|-----|------|

| t <sub>(ODPW)</sub>      | Diagnostics pulse-width, CONF_ODPW = 0h   |     | 100 |     | μs   |

| t <sub>(CONV)</sub>      | time needed to complete one AD conversion |     | 57  |     | μs   |

| t <sub>(OPEN_deg)</sub>  | Open-circuit deglitch timer               |     | 5   |     | μs   |

| t <sub>(SHORT_deg)</sub> | Short-circuit deglitch timer              |     | 5   |     | μs   |

| t <sub>(retry)</sub>     | Fault retry timer                         |     | 10  |     | ms   |

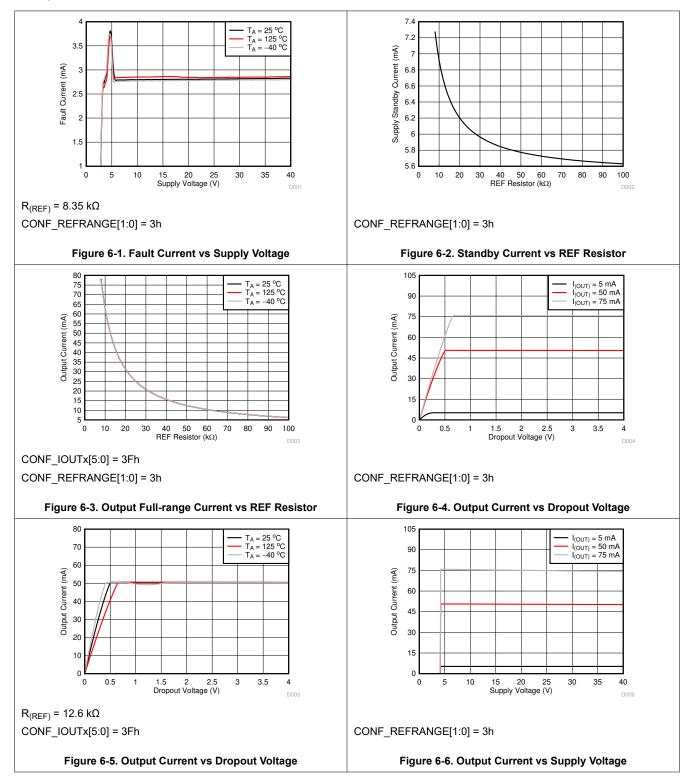

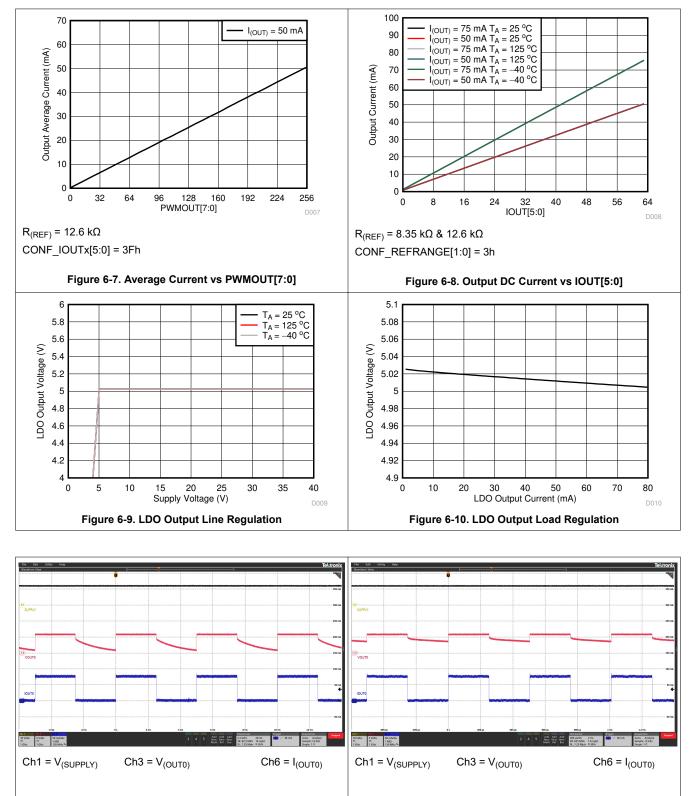

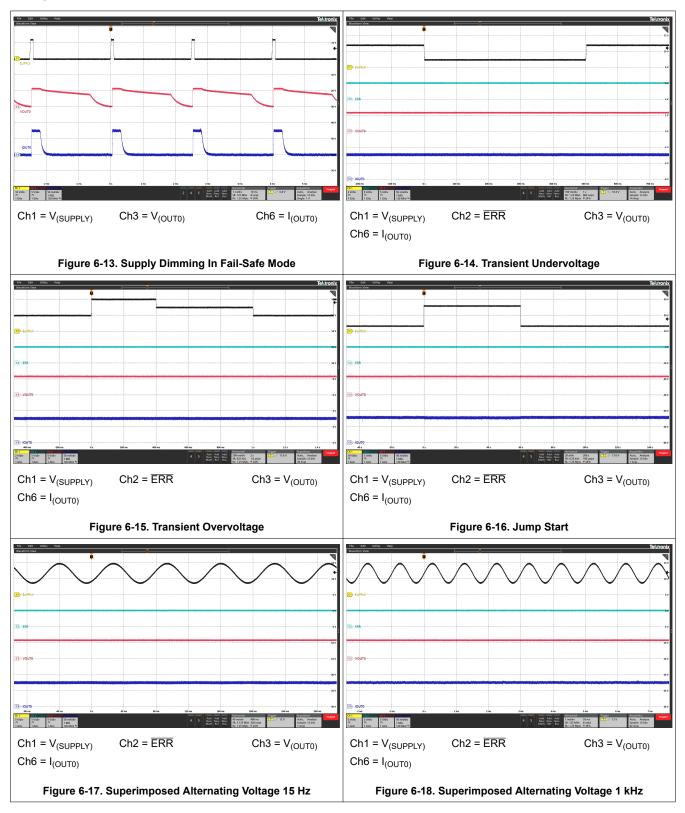

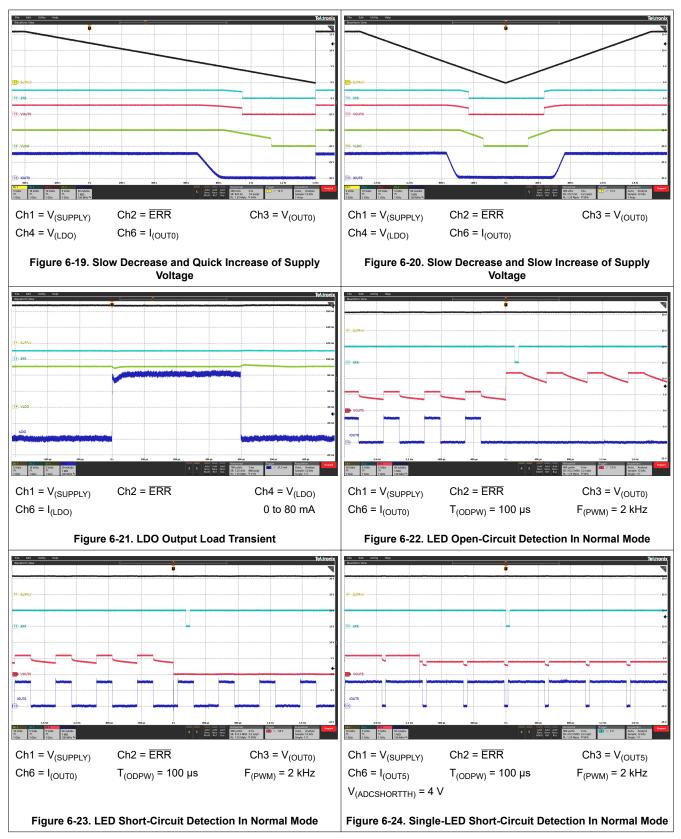

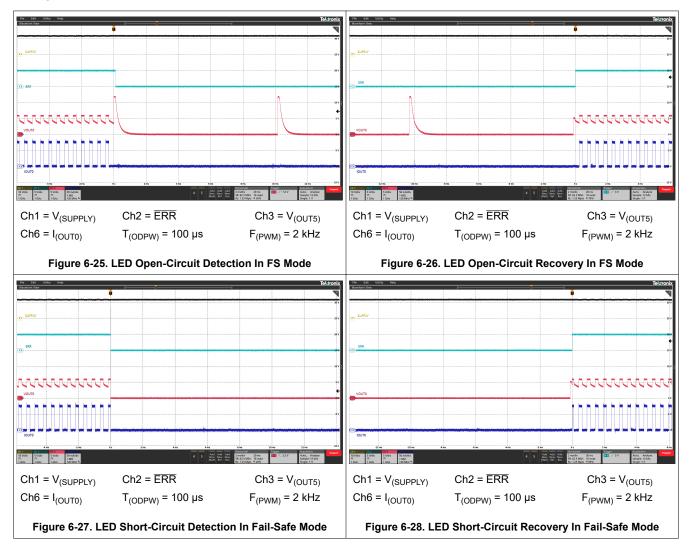

# 6.7 Typical Characteristics

# 6.7 Typical Characteristics

Figure 6-11. PWM Dimming at 200 Hz

Figure 6-12. PWM Dimming at 2000 Hz

# 6.7 Typical Characteristics (continued)

11

# 6.7 Typical Characteristics (continued)

# 6.7 Typical Characteristics (continued)

# 7 Detailed Description

# 7.1 Overview

TPS929120-Q1 is an automotive 12-channel LED driver with FlexWire interface to address increasing requirements for individual control of each LED string. Each of its channel can support both analog dimming and pulse-width-modulation (PWM) dimming, configured through its FlexWire serial interface. The internal electrically erasable programmable read-only memory (EEPROM) allows users to configure device in the scenario of communication loss to fulfill system level safety requirements.

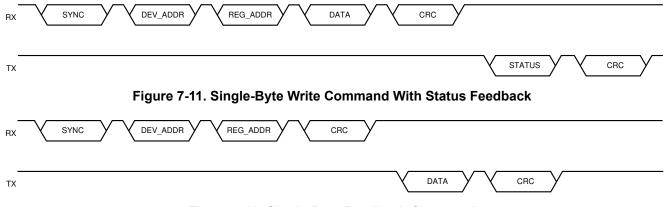

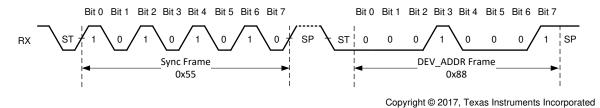

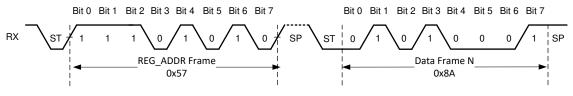

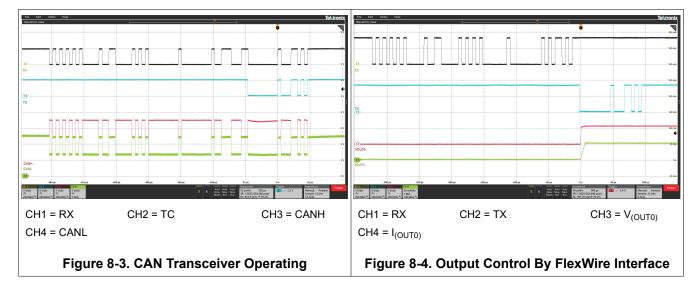

The FlexWire interface is a robust address-based master-slave interface with flexible baud rate. The interface is based on multi-frame universal asynchronous receiver-transmitter (UART) protocol. The unique synchronization frame of FlexWire reduces system cost by saving external crystal oscillators. It also supports various physical layer with the help of external physical layer transceiver such as CAN or LIN transceivers. The embedded CRC correction is able to ensure robust communication in automotive environments. The FlexWire interface is easily supported by most MCUs in the markets.

Each output is a constant current source with individually programmable current output and PWM duty cycle. Each channel features various diagnostics including LED open-circuit, short-circuit and single-LED short-circuit detection. The on-chip analog-digital convertor (ADC) allows controller to real-time monitor loading conditions.

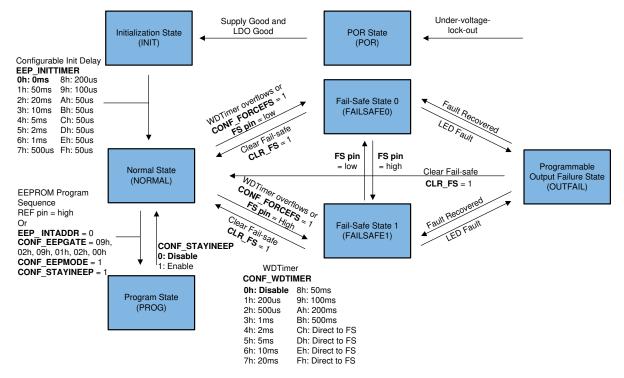

To further increase robustness, the unique fail-safe of the device state machine allows automatic switching to fail-safe states in the case of communication loss, for example, MCU failure. The device supports programming fail-safe settings with user-programmable EEPROM. In fail-safe states, the device supports different configurations if output fails, such as one-fails-all-fail or one-fails-others-on. Each channel can be independently programmed as on or off in fail-safe states. The fail-safe state machine also allows the system to function with pre-programmed EEPROM settings without presence of any controller in the system, also known as stand-alone operation.

The microcontroller can access each of the device through the FlexWire interface. By setting and reading back the registers, the master, which is the microcontroller, has full control over the device and LEDs. All EEPROMs are pre-programmed to default values. TI recommends that users program the EEPROM at the end-of-line for application-specific settings and fail-safe configurations.

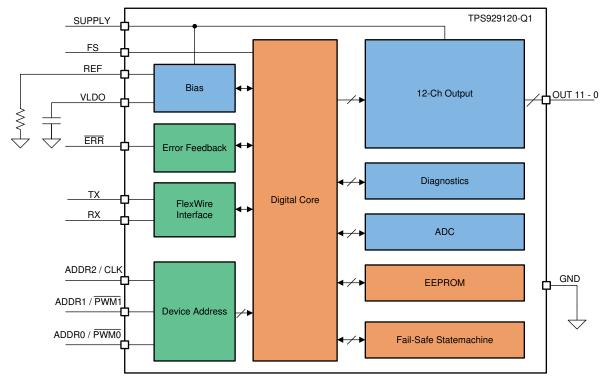

# 7.2 Functional Block Diagram

# 7.3 Feature Description

## 7.3.1 Device Bias and Power

# 7.3.1.1 Power Supply (SUPPLY)

The TPS929120-Q1 is AECQ-100 qualified for automotive applications. The power input to the device through SUPPLY pin can be low to 4.5 V and up to 40 V for automotive battery directly powered systems.

### 7.3.1.2 5-V Low-Drop-Out Linear Regulator (VLDO)

The TPS929120-Q1 has an integrated low-drop-out linear regulator to provide power supply to external CAN transceivers, such as TCAN1042. The internal LDO powered by supply voltage  $V_{(SUPPLY)}$  provides a stable 5-V output with up to 80-mA constant current capability. TI recommends a ceramic capacitor from 1 µF to 10 µF on the VLDO pin. The LDO has an internal current limit  $I_{(LDO\_LIMIT)}$  for protection and soft start. The capacitor charging time must be considered to total start-up time period, because the device is held in POR state if the capacitor voltage is not charged to above UVLO threshold.

### 7.3.1.3 Undervoltage Lockout (UVLO) and Power-On-Reset (POR)

In order to ensure clean start-up, the TPS929120 uses UVLO and POR circuitry to clear its internal registers upon power-up and to reset registers with its default values.

The TPS929120-Q1 has internal UVLO circuits so that when either power supply voltage  $V_{(SUPPLY)}$  or LDO output voltage  $V_{(LDO)}$  is lower than its UVLO threshold, POR is triggered. In POR state, the device resets digital core and all registers to default value. FLAG\_POR register is set to 1 for each POR cycle to indicate the POR history.

Before both powers are above UVLO thresholds, the TPS929120-Q1 stays in POR state with all outputs off and ERR pulled down. Once both power supplies are above UVLO threshold, the device enters INIT mode for initialization releasing ERR pulldown. A programmable timer starts counting in INIT state, the timer length can be set by EEPROM register EEP\_INITTIMER. When the timer is completed, the device switches to normal state. In INIT state, setting CLR\_POR to 1 clears FLAG\_POR, disables the timer, and sets the device to normal state.

Upon powering up, the TPS929120-Q1 automatically loads all settings stored in EEPROM to correlated registers and sets the other registers to default value which don't have correlated EEPROM. All channels are powered up in off-state by default to avoid unwanted blinking.

Writing 1 to CLR\_REG manually loads EEPROM setting to the correlated registers and set the other registers to default value. After CLR\_REG is set, the FLAG\_POR is set 1 to indicate registers clear to default values. Writing 1 to CLR\_POR resets the FLAG\_POR register to 0. TI recommends setting CLR\_REG to 1 to clear the internal registers every time after POR. The CLR\_REG automatically resets to 0.

### 7.3.1.4 Programmable Low Supply Warning

The TPS929120-Q1 uses its internal ADC to monitor supply voltage  $V_{(SUPPLY)}$ . If the supply is below allowable working threshold, the output voltage may not be sufficient to keep the LED operating with desired brightness output as expected. The ADC output is automatically compared with threshold set by register CONF\_ADCLOWSUPTH as described in *Register Maps*. When the supply voltage is below threshold, the device sets warning flag register FLAG\_ADCLOWSUP to 1 in the status register. CLR\_FAULT is able to clear the FLAG\_ADCLOWSUP as well as other fault registers. In addition, the LED open-circuit and single LED short-circuit detection is disabled if the supply voltage is below threshold to avoid LED open circuit and to prevent the single LED short-circuit fault from being mis-triggered. The 4-bit register CONF\_ADCLOWSUPTH has total 15 options covering from 5 V to 20 V.

### 7.3.2 Constant Current Output

### 7.3.2.1 Reference Current With External Resistor (REF)

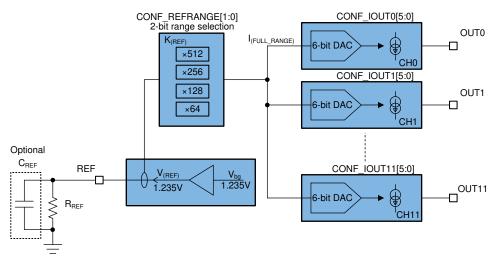

The TPS929120-Q1 must have an external resistor  $R_{(REF)}$  to set the internal current reference  $I_{(REF)}$  as shown in Figure 7-1.

Figure 7-1. Output Current Setting

The internal current reference  $I_{(FULL\_RANGE)}$  is generated based on the  $I_{(REF)}$  multiplied by factor  $K_{(REF)}$  to provide the full range current reference for each OUTx channel. The  $K_{(REF)}$  is programmable by 2-bit register CONF\_REFRANGE with 4 different options. The  $I_{(FULL\_RANGE)}$  can be calculated with Equation 1.

$$I_{(FULL\_RANGE)} = \frac{V_{(REF)}}{R_{(REF)}} \times K_{(REF)}$$

where

- V<sub>(REF)</sub> = 1.235 V typically

- K<sub>(REF)</sub> = 64, 128, 256, or 512 (default)

(1)

The recommended resistor values of  $R_{(REF)}$  and amplifier ratios of  $K_{(REF)}$  are listed in Table 7-1.

| CONF_REFRA | V                  | FULL RANGE CURRENT (mA)      |                              |                              |  |

|------------|--------------------|------------------------------|------------------------------|------------------------------|--|

| NGE        | K <sub>(REF)</sub> | R <sub>(REF)</sub> = 8.45 kΩ | R <sub>(REF)</sub> = 12.7 kΩ | R <sub>(REF)</sub> = 31.6 kΩ |  |

| 11b        | 512                | 75                           | 50                           | 20                           |  |

| 10b        | 256                | 37.5                         | 25                           | 10                           |  |

| 01b        | 128                | 18.75                        | 12.5                         | 5                            |  |

| 00b        | 64                 | 9.375                        | 6.25                         | 2.5                          |  |

| Table 7-1 | Reference    | Current | Range | Setting |

|-----------|--------------|---------|-------|---------|

|           | I CICICICICC | ouncil  | Range | ocuing  |

Place the  $R_{(REF)}$  resistor as close as possible to the REF pin with an up to 2.2-nF ceramic capacitor in parallel to improve the noise immunity. The off-board  $R_{(REF)}$  setup is not allowed due to the concern of instability reference current. TI recommends a 1-nF ceramic capacitor in parallel with  $R_{(REF)}$ .

### 7.3.2.2 64-Step Programmable High-Side Constant-Current Output

TPS929120-Q1 has 12 channels of high-side current sources. Each channel has its own enable configuration register CONF\_ENCHx. Setting CONF\_ENCHx to 1 enables the channel output; clearing the register to 0 disables the channel output. To completely turn off the channel current, user can clear channel enable bit CONF\_ENCHx to 0. Upon power up, CONF\_ENCHx is automatically reset to 0 to avoid unwanted blinking.

Each OUTx channel supports individual 64-step programmable current setting, also known as dot correction (DC). The DC feature can be used to set binning values for output LEDs or to calibrate the LEDs to achieve high brightness homogeneity based on external visual system to further save binning cost. The 6-bit register CONF\_IOUTx sets the current independently, where x is the channel number from 0 to 11. The OUTx current can be calculated with Equation 2

$$I_{(OUTx)} = \frac{(CONF\_IOUTx + 1)}{64} \times I_{(FULL\_RANGE)}$$

where

- CONF\_IOUTx is programmable from 0 to 63

- x is from 0 to 11 for different output channel

- I<sub>(FULL RANGE)</sub> can be calculated with Equation 1

# 7.3.3 PWM Dimming

TPS929120-Q1 integrates independent 12-bit PWM generators for each OUTx channel. The current output for each OUTx channel is turned on and off controlled by the integrated PWM generator. The average current of each OUTx can be adjusted by PWM duty cycle independently, therefore, to control the brightness for LEDs in each channel.

# 7.3.3.1 PWM Dimming Frequency

The frequency for PWM dimming is programmable by 4-bit register CONF\_PWMFREQ with 16 options covering from 200 Hz to 20.8 kHz. Select the frequency for PWM dimming based on the minimum brightness requirement in application. TPS929120-Q1 supports down to 1-µs minimum pulse current for all 12 channel outputs.

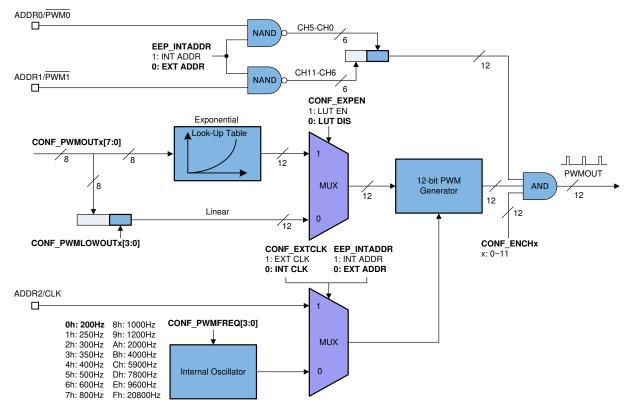

# 7.3.3.2 PWM Generator

The 12-bit PWM generator constructs the cyclical PWM output based on a 12-bit digital binary input to control the output current ON and OFF. Basically the PWM generator counts 256 pulses at base high frequency for PWM output cycle period and counts number of pulses determined by MSB 8 bits of 12-bit binary input at the same frequency for PWM ON period. The LSB 4 bits of 12-bit binary input is used to set up the dithering to realize total 12-bit resolution. The base high frequency is generated by internal oscillator, which is 256 times of the frequency programmable by CONF\_PWMFREQ. Figure 7-2 is the signal path diagram for PWM generator.

(2)

### 7.3.3.3 Linear Brightness Control

When register CONF\_EXPEN is set to 0, the MSB 8 bits of 12-bit binary input to PWM generator is directly copied from 8-bit register CONF\_PWMOUTx, and the LSB 4 bits is directly copied from 4-bit register CONF\_PWMLOWOUTx. The PWM output duty cycle can be calculated with Equation 3. Because the 4 LSB bits inputs are used to control the dithering, setting CONF\_PWMLOWOUTx to Fh disables the dithering if it is not needed. The PWM output duty cycle is linearly controlled by the register CONF\_PWMOUTx and CONFPWMLOWOUTx, which provides the linearly brightness control to each channel output.

$$D_{(OUTx)} = \frac{(16 \times CONF_PWMOUTx + CONF_PWMLOWOUTx + 1)}{4096} \times 100\%$$

(3)

where

- CONF\_PWWOUTx is decimal number from 0 to 255.

- CONF\_PWMLOWOUTx is decimal number from 0 to 15.

- x is from 0 to 11 for different output channel

If using the dithering feature to realize the 12-bit dimming resolution, set the PWM frequency higher than 2 kHz through setting register CONF\_PWMFREQ to avoid visible brightness flicker when the value of CONF\_PWMLOWOUTx is less than Fh. Higher PWM frequency can also prevent the visible LED flash in video display due to the low beat frequency between digital camera shutter frequency and PWM frequency for LED dimming.

Because the 12-bit PWM duty cycles require 2 bytes of write operation to update the completed data, the output PWM duty cycle is not changed in between of the two bytes data transmission. TPS929120-Q1 only updates PWM duty cycle of any output when its high 8-bit CONF\_PWMOUTx is written. When very fast brightness change is needed, for example, fade-in and fade-out effects, simultaneous PWM duty cycle change of all

channels is required. Setting CONF\_SHAREPWM to 1 enables all channels using the PWM dutycycle setting of channel 0 to save communication latency.

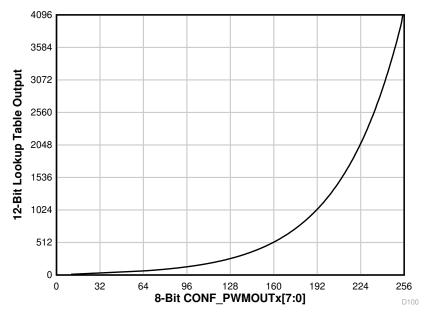

### 7.3.3.4 Exponential Brightness Control

The TPS929120-Q1 can also generate PWM duty-cycle output following exponential curve. The integrated lookup table provides a one-to-one conversion from 8-bit register CONF\_PWMOUTx to 12-bit binary code following exponential increment when register CONF\_EXPEN is set to 1 as Figure 7-3 illustrated. When exponential control path is selected, the CONF\_PWMLOWOUTx data is neglected. By using the exponential brightness control, LED brightness change by one LSB is invisible to human eyes especially at low brightness range.

Figure 7-3. PWM Duty Cycle vs 8-bit Code for Exponential Dimming

CONF\_EXPEN bit selects the dimming method between linear or exponential. Setting the bit CONF\_EXPEN to 1 enables the look-up table for exponential dimming curve. In exponential PWM dimming mode, 8-bit register CONF\_PWMOUTx is converted to 12-bit PWM dutycycle by look-up table automatically. Clear the bit CONF\_EXPEN to 0 disables the look-up table. In this case, users must provide 12-bit PWM duty cycle. CONF\_PWMOUTx stores the high 8-bit of 12-bit PWM duty-cycle information. CONF\_PWMLOWOUTx stores the low 4-bit.

To avoid visible brightness flicker for exponential dimming, choose PWM frequency higher than 2 kHz through setting register CONF\_PWMFREQ. Higher PWM frequency can also avoid the visible LED flash in video display due to the low beat frequency between digital camera shutter frequency and PWM frequency for LED dimming.

During power-up or in fail-safe state, the registers CONF\_EXPEN, CONF\_PWMOUTx, CONF\_PWMFREQ are automatically reset to their default values stored in EEPROM register EEP\_EXPEN, EEP\_PWMOUTx, EEP\_PWMFREQ. CONF\_PWMLOWOUTx is reset to Fh as default value.

In fail-safe state, PWM generator only uses 8-bit EEPROM data from EEP\_PWMOUTx to build PWM dutycycle output and ignores the low 4-bit. The PWM duty-cycle calculation is as shown in Equation 4.

$$D_{(OUTx)} = \frac{(EEP_PWMOUTx+1)}{256} \times 100\%$$

where

- EEP\_PWMOUTx is decimal number from 0 to 255.

- x is from 0 to 11 for different output channel

(4)

### 7.3.3.5 External Clock Input for PWM Generator (CLK)

The TPS929120-Q1 has internal precision oscillator for PWM generators. In addition, the device also supports an external clock for the PWM generator source with ADDR2/CLK input considering the synchronization requirement.

Then external clock inputs through ADDR2/CLK pin is a multi-function pin not only for external clock input but also for device slave address selection. The device slave address stored in EEPROM must be enabled by burning EEP\_INTADDR to 1 to release ADDR2/CLK pin for external clock input. In addition, register CONF\_EXTCLK can be used to choose the PWM generator between external input or an internal oscillator. Writing CONF\_EXTCLK to 1 enables the external clock source. The external clock frequency must be 256 times of desired PWM dimming frequency. The external clock source is only used in PWM generation. TI recommends that the external clock frequency be less than 1 MHz. The internal clock is recommended when high dimming frequency is required.

### 7.3.3.6 External PWM Input ( PWM0 and PWM1)

The TPS929120-Q1 has two PWM inputs that can be used to directly control OUT0-11. The both ADDR1/ PWM1 and ADDR0/ PWM0 pins are multi-function pins for not only external PWM input signal but also device slave address selection pins. The register EEP\_INTADDR must be written to 1 to release both twos for external PWM input. When the EEP\_INTADDR is 1, the ADDR0/ PWM0 is functional as external active low PWM control input for OUT0-5 and the ADDR1/ PWM1 is functional as external active low PWM control input for OUT6-11, as shown in Figure 7-2. Setting the register CONF\_PWMOUTx to 0xFF and the register CONF\_PWMLOWOUTx to 0xF is recommended when external PWM input is used. In case external PWM is not used, ADDR0/ PWM0 and ADDR1/ PWM1 must be tied to GND when EEP\_INTADDR is set to 1.

### 7.3.4 On-chip 8-bit Analog-to-Digital Converter (ADC)

The TPS929120-Q1 has integrated a successive-approximation-register (SAR) ADC for diagnostics. It routinely monitors supply voltage if the ADC is idle and stores SUPPLY conversion results into ADC\_SUPPLY.

To manually read the voltage of an ADC channel as listed in Table 7-2, user must write the 5-bit register CONF\_ADCCH to select channel. Once CONF\_ADCCH register is written, the one time ADC conversion starts and clears FLAG\_ADCDONE register. As long as the ADC conversion is completed, the ADC result is available in 8-bit register ADC\_OUT and sets FLAG\_ADCDONE to 1. Reading the ADC\_OUT register also clears FLAG\_ADCDONE, and the FLAG\_ADCDONE is set to 0 after reading completion.

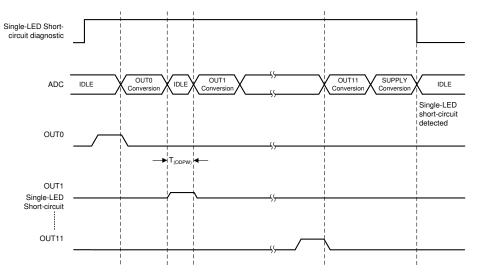

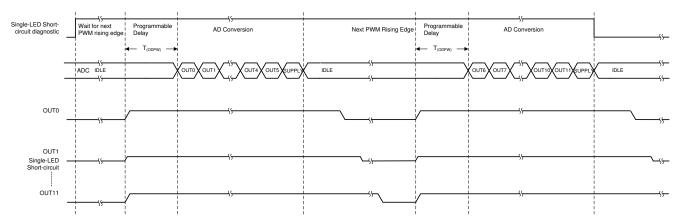

Because the TPS929120-Q1 supports PWM control for adjusting LED brightness, the voltage on OUT0 to OUT11 is like a pulse waveform. When the current output is enabled by setting CONF\_ENCHx to 1, the ADC measures the voltage on assigned OUTx after the channel is turned on with  $t_{(diag_pulse)}$  delay time, which is programmable by 4-bit register CONF\_ODPW. When the channel is disabled by setting CONF\_ENCHx to 0, the ADC samples the voltage on assigned OUTx at off state.

The analog value can be calculated based on the read back binary code with Equation 5 and Table 7-2.

Analog Value =

$$a + k \times (ADC_OUT)$$

(5)

where

• ADC\_OUT is decimal number from 0 to 255.

| Table 7-2. ADC Channel |            |          |                                        |                                        |                                |  |

|------------------------|------------|----------|----------------------------------------|----------------------------------------|--------------------------------|--|

| CHANNEL<br>NO.         | CONF_ADCCH | NAME     | ADC<br>CALCULATION<br>PARAMETER<br>(a) | ADC<br>CALCULATION<br>PARAMETER<br>(k) | COMMENT                        |  |

| 0                      | 00h        | REF      | 0.007 V                                | 0.0101 V/LSB                           | Reference voltage              |  |

| 1                      | 01h        | SUPPLY   | 0.0673 V                               | 0.0804 V/LSB                           | Supply voltage                 |  |

| 2                      | 02h        | VLDO     | 0.0465 V                               | 0.022 V/LSB                            | 5V LDO output voltage          |  |

| 3                      | 03h        | TEMPSNS  | –242.35°C                              | 2.152°C/LSB                            | Internal temperature sensor    |  |

| 4                      | 04h        | IREF     | 0.7592 µA                              | 0.7461 µA/LSB                          | Reference current              |  |

| 5                      | 05h        | MAXOUT   | 0.0673 V                               | 0.0804 V/LSB                           | Maximum channel output voltage |  |

| 6-15                   | 06h - 0Fh  | RESERVED | RESERVED                               | RESERVED                               | RESERVED                       |  |

| 16                     | 10h        | OUT0     |                                        |                                        | Output voltage channel 0       |  |

| 17                     | 11h        | OUT1     |                                        |                                        | Output voltage channel 1       |  |

| 18                     | 12h        | OUT2     |                                        |                                        | Output voltage channel 2       |  |

| 19                     | 13h        | OUT3     |                                        |                                        | Output voltage channel 3       |  |

| 20                     | 14h        | OUT4     |                                        |                                        | Output voltage channel 4       |  |

| 21                     | 15h        | OUT5     | 0.0673 V                               | 0.0804 V/LSB                           | Output voltage channel 5       |  |

| 22                     | 16h        | OUT6     | 0.0073 V                               | 0.0004 V/LSB                           | Output voltage channel 6       |  |

| 23                     | 17h        | OUT7     |                                        |                                        | Output voltage channel 7       |  |

| 24                     | 18h        | OUT8     |                                        |                                        | Output voltage channel 8       |  |

| 25                     | 19h        | OUT9     |                                        |                                        | Output voltage channel 9       |  |

| 26                     | 1Ah        | OUT10    |                                        |                                        | Output voltage channel 10      |  |

| 27                     | 1Bh        | OUT11    | 1                                      |                                        | Output voltage channel 11      |  |

| 28                     | 1Ch        | RESERVED | RESERVED                               | RESERVED                               | RESERVED                       |  |

| 29                     | 1Dh        | RESERVED | RESERVED                               | RESERVED                               | RESERVED                       |  |

| 30                     | 1Eh        | RESERVED | RESERVED                               | RESERVED                               | RESERVED                       |  |

| 31                     | 1Fh        | RESERVED | RESERVED                               | RESERVED                               | RESERVED                       |  |

The TPS929120-Q1 also provides ADC auto-scan mode for single-led short-circuit diagnostics. The detail description for auto-scan mode can be found in *On-Demand Off-State Single-LED Short-Circuit (SS) Diagnostics*.

In ADC auto-scan mode, If MAXOUT channel is selected by writing 05h to CONF\_ADCCH, the maximum voltage of OUT0 to OUT11 is recorded into ADC\_OUT register. The maximum channel output voltage is available after at least one output PWM cycle is completed. Based on the measured maximum output voltage and supply voltage, microcontroller is able to regulate supply voltage from previous power stage to minimize the power consumption on the TPS929120-Q1. Basically microcontroller needs to program the output voltage of previous power stage to be just higher than the measured maximum channel output voltage plus the required dropout voltage  $V_{(OUT_drop)}$  of the TPS929120-Q1. In this way, the TPS929120-Q1 takes minimum power consumption, and overall power efficiency is optimized.

### 7.3.5 Diagnostic and Protection in Normal State

The TPS929120-Q1 has full-diagnostics coverage for supply voltage, current output, and junction temperature.

In normal state, the device detects all failures and reports the status out through the ERR or FLAG registers, without any actions taken by the device except UVLO and overtemperature protection. The master controller must handle all fault actions, for example, retry several times and shut down the outputs if the error still exists. The fault behavior in normal state can be found in Table 7-3.

### 7.3.5.1 Fault Masking

The TPS929120-Q1 provides fault masking capability using masking registers. The device is capable of masking faults by channels or by fault types. The fault masking does not disable diagnostics features but only prevents fault reporting to FLAG\_OUT register, FLAG\_ERR register, and ERR output.

To disable diagnostics on a single channel, setting CONF\_DIAGENCHx registers to 0 disables diagnostics of channel x and thus no fault of this channel is reported to FLAG\_OUT or FLAG\_ERR registers, or to the ERR output.

CONF\_MASKREF prevents the reference fault being reported to FLAG\_ERR and ERR output.

CONF\_MASKOPEN prevents the output open-circuit fault being reported to FLAG\_OUT, FLAG\_ERR and ERR output.

CONF\_MASKSHORT prevents the output short-circuit fault being reported to FLAG\_OUT, FLAG\_ERR and ERR output.

CONF\_MASKTSD prevents the overtemperature shutdown fault being reported to FLAG\_ERR and ERR output.

CONF\_MASKCRC prevents the CRC fault being reported to FLAG\_ERR and ERR output.

### 7.3.5.2 Supply Undervoltage Lockout Diagnostics in Normal State

When SUPPLY or VLDO voltage drops below its UVLO threshold, the device enters POR state. Upon voltage recovery, the device automatically switches to INIT state with FLAG\_POR and FLAG\_ERR set to 1.

### 7.3.5.3 Low-Supply Warning Diagnostics in Normal State

The internal AD converter of TPS92910-Q1 continuously monitors the supply voltage and compares the results with internal threshold  $V_{(ADCLOWSUPTH)}$  set by CONF\_ADCLOWSUPTH as described in *Register Maps*. If the supply voltage is lower than threshold, the device pulls ERR pin down with one pulsed current sink for 50 µs to report the fault and set flag registers including FLAG\_ADCLOWSUP to 1. The master controller can write register CLR\_FAULT to 1 to reset this flag, and the CLR\_FAULT bit automatically returns to 0. The internal ADC monitors supply voltage and converters to 8-bit binary code in every conversion cycle  $T_{(CONV)}$  when it is in idle. After each AD conversion-cycle time on supply, the ADC\_SUPPLY is automatically updated with the latest result.

The low-supply warning is also used to disable the LED open-circuit detection and single-LED short-circuit detection. When the voltage applied on SUPPLY pin is higher than the threshold  $V_{(ADCLOWSUPTH)}$ , the TPS929120-Q1 enables LED open-circuit and single-LED short-circuit diagnosis. When  $V_{(SUPPLY)}$  is lower than the threshold  $V_{(ADCLOWSUPTH)}$ , the device disables LED-open-circuit detection and single-LED short-circuit diagnosis. Because when  $V_{(SUPPLY)}$  drops below the maximum total LED forward voltage plus required  $V_{(DROPOUT)}$  at required current, the TPS929120-Q1 is not able to deliver sufficient current output to pull the voltage of each output channel as close as possible to the  $V_{(SUPPLY)}$ . In this condition, the LED open-circuit fault or single-LED short-circuit fault might be detected and reported by mistake. Setting the low-supply warning threshold high enough can avoid the LED open-circuit and single LED short-circuit fault being detected when  $V_{(SUPPLY)}$  drops to low. The  $V_{(ADCLOWSUPTH)}$  is programmable from 5 V to 20 V.

### 7.3.5.4 Reference Diagnostics in Normal State

The TPS929120-Q1 integrates diagnostics for REF resistor open/short fault. If the current output from REF pin  $I_{(REF)}$  is lower than  $I_{(REF_OPEN_th)}$ , the reference resistor open-circuit fault is reported. The reference resistor short-circuit fault is reported if the voltage of REF pin  $V_{(REF)}$  is lower than  $V_{(REF_SHORT_th)}$ . The device pulls the

ERR pin down with constant current sink and set flag registers including FLAG\_REF and FLAG\_ERR to 1. The master controller must send CLR\_FAULT to clear fault flag registers after fault removal.

In normal state, the device does not perform any actions automatically when reference resistor fault is detected. However, the output may not work properly and the output current may be operating at high current level. It is recommended for master controller to shut down the device outputs and report error to upper level control system such as body control module (BCM).

The TPS929120-Q1 monitors the reference current  $I_{(REF)}$  set by external resistor  $R_{(REF)}$ . The  $I_{(REF)}$  can be calculated with Equation 6.

$$I_{(REF)} = \frac{V_{(REF)}}{R_{(REF)}}$$

(6)

# where

• V<sub>(REF)</sub> = 1.235 V typically

# 7.3.5.5 Pre-Thermal Warning and Overtemperature Protection in Normal State

The TPS929120-Q1 has pre-thermal warning at typical 135°C and overtemperature shutdown at typical 175°C.

When the junction temperature  $T_{(J)}$  of TPS929120-Q1 rises above pre-thermal warning threshold, the device reports pre-thermal warning, pull ERR pin with pulsed current sink for 50 µs and sets the flag registers including FLAG\_PRETSD to 1. The master controller must write 1 to CLR\_FAULT register to clear FLAG\_PRETSD.

When device junction temperature  $T_{(J)}$  further rises above overtemperature protection threshold, the device shuts down all output drivers, pulls the  $\overline{ERR}$  pin low with constant current sink, and sets the flag registers including FLAG\_TSD and FLAG\_ERR to 1. When junction temperature falls below  $T_{(TSD)} - T_{(TSD_HYS)}$ , the device resumes all outputs and releases  $\overline{ERR}$  pin pulldown. The FLAG\_TSD still must be cleared by writing CLR\_FAULT to 1.

If the  $T_{(J)}$  rises too high above 180°C typically, the TPS929120-Q1 turns off the internal linear regulator to shutdown all the analog and digital circuit. When the  $T_{(J)}$  drops below  $T_{(TSD)} - T_{(TSD_HYS)}$ , the TPS929120-Q1 restarts from POR state with all the registers cleared to default value.

When more accurate thermal measurement on LED unit is required, one current output channel can be sacrificed to provide current bias to external thermal resistor such as PTC or NTC. The voltage of external thermal resistor can be measured by integrated ADC to acquire the temperature information of thermal resistor located area. The master controller can determine actions based on the acquired temperature information to turn off or reduce current output.

# 7.3.5.6 Communication Loss Diagnostic in Normal State

The TPS929120-Q1 monitors the FlexWire interface for the communication with an internal watchdog timer. Any successful non-broadcast communication with correct CRC and address matching target device automatically resets the timer. If the watchdog timer overflows, device automatically switches to fail-safe state as indicated by external FS input. If FS = 0, the device switches to fail-safe state 0, If FS = 1, the device switches to fail-safe state 1.

The watchdog timer is programmable by 4-bit register CONF\_WDTIMER. The TPS929120-Q1 can directly enter fail-safe states from normal mode by burning EEP\_WDTIMER to 0xFh. Disabling the watchdog timer by setting CONF\_WDTIMER to 0x0h prevents the device from getting into fail-safe state.

# 7.3.5.7 LED Open-Circuit Diagnostics in Normal State

The TPS929120-Q1 integrates LED open-circuit diagnostics to allow users to monitor LED status real time. The device monitors voltage difference between SUPPLY and OUTx to judge if there is any open-circuit failure. The SUPPLY voltage is also monitored by on-chip ADC with programmable threshold to determine if supply voltage is high enough for open-circuit diagnostics.

The open-circuit monitor is only enabled during PWM-ON state with programmable minimal pulse width greater than  $T_{(ODPW)} + T_{(OPEN\_deg)}$ . The  $T_{(ODPW)}$  is programmed by register CONF\_ODPW. If PWM on-time is less than  $T_{(ODPW)} + T_{(OPEN\_deg)}$ , the device does not report any open-circuit fault.

When the voltage difference  $V_{(SUPPLY)} - V_{(OUTx)}$  is below threshold  $V_{(OPEN\_th\_rising)}$  with duration longer than  $T_{(ODPW)} + T_{(OPEN\_deg)}$ , and the device supply voltage  $V_{(SUPPLY)}$  is above the threshold  $V_{(ADCLOWSUPTH)}$  set by register CONF\_ADCLOWSUPTH, the TPS929120-Q1 pulls the ERR pin down with one pulsed current sink for 50 µs to report fault and set flag registers including FLAG\_OPENCHx, FLAG\_OUT and FLAG\_ERR to 1. If the device supply voltage  $V_{(SUPPLY)}$  is below the threshold  $V_{(ADCLOWSUPTH)}$  set by register CONF\_ADCLOWSUPTH, open-circuit fault is not detected nor reported.

Once the open-circuit failure is removed, the master controller must write 1 to CLR\_FAULT to reset fault flags.

### 7.3.5.8 LED Short-circuit Diagnostics in Normal State

The TPS929120-Q1 has internal analog comparators to monitor all channel outputs with respect to a fixed threshold. If the device has detected channel voltage below threshold, it sets FLAG\_SHORTCHx accordingly. The FLAG\_OUT and FLAG\_ERR are set as well. Writing 1 to CLR\_FAULT register is able to clear the fault flag registers.

The short-circuit detection is only enabled during PWM-ON state with programmable minimal pulse width of  $T_{(ODPW)} + T_{(SHORT_deg)}$ . The  $T_{(ODPW)}$  is programmable by register CONF\_ODPW. If PWM on-time is less than  $T_{(ODPW)} + T_{(SHORT_deg)}$ , the device can not report any short-circuit fault. When the voltage  $V_{(OUTx)}$  is below threshold  $V_{(SG_th_rising)}$  with duration longer than deglitch timer length of  $T_{(ODPW)} + T_{(SHORT_deg)}$ , the device pulls ERR pin down with pulsed current sink for 50 µs to report fault and set flag registers including FLAG\_SHORTCHx, FLAG\_OUT and FLAG\_ERR. In normal state, the device does not take any actions in response the LED short-circuit fault and waits for the master controller to detect need for protection behavior. The fault is latched in flag registers. The master controller must write 1 to register CLR\_FAULT to reset fault flags if the LED short-circuit fault is removed.

Possible user case:

- 1. Supply voltage dip below threshold, triggering false single led short-circuit fault.

- 2. LED short to ground and recover

- 3. LED single LED short and recover

- 4. Dutycycle too short to detect

- 5. Extra capacitance caused false short-circuit

### 7.3.5.9 On-Demand Off-State Invisible Diagnostics

It is commonly required to ensure there is no fault on each LED load before lighting them up, especially for LED animation. Otherwise, the LED fault is detected in the middle of the admiration pattern, which results a random and uncertain failure animation pattern. The TPS929120-Q1 provides a solution to diagnose the LED opencircuit or LED short-circuit fault without lighting up the LEDs. With this feature, the master controller can initiate the on-demand invisible diagnostics before commencing the animation sequence. If one of the channel fails, the device is able to detect it immediately instead of only when the fault channel is turned on in traditional diagnostics mode. To initiate the on-demand invisible diagnostics, the master controller writes register CONF\_INVDIAGSTART to 1. The register CONF\_INVDIAGSTART returns to 0 automatically in the next clock cycle. Once the diagnostics started, the on-demand diagnostics ready flag FLAG\_ODREADY is cleared to 0. Once the diagnostics finished, the FLAG\_ODREADY is set to 1. If any channel has output failures, its on-demand diagnostic flag FLAG\_ODDIAGCHx is set 1.

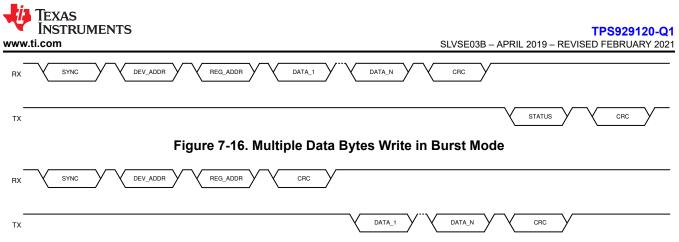

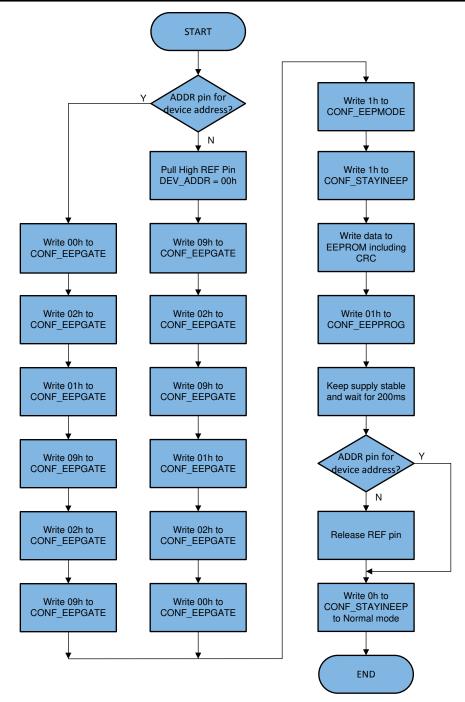

To ensure the invisibility of the diagnostics, the TPS929120-Q1 outputs only a small DC current in short period to each output channel and detects if there is any LED open-circuit or LED short-circuit failures. The output DC current  $I_{(ODIOUT)}$  can be adjusted to a proper value by setting the DC current CONF\_ODIOUT and ignoring the DC current setup by register CONF\_IOUTx. The pulse-width  $T_{(ODPW)}$  of output DC current can be programmable by CONF\_ODPW and neglecting duty cycle configuration by register CONF\_PWMOUTx. At the end of the current output pulse, if there is any LED open-circuit fault as Section 7.3.5.7 described, the TPS929120-Q1 pulls