## Freescale Semiconductor Technical Data

# **Eight Output Switch with Serial Peripheral Interface I/O**

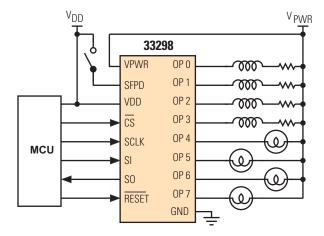

The 33298 is a smart eight-output low-side power switch. It is a versatile device incorporating an 8-bit serial-in shift register to control an 8-bit parallel output latch providing control of eight independent "ON/OFF" output switches. Applications include the control of solenoids, relays, lamps, small DC-motors, and other moderate current loads (1.0 - 3.0 A).

The 33298 interfaces directly with a microcontroller to control various inductive or incandescent loads. Input control is fast. Data rates are guaranteed to 2.0 MHz but the device is capable of rates to 8.5 MHz @  $25^{\circ}$ C.

Each output uses high-efficiency MOSFET power transistors configured with open drains. Each low "ON" resistance output (0.4  $\Omega$   $R_{DS(ON)} @ 25^{\circ}C$ ) is capable of sinking up to 3.0 A of transient current. On a continuous basis, each output can simultaneously (with all outputs "ON") handle 0.5 A of current when the device is soldered onto a typical PC board. Higher output currents are dependent on the number of outputs simultaneously "ON". The circuit's innovative monitoring and protection features include very low standby current.

## Features

- Designed to Operate Over Wide Supply Voltages of 5.5 to 26.5 V

- Interfaces to Microprocessor Using 8-Bit SPI I/O Protocol up to 3.0 MHz

- 1.0 A Peak Current Outputs with Maximum  $R_{DS(on)}$  of 1.6  $\Omega$  at  $T_J$  150°C

- · Outputs Current Limited to Accommodate In-rush Currents Associated with Switching Incandescent Loads

- Output Voltages Clamped to 53 V During Inductive Switching

- Maximum Sleep Current (I<sub>PWR</sub>) of 25 μA

- Maximum of 4.0 mA I<sub>DD</sub> During Operation

- Pb-Free Packaging Designated by Suffix Code EG

Figure 1. 33298 Simplified Application Diagram

Freescale Semiconductor, Inc. reserves the right to change the detail specifications, as may be required, to permit improvements in the design of its products. © Freescale Semiconductor, Inc., 2007. All rights reserved.

33298

## LOW-SIDE SWITCH

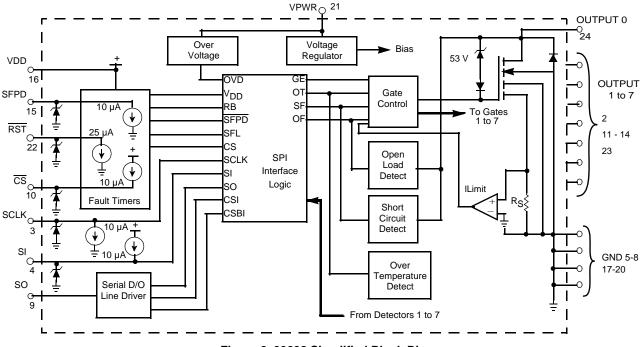

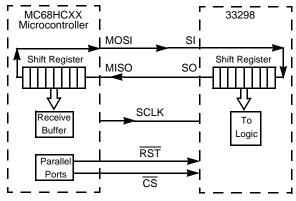

# INTERNAL BLOCK DIAGRAM

## Figure 2. 33298 Simplified Block Diagram

## Table 1. Fault Operation

## SERIAL OUTPUT (SO) PIN REPORTS

| Overvoltage                 | Overvoltage condition reported                                                                                                                                                                                         |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overtemperature             | Fault reported by Serial Output (SO) pin                                                                                                                                                                               |

| Overcurrent                 | SO pin reports short to battery/supply or over current condition                                                                                                                                                       |

| Output ON, Open Load Fault  | Not reported                                                                                                                                                                                                           |

| Output OFF, Open Load Fault | SO pin reports output OFF open load condition                                                                                                                                                                          |

| DEVICE SHUTDOWNS            |                                                                                                                                                                                                                        |

| Overvoltage                 | Total device shutdown at $V_{PWR}$ = 28 to 36 V. All outputs are latched off while the SPI register is reset (cleared). Outputs can be turned back on with a new SPI command after $V_{PWR}$ has decayed below 26.5 V. |

| Overtemperature             | Only the output experiencing an overtemperature condition turns off.                                                                                                                                                   |

| Overtemperature | Only the output experiencing an overtemperature condition turns off.                                                                                                                                                                                                                                                             |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overcurrent     | Only the output experiencing an over current shuts down at 1.0 to 3.0 A after a 70 to 250 µs delay, with SFPD pin grounded. All other outputs will continue to operate in a current limit mode, with no shutdown, if the SFPD pin is at 5.0 V (so long as the individual outputs are not experiencing thermal limit conditions). |

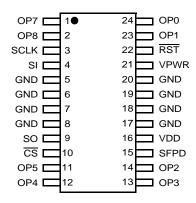

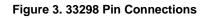

## **PIN CONNECTIONS**

Table 2. 33298 Pin Function Description

| Pin Number | Pin Name         | Formal Name                    | Definition                                                                                                                                                        |

|------------|------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | OP7              | Output 7                       | This pin provides connection to drain of output MOSFET number seven.                                                                                              |

| 2          | OP6              | Output 6                       | This pin provides connection to drain of output MOSFET number six.                                                                                                |

| 3          | SCLK             | System Clock                   | This pin clocks the internal Shift registers of the 33298.                                                                                                        |

| 4          | SI               | Serial Input                   | This pin is for the input of serial instruction data. SI information is read on the falling edge of SCLK.                                                         |

| 5          | GND              | Ground                         | This pin provides connection to IC Power Ground and functions as part of heat sinking path.                                                                       |

| 6          | GND              | Ground                         | This pin provides connection to IC Power Ground and functions as part of heat sinking path.                                                                       |

| 7          | GND              | Ground                         | This pin provides connection to IC Power Ground and functions as part of heat sinking path.                                                                       |

| 8          | GND              | Ground                         | This pin provides connection to IC Power Ground and functions as part of heat sinking path.                                                                       |

| 9          | SO               | Serial Output                  | This pin is the <i>tri-stateable</i> output from the Shift register.                                                                                              |

| 10         | CS               | Chip Select                    | Whenever this pin is in a logic low state, data can be transferred from the MCU to the 33298 through the SI pin and from the 33298 to the MCU through the SO pin. |

| 11         | OP5              | Output 5                       | This pin provides connection to drain of output MOSFET number five.                                                                                               |

| 12         | OP4              | Output 4                       | This pin provides connection to drain of output MOSFET number four.                                                                                               |

| 13         | OP3              | Output 3                       | This pin provides connection to drain of output MOSFET number three.                                                                                              |

| 14         | OP2              | Output 2                       | This pin provides connection to drain of output MOSFET number two.                                                                                                |

| 15         | SFPD             | Short Fault<br>Protect Disable | This pin is used to prevent the outputs from latching-OFF because of an over current condition.                                                                   |

| 16         | V <sub>DD</sub>  | Logic Supply                   | Logic Supply.                                                                                                                                                     |

| 17         | GND              | Ground                         | This pin provides connection to IC Power Ground and functions as part of heat sinking path.                                                                       |

| 18         | GND              | Ground                         | This pin provides connection to IC Power Ground and functions as part of heat sinking path.                                                                       |

| 19         | GND              | Ground                         | This pin provides connection to IC Power Ground and functions as part of heat sinking path.                                                                       |

| 20         | GND              | Ground                         | This pin provides connection to IC Power Ground and functions as part of heat sinking path.                                                                       |

| 21         | V <sub>PWR</sub> | Power                          | Output MOSFET Gate Drive Supply.                                                                                                                                  |

| 22         | RST              | RESET                          | This pin is active low. It is used to clear the SPI Shift register, thereby setting all output switches OFF.                                                      |

| Pin Number | Pin Name | Formal Name | Definition                                                          |

|------------|----------|-------------|---------------------------------------------------------------------|

| 23         | OP1      | Output 1    | This pin provides connection to drain of output MOSFET number one.  |

| 24         | OP0      | Output 0    | This pin provides connection to drain of output MOSFET number zero. |

Table 2. 33298 Pin Function Description (continued)

# **ELECTRICAL CHARACTERISTICS**

## **MAXIMUM RATINGS**

#### Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                                          | Symbol                 | Value         | Unit |

|---------------------------------------------------------------------------------|------------------------|---------------|------|

| Power Supply Voltage                                                            |                        |               | V    |

| Normal Operation (Steady-State)                                                 | V <sub>PWR(SS)</sub>   | - 1.5 to 26.5 |      |

| Transient Conditions <sup>(1)</sup>                                             | V <sub>PWR(PK)</sub>   | - 13 to 60    |      |

| Logic Supply Voltage <sup>(2)</sup>                                             | V <sub>DD</sub>        | - 0.3 to 7.0  | V    |

| Input pin Voltage <sup>(3)</sup>                                                | V <sub>IN</sub>        | - 0.3 to 7.0  | V    |

| Output Clamp Voltage <sup>(4)</sup>                                             | V <sub>OUT(OFF)</sub>  |               | V    |

| $2.0 \text{ mA} \le I_{OUT} \le 0.5 \text{ A}$                                  |                        | 50 to 75      |      |

| Output Self-Limit Current                                                       | I <sub>OUT(LIM)</sub>  | 3.0 to 6.0    | А    |

| Continuous Per Output Current <sup>(5)</sup>                                    | I <sub>OUT(CONT)</sub> | 1.0           | А    |

| ESD Voltage <sup>(6)</sup>                                                      |                        |               | V    |

| Human Body Model <sup>(7)</sup>                                                 | V <sub>ESD1</sub>      | 2000          |      |

| Machine Model <sup>(7)</sup>                                                    | V <sub>ESD2</sub>      | 200           |      |

| Output Clamp Energy <sup>(8)</sup>                                              | E <sub>CLAMP</sub>     |               |      |

| Repetitive:                                                                     |                        |               |      |

| $T_J = 25^{\circ}C$                                                             |                        | 100           | mJ   |

| $T_J = 124^{\circ}C$                                                            |                        | 30            | mJ   |

| Non-Repetitive:                                                                 |                        |               |      |

| $T_{\rm J} = 25^{\circ} \rm C$                                                  |                        | 2.0           | J    |

| $T_{J} = 124^{\circ}C$                                                          |                        | 0.5           | J    |

| Recommended Frequency of SPI Operation <sup>(9)</sup>                           | f <sub>SPI</sub>       | 2.0           | MHz  |

| Storage Temperature                                                             | T <sub>STG</sub>       | - 55 to 150   | °C   |

| Peak Package Reflow Temperature During Reflow <sup>(10)</sup> , <sup>(11)</sup> | T <sub>PPRT</sub>      | Note 11.      | °C   |

Notes

1. Transient capability with external 100  $\Omega$  resistor in series with VP pin and supply.

2. Exceeding these limits may cause a malfunction or permanent damage to the device.

3. Exceeding the limits on SCLK, SI, CS, SFPD, or RST pins may cause permanent damage to the device.

4. With output OFF.

Continuous output current rating so long as maximum junction temperature is not exceeded. Operation at 125°C ambient temperature will require maximum output current computation using package R<sub>0JA</sub>.

- 6. ESD data available upon request.

- 7. ESD1 testing is performed in accordance with the Human Body Model ( $C_{Zap} = 200 \text{ pF}$ ,  $R_{Zap} = 1500 \Omega$ ), ESD2 testing is performed in accordance with the Machine Model ( $C_{Zap} = 200 \text{ pF}$ ,  $R_{Zap} = 0 \Omega$ ).

- 8. Maximum output clamp energy capability at 150°C junction temperature using a single non-repetitive pulse method.

- 9. Guaranteed and production tested for 2.0 MHz SPI operation, but demonstrated to operate to 8.5 MHz at 25°C.

- 10. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

## Table 4. Maximum Ratings (continued)

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                             | Symbol           | Value       | Unit |

|--------------------------------------------------------------------|------------------|-------------|------|

| Operating Case Temperature                                         | T <sub>C</sub>   | - 40 to 125 | °C   |

| Operating Junction Temperature <sup>(12)</sup>                     | ТJ               | - 40 to 150 | °C   |

| Power Dissipation ( $T_A = 25^{\circ}C$ ) <sup>(13)</sup>          | PD               | 3.0         | W    |

| Thermal Resistance (Junction-to-Ambient)<br>Case 738 Package       | R <sub>θJA</sub> |             | °C/W |

| All Outputs ON <sup>(15)</sup>                                     |                  | 31          |      |

| Single Output ON <sup>(15)</sup><br>Case 751E Package              |                  | 37          |      |

| All Outputs ON <sup>(14)</sup><br>Single Output ON <sup>(15)</sup> |                  | 34<br>40    |      |

Notes

12. See Figure 20 for Thermal model.

Soldering temperature limit is for 10 seconds maximum duration; not designed for immersion soldering; exceeding these limits may cause malfunction or permanent damage to the device.Contact Freescale Semiconductor Sales Office for device immersion soldering time/temperature limits.

14. Thermal resistance from Junction-to-Ambient with all outputs ON and dissipating equal power.

15. Thermal resistance from Junction -to-Ambient with a single output ON.

## STATIC ELECTRICAL CHARACTERISTICS

#### **Table 5. Static Electrical Characteristics**

Characteristics noted under conditions 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, 9.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, unless otherwise noted. Typical values noted reflect the approximate value with V<sub>Bat</sub> = 13 V, T<sub>A</sub> = 25°C.

| Characteristic                                                                   | Symbol                | Min | Тур  | Мах  | Unit            |

|----------------------------------------------------------------------------------|-----------------------|-----|------|------|-----------------|

| POWER INPUT                                                                      |                       |     | 1    | 1    |                 |

| Supply Voltage Range                                                             |                       |     |      |      | V               |

| Quasi-Functional <sup>(16)</sup>                                                 | V <sub>PWR(QF)</sub>  | 5.5 | —    | 9.0  |                 |

| Fully Operational                                                                | V <sub>PWR(FO)</sub>  | 9.0 | -    | 26.5 |                 |

| Supply Current (All Outputs ON, $I_{OUT} = 0.5 \text{ A}$ ) <sup>(17)</sup>      | V <sub>PWR(ON)</sub>  | _   | 1.0  | 2.0  | V               |

| Sleep State Supply Current ( $V_{DD} = 0.5 V$ )                                  | I <sub>PWR(SS)</sub>  | _   | 1.0  | 50   | μA              |

| Sleep State Output Leakage Current (per Output, $\overline{V}_{DD} = 0.5V$ )     | I <sub>OUT(SS)</sub>  | _   | —    | 50   | μA              |

| Over Voltage Shutdown                                                            | V <sub>OV</sub>       | 28  | _    | 36   | V               |

| Over Voltage Shutdown Hysteresis                                                 | V <sub>OV(HYS)</sub>  | 0.2 | —    | 1.5  | V               |

| Logic Supply Voltage                                                             | V <sub>DD</sub>       | 4.5 | —    | 5.5  | V               |

| Logic Supply Current (with any combination of Outputs ON)                        | I <sub>DD</sub>       | _   | _    | 4.0  | mA              |

| Logic Supply Under Voltage Lockout Threshold (18)                                | V <sub>DD(UVLO)</sub> | 2.0 | —    | 4.5  | V               |

| POWER OUTPUT                                                                     |                       |     |      |      |                 |

| Drain-to-Source ON Resistance (I <sub>OUT</sub> = 0.5 A, T <sub>J</sub> = 25°C)  | RDS(ON)               |     |      |      | Ω               |

| V <sub>PWR</sub> = 5.5 V                                                         |                       | _   | _    | 10   |                 |

| V <sub>PWR</sub> = 9.0 V                                                         |                       | _   | 0.4  | 0.5  |                 |

| V <sub>PWR</sub> = 13 V                                                          |                       | _   | 0.35 | 0.45 |                 |

| Drain-to-Source ON Resistance (I <sub>OUT</sub> = 0.5 A, T <sub>J</sub> = 150°C) | RDS(ON)               |     |      |      | Ω               |

| V <sub>PWR</sub> = 5.5 V                                                         | -(- )                 | _   | _    | 1.8  |                 |

| V <sub>PWR</sub> = 9.0 V                                                         |                       | _   | 7.5  | 0.9  |                 |

| V <sub>PWR</sub> = 13 V                                                          |                       | _   | 0.65 | 0.8  |                 |

| Output Self-Limiting Current                                                     | I <sub>OUT(LIM)</sub> |     |      |      | А               |

| Outputs Programmed ON, $V_{OUT} = 0.6 V_{DD}$                                    |                       | 3.0 | 4.0  | 6.0  |                 |

| Output Fault Detect Threshold <sup>(19)</sup>                                    | V <sub>OUTth(F)</sub> |     |      |      | V <sub>DD</sub> |

| Output Programmed OFF                                                            |                       | 0.6 | 0.7  | 0.8  |                 |

| Output OFF Open Load Detect Current (20)                                         | l <sub>oco</sub>      |     |      |      | μA              |

| Output Programmed OFF, $V_{OUT}$ = 0.6 $V_{DD}$                                  |                       | 30  | 50   | 100  |                 |

| Output Clamp Voltage                                                             | V <sub>OK</sub>       |     |      |      | V               |

| $2.0 \text{ mA} \le I_{OUT} \le 200 \text{ mA}$                                  |                       | 50  | 60   | 75   |                 |

| Output Leakage Current ( $V_{DD} \le 2.0 \text{ V}$ ) <sup>(21)</sup>            | I <sub>OUT(LKG)</sub> | -50 | 0    | 50   | μA              |

Notes

16. SPI inputs and outputs operational; Fault status reporting may not be fully operational within this voltage range.

17. Value reflects normal operation (no faults) with all outputs ON. Each ON output contributes approximately 20 µA to I<sub>PWR</sub>. Each output experiencing a *soft short* condition contributes approximately 0.5 mA to I<sub>PWR</sub>. A *soft short* is defined as any load current causing the output source current to self-limit. A *hard* output short is a very low impedance short to supply.

18. For V<sub>DD</sub> less than the Under Voltage Lockout Threshold voltage, all data registers are reset and all outputs are disabled.

19. Output Fault Detect Threshold with outputs programmed OFF. Output fault detect thresholds are the same for output opens and shorts.

20. Output OFF Open Load Detect Current is the current required to flow through the load for the purpose of detecting the existence of an open load condition when the specific output is commanded to be OFF.

21. Output leakage current measured with the output OFF and at 16 V.

## Table 6. Static Electrical Characteristics (continued)

Characteristics noted under conditions 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, 9.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, unless otherwise noted. Typical values noted reflect the approximate value with V<sub>PWR</sub> = 13 V, T<sub>A</sub> = 25°C.

| Characteristic                                                                                                | Symbol                | Min                    | Тур                    | Max | Unit            |

|---------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|------------------------|-----|-----------------|

| Over Temperature Shutdown (Outputs OFF) (22)                                                                  | T <sub>LIM</sub>      | 155                    | 170                    | 185 | °C              |

| Over Temperature Shutdown Hysteresis (22)                                                                     | T <sub>LIM(HYS)</sub> | -                      | 10                     | 20  | °C              |

| DIGITAL INTERFACE                                                                                             |                       |                        |                        |     |                 |

| Input Logic High Voltage <sup>(23)</sup>                                                                      | V <sub>IH</sub>       | 0.7                    | —                      | 1.0 | V <sub>DD</sub> |

| Input Logic Low Voltage (24)                                                                                  | V <sub>IL</sub>       | 0                      | —                      | 0.2 | V <sub>DD</sub> |

| Input Logic Voltage Hysteresis (25)                                                                           | V <sub>I(HYS)</sub>   | 50                     | 100                    | 500 | mV              |

| Input Logic Current <sup>(26)</sup>                                                                           | I <sub>IN</sub>       | -10                    | 0                      | 10  | μA              |

| $\overline{\text{RST}}$ Pull-Up Current ( $\overline{\text{RST}}$ = 0.7 V <sub>DD</sub> )                     | IRST                  | 10                     | 22                     | 50  | μA              |

| SFPD Pull-Down Current (SFPD = $0.2 V_{DD}$ )                                                                 | I <sub>SFPD</sub>     | 10                     | 22                     | 50  | μA              |

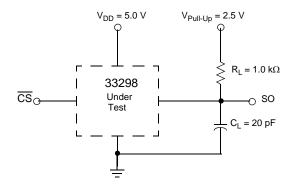

| SO High State Output Voltage ( $I_{\overline{OH}}$ = 1.0 mA)                                                  | V <sub>SOH</sub>      | V <sub>DD</sub> -1.0 V | V <sub>DD</sub> -0.6 V | _   | V               |

| SO Low State Output Voltage (I <sub>OL</sub> = -1.6 mA)                                                       | V <sub>SOL</sub>      | —                      | 0.2                    | 0.4 | V               |

| SO Tri-State Leakage Current ( $\overline{CS}$ = 0.7 VDD, 0 V $\leq$ V <sub>SO</sub> $\leq$ V <sub>DD</sub> ) | I <sub>SOT</sub>      | -10                    | 0                      | 10  | μA              |

| Input Capacitance (0 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V) <sup>(27)</sup>                                   | C <sub>IN</sub>       | —                      | —                      | 12  | pF              |

| SO Tri-State Capacitance (0 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V) <sup>(28)</sup>                            | C <sub>SOT</sub>      | —                      | —                      | 20  | pF              |

Notes

22. This parameter is guaranteed by design, but it is not production tested.

23. Upper and lower logic threshold voltage levels apply to SI, CS, SCLK, RST, and SFPD inputs.

24. Lower logic threshold voltage range applies to SI, CS, SCLK, Reset, and SFPD input signals.

25. Only the SFPD and Reset inputs have hysteresis. This parameter is guaranteed by design, but it is not production tested.

26. Input current of SCLK, SI and  $\overline{CS}$  logic control inputs.

27. Input capacitance of SI, CS, SCLK, RST, and SFPD for 0 V ≤ VDD ≤ 5.5 V. This parameter is guaranteed by design, but it is not production tested.

28. Tri-state capacitance of SO for 0 V ≤ VDD ≤ 5.5 V. This parameter is guaranteed by design, but it is not production tested.

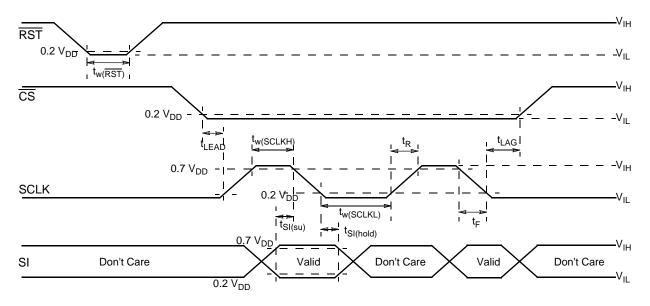

## DYNAMIC ELECTRICAL CHARACTERISTICS

#### **Table 7. Dynamic Electrical Characteristics**

Characteristics noted under conditions 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, 9.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                     | Symbol                | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|-----|------|

| POWER OUTPUT TIMING                                                                                                |                       |     |     |     |      |

| Output Rise Time (V <sub>PWR</sub> = 13 V, R <sub>L</sub> = 26 $\Omega$ ) <sup>(29)</sup>                          | t <sub>R</sub>        | 0.4 | 1.5 | 20  | μs   |

| Output Fall Time (V <sub>PWR</sub> = 13 V, R <sub>L</sub> = 26 $\Omega$ ) <sup>(29)</sup>                          | t <sub>F</sub>        | 0.4 | 2.5 | 20  | μs   |

| Output Turn ON Delay Time (V <sub>PWR</sub> = 13 V, R <sub>L</sub> = 26 $\Omega$ ) <sup>(30)</sup>                 | t <sub>DLY(ON)</sub>  | 1.0 | 5.0 | 15  | μs   |

| Output Turn-OFF Delay Time (V <sub>PWR</sub> = 13 V, R <sub>L</sub> = 26 $\Omega$ ) <sup>(31)</sup>                | t <sub>DLY(OFF)</sub> | 1.0 | 5.0 | 15  | μs   |

| Output Short Fault Disable Report Delay <sup>(32)</sup><br>SFPD = 0.2 x V <sub>DD</sub>                            | <sup>t</sup> DLY(SF)  | 25  | 50  | 100 | μs   |

| Output OFF Fault Report Delay $^{(33)}$<br>SFPD = 0.2 x V <sub>DD</sub>                                            | <sup>t</sup> DLY(OFF) | 25  | 50  | 100 | μs   |

| DIGITAL INTERFACE TIMING                                                                                           | ·                     |     |     |     |      |

| SCLK Clock Period <sup>(34)</sup>                                                                                  | t <sub>pSCLK</sub>    | 500 |     | _   | ns   |

| SCLK Clock High Time                                                                                               | t <sub>wSCLKH</sub>   | 175 | —   | _   | ns   |

| SCLK Clock Low Time                                                                                                | twSCLKL               | 175 | —   | _   | ns   |

| Required Low State Duration for $\overline{\text{Reset}}$ (V <sub>IL</sub> < 0.2 V <sub>DD</sub> ) <sup>(35)</sup> | t <sub>w(RST)</sub>   | 250 | 50  | _   | ns   |

| Falling Edge of $\overline{\text{CS}}$ to Rising Edge of SCLK (Required Setup Time)                                | t <sub>LEAD</sub>     | 250 | 50  | —   | ns   |

| Falling Edge of SCLK to Rising Edge of $\overline{CS}$ (Required for Setup Time)                                   | t <sub>LAG</sub>      | 250 | 50  | —   | ns   |

| SI to Falling Edge of SCLK (Required for Setup Time)                                                               | t <sub>SISU</sub>     | 125 | 25  | —   | ns   |

| Falling Edge of SCLK to SI (Required for Hold Time)                                                                | t <sub>SI(HOLD)</sub> | 125 | 25  | —   | ns   |

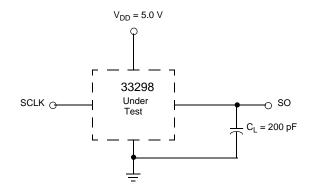

| SO Rise Time (C <sub>L</sub> = 200 pF)                                                                             | t <sub>rSO</sub>      | _   | 25  | 75  | ns   |

| SO Fall Time (C <sub>L</sub> = 200 pF)                                                                             | t <sub>fSO</sub>      | _   | 25  | 75  | ns   |

| SI, CS, SCLK, Incoming Signal Rise Time <sup>(36)</sup>                                                            | t <sub>rSI</sub>      | _   | —   | 200 | ns   |

| SI, $\overline{\text{CS}}$ , SCLK, Incoming Signal Fall Time <sup>(36)</sup>                                       | t <sub>fSI</sub>      | —   | —   | 200 | ns   |

| Time from Falling Edge of $\overline{CS}$ to SO Low Impedance <sup>(37)</sup>                                      | t <sub>SO(EN)</sub>   | —   | _   | 200 | ns   |

| Time from Rising Edge of $\overline{CS}$ to SO High Impedance <sup>(38)</sup>                                      | t <sub>SO(DIS)</sub>  |     | _   | 200 | ns   |

Notes

29. Output Rise and Fall time respectively measured across a 26 Ω resistive load at 10 to 90 percent, and 90 to 10 percent voltage points.

30. Output Turn ON Delay time measured from 50 percent rising edge of  $\overline{CS}$  to 90 percent of Output OFF voltage (V<sub>PWR</sub>) with R<sub>L</sub> = 26  $\Omega$  resistive load.

31. Output Turn OFF Delay time measured from 50 percent rising edge of  $\overline{CS}$  to 10 percent of Output OFF voltage (V<sub>PWR</sub>) with R<sub>L</sub> = 26  $\Omega$  resistive load.

- 32. Output Short Fault Delay time measured from rising edge of CS to  $I_{OUT}$  = 2.0 A point with output ON,  $V_{OUT}$  = 5.0 V, and SFPD = 0.2 x  $V_{DD}$ . See Figures 8 and 10.

- 33. Output OFF Fault Report Delay measured from 50 percent rising edge of  $\overline{CS}$  to rising edge of output. See Figure 9.

- 34. Clock period include 75 ns rise plus 75 ns fall transition in addition to clock high and low time.

- 35. RST Low duration measured with outputs enabled and going to OFF or disabled condition.

- 36. Rise and Fall time of incoming SI, CS, and SCLK signals suggested for design consideration to prevent the occurrence of double pulsing.

- 37. Time required for output status data to be available for use at the SO pin.

- 38. Time required for output status data to be terminated at the SO pin.

ELECTRICAL CHARACTERISTICS DYNAMIC ELECTRICAL CHARACTERISTICS

## Table 7. Dynamic Electrical Characteristics

$Characteristics noted under conditions 4.5 \ V \le V_{DD} \le 5.5 \ V, 9.0 \ V \le V_{PWR} \le 16 \ V, -40^{\circ}C \le T_A \le 125^{\circ}C, unless otherwise noted.$ Typical values noted reflect the approximate parameter mean at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                   | Symbol             | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|-----|------|

| Time from Rising Edge of SCLK to SO Data Valid <sup>(39)</sup>                                                   | t <sub>VALID</sub> |     |     |     | ns   |

| $0.2 \text{ V}_{\text{DD}} \leq \text{SO} \geq 0.8 \text{ V}_{\text{DD}}, \text{ C}_{\text{L}} = 200 \text{ pF}$ |                    |     | 50  | 125 |      |

Notes

39. Time required to obtain valid data out from SO following the rise of SCLK. See Figure 5.

## TIMING DIAGRAMS

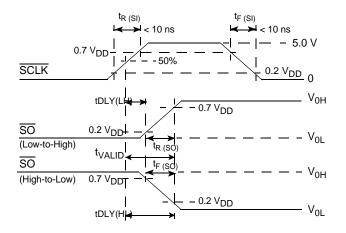

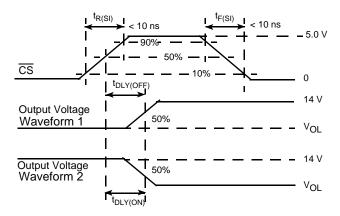

Figure 4. Input Timing Switch Characteristics

## **ELECTRICAL PERFORMANCE CURVES**

ρεπρεσεντσ τηε τοταλ χαπαχιτανχε οφ τηε τεστ φιξτυρε ανδ προβε

C<sub>L</sub> represents the total capacitance of the test fixture and probe.

# Figure 5. Valid Data Delay Time and Valid Time Test Circuit

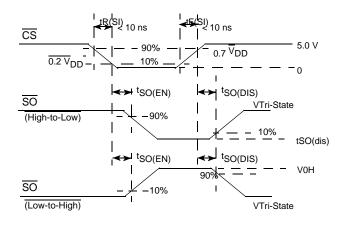

Figure 6. Enable and Disable Time Test Circuit

SO (Low-to-High) is for an output with internal conditions such that the low-to-high transition of  $\overline{CS}$  causes the SO output to switch from high to low.

# Figure 7. Valid Data Delay Time and Valid Time Waveforms

- SO (high-to-low) waveform is for SO output with internal conditions such that SO output is low except when an output is disabled as a result of detecting a circuit fault with CS in a High Logic state, e.g. open load.

- SO (low-to-high) waveform is for SO output with internal conditions such that SO output is high except when an output is disabled as a result of detecting a circuit fault with CS in a High Logic state, e.g. shortened load.

#### Figure 8. Enable and Disable Time Waveforms

$C_{L}$  represents the total capacitance of the test fixture and probe.

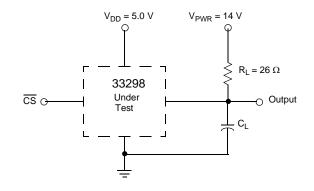

Figure 9. Switching Time Test Circuit

$C_L$  represents the total capacitance of the test fixture and probe.

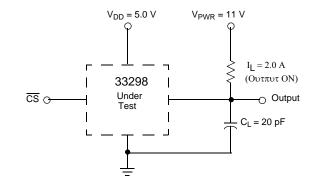

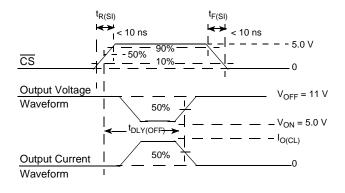

#### Figure 10. Output Fault Unlatch Disable Delay Test Circuit

1.  ${}^t\!\text{DLY}(\text{ON})$  and  ${}^t\!\text{DLY}(\text{OFF})$  are turn-on and turn-off propagation delay times.

2. Turn-off is an output programmed from an ON to an OFF state.

3. Turn-on is an output programmed from and OFF to an ON state.

#### Figure 11. Turn-On/Off Waveforms

1.  $t_{PDLY(OFF)}$  is the output fault unlatch disable propagation delay time required to correctly report an output fault after  $\overline{CS}$  rises. It represents an output commanded ON while having an existing output short (over current) to supply.

2. The SFPD pin  $\leq$  0.2 V

#### Figure 12. Output Fault Unlatch Disable Delay Waveforms

## FUNCTIONAL DESCRIPTION

#### **INTRODUCTION**

The 33298 was conceived, specified, designed, and developed for automotive applications. It is an eight output low side power switch having 8-bit serial control. The 33298 incorporates SMARTMOS<sup>™</sup> technology having effective 1.5 µ CMOS logic, bipolar/MOS analog circuitry, and independent state of the art double diffused MOS (DMOS) power output transistors. Many benefits are realized as a direct result of using this mixed technology. A simplified block diagram delineates 33298 in Figure 1.

Where bipolar devices require considerable control current for their operation, structured MOS devices, since they are voltage controlled, require only transient gate charging current affording a significant decrease in power consumption. The CMOS capability of the SMARTMOS<sup>™</sup> process allows significant amounts of logic to be economically incorporated into the monolithic design. Additionally, the bipolar/MOS analog circuits embedded within the updrain power DMOS output transistors monitor and provide fast, independent protection control functions for each individual output. All outputs have internal 45 V at 0.5 A independent output voltage clamps to provide fast inductive turn-off and transient protection.

The 33298 uses high efficiency updrain power DMOS output transistors exhibiting very low room temperature drain-to-source ON resistance values ( $R_{DS(on)} \leq 1.0 \ \Omega$  at 13 V  $V_{PWR}$ ) and dense CMOS control logic. Operational bias currents of less than 2.0 mA (1.0 mA typical) with any combination of outputs ON are the result of using this mixed technology and would not be possible with bipolar structures. To accomplish a comparable functional feature set using a bipolar structure approach would result in a device requiring hundreds of milliamperes of internal bias and control current. This would represent a very large amount of power to be consumed by the device itself and not available for load use.

During operation, the 33298 functions as an eight output serial switch serving as a microcontroller (MCU) bus expander and buffer with fault management and fault reporting features.

In doing so, the device directly relieves the MCU of the fault management functions.

The 33298 directly relieves the MCU of the fault management functions. The 33298 directly interfaces to an MCU, operating at system clock serial frequencies in excess of 3.0 MHz. It uses a Synchronous Peripheral Interface (SPI) for control and diagnostic readout. Figure 11 illustrates the basic SPI configuration between an MCU and one 33298.

The circuit can also be used in a variety of other applications in the computer, telecommunications, and industrial fields. It is parametrically specified over an input *battery* /supply range of 9.0 to 16 V but is designed to operate over a considerably wider range of 5.5 to 26.5 V. The design incorporates the use of Logic Level MOSFETs as output devices. These MOSFETs are sufficiently turned ON with a gate voltage of less than 5.0 V thus eliminating the need for an internal charge pump. Each output is identically sized and *independent* in operation. The efficiency of each output transistor, at room temperature provides as little as 9.0 V supply (V<sub>PWR</sub>), the maximum R<sub>DS(on)</sub> of an output

All inputs are compatible with 5.0 V CMOS logic levels, incorporating negative or inverted logic. Whenever an input is programmed to a logic low state (<1.0 V) the corresponding low side switched output being controlled will be active low and turned ON. Conversely, whenever an input is programmed to a logic high state (>3.0 V), the output being controlled will be high and turned OFF.

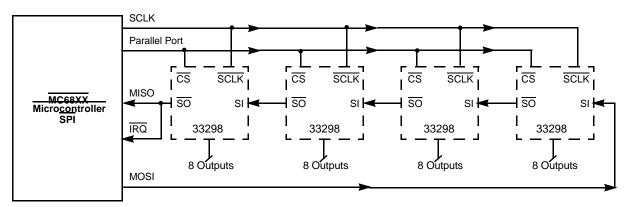

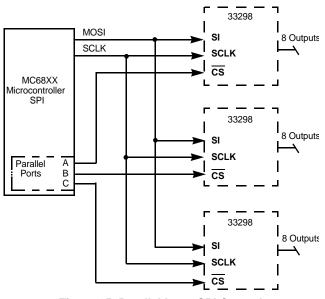

One main advantage of the 33298 is the serial port. When coupled to an MCU, it receives ON/OFF commands from the MCU and in return transmits the drain status of the device's output switches. Many devices can be *daisy-chained* together, forming a larger system, illustrated in Figure 12.

**Note** In this example, only one dedicated MCU parallel port (aside from the required SPI) is required for chip select to control 32 possible loads.

Multiple 33298 devices can also be controlled in a parallel input fashion using SPI, illustrated in Figure 13. This figure shows a possible 24 loads being controlled by only three dedicated parallel MCU ports used for chip select.

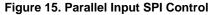

Figure 14 illustrates a basic method of controlling multiple 33298 devices using two MCUs. A system can have only one master MCU at any given instant of time and one or more slave MCUs. Master control of the system must pass from one MCU to the other in an orderly manner. The master MCU supplies the system clock signal (top MCU designated the master); the lower MCU being the slave. It is possible to have a system with more than one master; however, not at the same time. Only when the master is not communicating can a slave assume the *mastership* and communicate. MCU master control is switched through the use of the slave select  $(\overline{SS})$  pin of the MCUs. A master will become a slave when it detects a logic low state on its  $\overline{SS}$  pin.

These basic examples make the 33298 very attractive for applications where a large number of loads require efficient control. To this end, the popular Synchronous Serial Peripheral Interface (SPI) protocol is incorporated to communicate efficiently with the MCU.

## SPI SYSTEM ATTRIBUTES

The SPI system is flexible enough to communicate directly with numerous standard peripherals and MCUs available from Freescale Semiconductor and other semiconductor manufacturers. SPI reduces the number of pins necessary for input/output (I/O) on the 33298. It also offers an easy means of expanding the I/O function using few MCU pins. The SPI system of communication consists of the MCU transmitting, in return it receives one data-bit of information per system clock cycle.

Data-bits of information are simultaneously transmitted by one pin, Microcontroller Out Serial In (MOSI), and received by another pin, Microcontroller In Serial Out (MISO), of the MCU.

Some features of SPI are:

- · Full duplex, three-wire synchronous data transfer

- Each microcontroller can be a master or a slave

- Provides write collision flag protection

- Provides end of message interrupt flag

- Four I/Os associated with SPI (MOSI, MISO, SCLK, SS) Drawbacks to SPI are:

- An MCU is required for efficient operational control

- In contrast to parallel input control it Is slower at performing pulse width modulating (PWM) functions.

## FUNCTIONAL PIN DESCRIPTION

Figure 16. Multiple MCU SPI Control

## CHIP SELECT (CS)

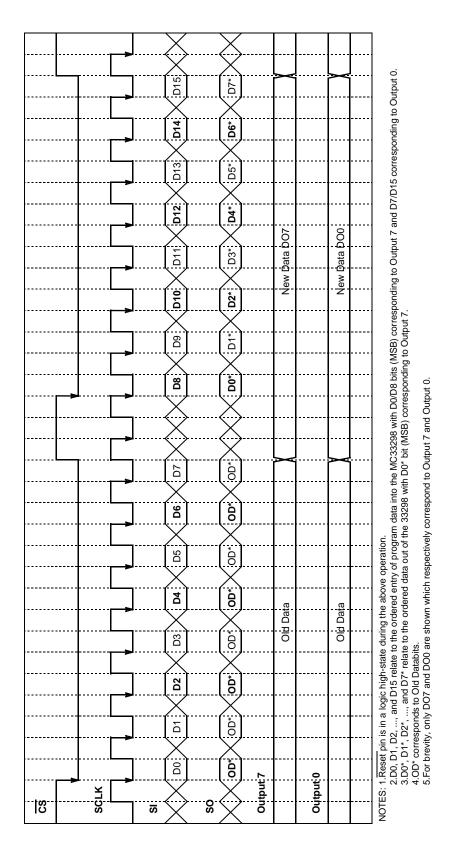

The 33298 receives its MCU communication through the CS pin. Whenever this pin is in a logic low state, data can be transferred from the MCU to the 33298 by way of the SI pin and from the 33298 to the MCU through the SO pin. Clockedin data from the MCU is transferred from the 33298 Shift register and latched into the power outputs on the rising edge of the CS signal. On the falling edge of the CS signal, drain status information is transferred from the power outputs then loaded into the Shift register of the device. The CS pin also controls the output driver of the serial output (SO) pin. Whenever the  $\overline{CS}$  pin goes to a logic low state, the SO pin output driver is enabled allowing information to be transferred from the 33298 to the MCU. To avoid data corruption or the generation of spurious data, it is essential the high-to-low transition of the CS signal occur only when SCLK is in a logic low state.

## SYSTEM CLOCK (SCLK)

The system clock (SCLK) pin clocks the internal shift registers of the 33298. The serial input (SI) pin accepts data into the Input Shift register on the falling edge of the SCLK signal while the serial output (SO) pin shifts data information out of the SO line driver on the rising edge of the SCLK signal. False clocking of the Shift register must be avoided to guarantee validity of data. It is essential the S<u>CLK</u> pin be in a logic low state whenever the chip select bar (CS) pin makes any transition. For this reason, it is recommended, though not absolutely necessary, the SCLK pin be kept in a low logic state as long as the device is not accessed ( $\overline{CS}$  in logic high state). When  $\overline{CS}$  is in a logic high state, signals at the SCLK and SI pins are ignored and SO is tri-stated (high impedance). See the Data Transfer Timing diagram in Figure 16.

## SERIAL INPUT (SI)

This pin is for the input of serial instruction (SI) data. SI is read on the falling edge of SCLK. A logic high state present on this pin when the SCLK signal rises will program a specific output OFF. In turn, the pin turns OFF the specific output on the rising edge of the CS signal. Conversely, a logic low state present on the SI pin will program the output ON, In turn, the pin turns ON the specific output on the rising edge of the  $\overline{CS}$ signal.

To program the eight outputs of the 33298 ON or OFF, an 8-bit serial stream of data is required to be synchronously entered into the SI pin starting with Output 7, followed by Output 6, Output 5, and so on, to Output 0. Referring to Figure 15, the DO bit is the most significant bit (MSB) corresponding to Output 7. For each rise of the SCLK signal, with CS held in a logic low state, a data-bit instruction (ON or OFF) is synchronously loaded into the Shift register per the data-bit SI state. The Shift register is full after eight bits of information have been entered. To preserve data integrity, care should be taken to not transition SI as SCLK transitions from a low-to-high logic state.

## **SERIAL OUTPUT (SO)**

The serial output (SO) pin is the *tri-stateable* output from the Shift register. The SO pin remains in a high impedance state until the CS pin goes to a logic low state. The SO data reports the drain status, either high or low relative to the previous command word. The SO pin changes state on the rising edge of SCLK and reads out on the falling edge of SCLK. When an output is OFF and not faulted, the corresponding SO data-bit is a high state. When an output is ON, and there is no fault, the corresponding data-bit on the SO pin will be a low logic state. The SI/SO shifting of data follows a first-in-first-out (FIFO) protocol with both input and output words transferring the MSB first. Referring to Figure 16, the DO bit is the MSB corresponding to Output 7 relative to the previous command word. The SO pin is not affected by the status of the Reset pin.

## RESET (RST)

The 33298 reset ( $\overline{\text{RST}}$ ) pin is active low. It is used to clear the SPI Shift register. In doing so, all output switches are set at OFF. The device situated in the same system with an MCU, the MCU retains the Reset pin of the device in a logic low state. Retention ensures all outputs to be OFF until both the V<sub>DD</sub> and V<sub>PWR</sub> pin voltages are adequate for predictable operation. Retention of the device Reset pin takes place only upon initial system power up. After the 33298 is reset, the MCU is ready to assert system control with all output switches initially OFF.

If the V<sub>PWR</sub> pin of the 33298 experiences a low voltage, following normal operation, the MCU should pull the Reset pin low to shutdown the outputs and clear the input data register. The Reset pin is active low and has an internal pull-down incorporated, insuring operational predictability should the external pull-down of the MCU open circuit. The internal pull-down is only 25  $\mu$ A, affording safe and easy interfacing to the MCU. The Reset pin of the 33298 should be pulled to a logic low state for a duration of at least 250 ns, ensuring reliable a reset.

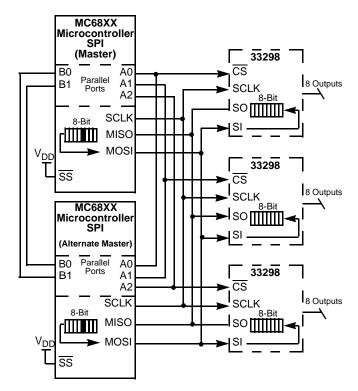

A simple power ON reset delay of the system can be programmed through the use of an RC network comprised of a shunt capacitor from the Reset pin to Ground and a resistor to  $V_{DD}$ , illustrated in Figure 15. Care should be exercised ensuring proper discharge of the capacitor. Careful attention eliminates adverse delay of the Reset and damage of the MCU if it pulls the Reset line low, thereby accomplishing initialization for turn ON delay. It may be easier to incorporate delay into the software program and use a parallel port pin of the MCU to control the 33298 Reset pin.

## SHORT FAULT PROTECT DISABLE (SFPD)

The Short Fault Protect Disable (SFPD) pin is used to prevent the outputs from latching-off due to an over current

condition. This feature provides control of incandescent lamp loads where in-rush currents exceed the device's analog current limits. Essentially the SFPD pin determines whether the 33298 output(s) will instantly shutdown upon sensing an output short or remain ON in a current limiting mode of operation until the output short is removed or thermal shutdown is reached. If the SFPD pin is tied to  $V_{DD} = 5.0$  V the 33298 output(s) will remain ON in a current limited mode of operation upon encountering a load short to supply or over current condition. When the SFPD pin is grounded, a short circuit will immediately shut down only the output affected. Other outputs not having a fault condition will operate normally. The short circuit operation is addressed in more detail later.

## POWER CONSUMPTION

The 33298 has extremely low power consumption in both the operating and standby modes. In the standby, or *Sleep* mode, with  $V_{DD} \le 2.0$  V, the current consumed by the  $V_{PWR}$  pin is less than 25 µA. In the operating mode, the current drawn by the  $V_{DD}$  pin is less than 4.0 mA (1.0 mA typical) while the current drawn at the  $V_{PWR}$  pin is 2.0 mA maximum (1.0 mA typical). During normal operation, turning outputs ON increases  $I_{PWR}$  by only 20 µA per output. Each output experiencing a *soft short* (over current conditions just under the current limit), adds 0.5 mA to the  $I_{PWR}$  current.

## PARALLELING OF OUTPUTS

Using MOSFETs as output switches permits connecting any combination of outputs together.  $R_{DS(ON)}$  of MOSFETs have an inherent positive temperature coefficient providing balanced current sharing between outputs without destructive operation (bipolar outputs could not be paralleled in this fashion as thermal run-away would likely occur). The device can even be operated with all outputs tied together. This mode of operation may be desirable in the event the application requires lower power dissipation, or the added capability of switching higher currents.

Performance of parallel operation results in a corresponding decrease in  $R_{DS(ON)}$  while the Output OFF Open Load Detect Currents and the Output Current Limits increase correspondingly (by a factor of eight if all outputs are paralleled). Less than 125 m $\Omega$  R<sub>DS(ON)</sub> at 25°C with current

limiting of eight to 24 A will result if all outputs are paralleled together. There will be no change in the over voltage detect or the OFF output threshold voltage range. The advantage of paralleling outputs within the same 33298 affords the existence of minimal  $R_{DS(ON)}$  and output clamp voltage variation between outputs.

Typically, the variation of  $R_{DS(ON)}$  between outputs of the same device is less than 0.5 percent. The variation in clamp

voltages, potentially affecting dynamic current sharing, is less than five percent. Paralleling outputs from two or more different devices is possible, but it is not recommended. There is no guarantee the  $R_{DS(ON)}$  and clamp voltage of the two devices will match. System level thermal design analysis and verification should be conducted whenever paralleling outputs; particularly where different devices are involved.

SO pin is enabled. Output Status information transferred to Output Shift Register

CS High-to-Low CS Low-to-High

s so

Data Transfer Timing (General)

Data from the Shift Register is transferred to the Output Power Switches.

Will change state on the rising edge of the SCLK pin signal. Will accept data on the falling edge of the SCLK pin signal.

## FAULT LOGIC OPERATION

#### INTRODUCTION

The MCU can perform a parity check of the fault logic operation by comparing the command 8-bit word to the status 8-bit word. Assume after system reset, the MCU first sends an 8-bit command word to the 33298. This word is called Command Word 1. Each output to be turned ON will have its corresponding data bit low. Refer to the data transfer timing illustration in Figure 16.

As Command Word 1 is being written into the Shift register of the 33298, a status word is being simultaneously written and received by the MCU. However, the word being received by the MCU is the status of the previous write word to the 33298, Status Word 0. If the command word of the MCU is written a second time (Command Word 2 = Command Word 1), the word received by the MCU, Status Word 2, is the status of Command Word 1. The timing diagram illustrated in Figure 16 depicts this operation. Status Word 2 is then compared with Command Word 1. The MCU will Exclusive OR Status Word 2 with Command Word 1 to determine if the two words are identical. If the two words are identical, faults do not exist. The timing between the two write words must be greater than 100 µs to receive proper drain status. The system data bus integrity may be tested by writing two like words to the 33298 within a few microseconds of each other.

#### **INITIAL SYSTEM SETUP TIMING**

The MCU can monitor two kinds of faults:

- 1. Communication errors on the data bus

- 2. Actual faults of the output loads

After initial system start up or reset, the MCU will write one word to the 33298. If the word is repeated within approximately five microseconds of the first word, the word received by the MCU, at the end of the repeated word, serves as a confirmation of data bus integrity (1). At start up, the 33298 will take 25 to 100  $\mu$ s before a repeat of the first word should be repeated at least 100  $\mu$ s later to verify the status of the outputs.

The SO of the 33298 will indicate any one of four faults. The four possible faults are:

- 1. Over Temperature

- 2. Output OFF Open Fault

- 3. Short Fault (over current)

- 4. V<sub>PWR</sub> Over Voltage Fault.

All of these faults, with the exception of the Over Voltage Fault, are output specific. Over Temperature Detect, Output OFF Open Detect, and Output Short Detect are dedicated to each output separately such that the outputs are independent in operation. A  $V_{PWR}$  Over Voltage Detect is a *global* nature causing all outputs to be turned OFF.

#### **OVER TEMPERATURE FAULT**

Patent pending Over Temperature Detect and shutdown circuits are specifically incorporated for each individual output. The shutdown following an Over Temperature condition is independent of the system clock and other logic signal. Each independent output shuts down at 155°C to 185°C. When an output shuts down due to an Over Temperature Fault, no other outputs are affected. The MCU recognizes the fault since the output was commanded to be ON and the status word indicates it is OFF. A maximum hysteresis of 20°C ensures an adequate time delay between output turn OFF and recovery. This avoids a very rapid turn ON and turn OFF of the device around the Over Temperature threshold. When the temperature falls below the recovery level for the Over Temperature Fault, the device will turn on only if the Command Word during the next write cycle indicates the output should be turned ON.

## **OVER VOLTAGE FAULT**

An Over Voltage condition on the V<sub>PWR</sub> pin causes the 33298 to shut down all outputs until the over voltage condition is removed and the device is re-programmed by the SPI. The over voltage threshold on the V<sub>PWR</sub> pin is specified as 28 V to 36 V with 1.0 V typical hysteresis. Following the over voltage condition, the next write cycle sends the SO pin the hexadecimal word \$FF (all ones) indicating all outputs are turned *off.* In this way, potentially dangerous timing problems are avoided and the MCU reset routine ensures an orderly startup of the loads. The 33298 does not detect an over voltage on the V<sub>DD</sub> pin. Other external circuitry, such as a universal voltage monitor, is necessary to accomplish this function.

## OUTPUT OFF OPEN LOAD FAULT

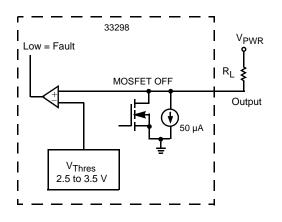

An Output OFF Open Load Fault is the detection and reporting of an *open* load when the corresponding output is disabled (input in a logic high state). To understand the operation of the Open Load Fault detect circuit; see Figure 17. The Output OFF Open Load Fault is detected by comparing the drain voltage of the specific MOSFET output to an internally generated reference. Each output has one dedicated comparator for this purpose.

#### Figure 19. Output OFF Open Load Fault

An Output OFF Open Load Fault is indicates when the output voltage is less than the Output Threshold Voltage (V<sub>Thres</sub>) of 0.6 to 0.8 x V<sub>DD</sub>. Since the 33298 outputs function as switches, during normal operation, each MOSFET output should either be completely turned ON or OFF. By design, the threshold voltage was selected to be between the ON and OFF voltage of the MOSFET. During normal operation, the ON state  $V_{DS}$  voltage of the MOSFET is less than the threshold voltage and the OFF state  $V_{DS}$  voltage is greater than the threshold voltage. This design approach provides using the same threshold comparator for Output Open Load Detect in the OFF state and Short Circuit Detect in the ON state. See Figure 18 for an understanding of the Short Circuit Detect circuit. With  $V_{DD}$  = 5.0 V, an OFF state output voltage of less than 3.0 V will be detected as an Output OFF Open Load Fault while voltages greater than 4.0 V will not be detected as a fault.

The 33298 has an internal pull-down current source of 50  $\mu$ A, illustrated in Figure 17 between the MOSFET drain and ground. This current source prevents the output from floating up to V<sub>PWR</sub> if there is an open load or internal wire bond failure. The internal comparator compares the drain voltage with a reference voltage, V<sub>Thres</sub> (0.6 to 0.8 x V<sub>DD</sub>). If the output voltage is less than this reference voltage, the 33298 will declare the condition to be an open load fault.

During steady-state operation, the minimum load resistance ( $R_L$ ) required to prevent false fault reporting during normal operation can be located using the following equation:

Therefore, the load resistance necessary to prevent false open load fault reporting is (using Ohm's Law) equal to 92  $k\Omega$  or less.

During output switching, especially with capacitive loads, a false output OFF Open Load Fault may be triggered. To prevent this false fault from being reported an internal fault filter in the range of 25 to 100  $\mu$ s is incorporated. The duration in which a false fault may be reported is a function of the load impedance (R<sub>L</sub>,C<sub>L</sub>,L<sub>L</sub>), R<sub>DS(on)</sub>, and C<sub>OUT</sub> of the MOSFET as well as the supply voltage (V<sub>PWR</sub>). The rising edge of CS triggers a built-in fault delay timer which must time-out (25 or 100  $\mu$ s) before the fault comparator is enabled to detect at

faulted threshold. The circuit automatically returns to normal operation once the condition causing the Open Load Fault is removed.

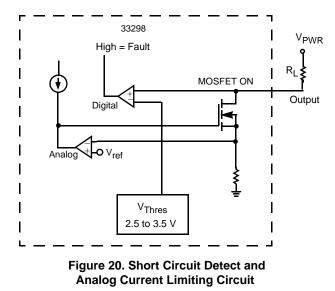

#### SHORTED LOAD FAULT

A short load, or over current fault can be caused by any output being shorted directly to supply, or an output experiencing a current greater than the current limit.

There are three safety circuits progressively in operation during load short conditions providing system protection. They are:

- The output current of the device is monitored in an analog fashion using a SENSEFET<sup>™</sup> approach and current limited.

- 2. The output current of the device is sensed by monitoring the MOSFET drain voltage.

- The output thermal limit of the device is sensed, and when attained, causes only the specific faulted output to be latched OFF, allowing all remaining outputs to operate normally.

Each of the three protection mechanisms are incorporated in their output providing robust independent output operation.

The analog current limit circuit is always active, monitoring the output drain current. An over current condition causes the gate control circuitry to reduce the gate-to-source voltage imposed on the output MOSFET, re-establishing the load current in compliance with current limit (1.0 to 3.0 A) range. Time required for the current limit circuitry to act is less than 20  $\mu$ s. Therefore, currents higher than 1.0 to 3.0 A will never be seen for more than 20  $\mu$ s (a typical duration is 10  $\mu$ s). If the current of an output attempts to exceed the predetermined limit of 1.0 to 3.0 A (2.0 A nominal), the V<sub>DS</sub> voltage will exceed the V<sub>Thres</sub> voltage and the over current comparator will be tripped, illustrated in Figure 18.

The status of SFPD determines whether the 33298 will shut down immediately, or continue to operate in an analog

33298

# FUNCTIONAL DESCRIPTION FAULT LOGIC OPERATION

current limited mode until either the short circuit (over current) condition is removed or thermal shutdown is reached.

Grounding the SFPD pin enables the short fault protection shutdown circuitry. Consider a load short (output short to supply) occurring on an output before, during, and after output turn ON. When the  $\overline{CS}$  signal rises to the high logic state, the corresponding output is turned ON, activating a delay timer. The duration of the delay timer is 70 to 250 µs. If the short circuit takes place before the output is turned ON, the delay experienced is the entire 70 µs to 250 µs followed by shutdown. If the short occurs during the delay time, the shutdown still occurs after the delay time has elapsed. However, if the short circuit occurs after the delay time, shutdown is immediate (within 20 µs after sensing). The purpose of the delay timer is to prevent *false* faults from being reported when switching capacitive loads.

If the SFPD pin is at 5.0 V, or  $V_{DD}$ , an output will not be disabled when an over current is detected. The specific output will, within 5.0 to 10  $\mu$ s of encountering the short circuit, go into an analog current limited mode. This feature is especially useful when switching incandescent lamp loads, where high in-rush currents experienced during startup last for 10 to 20 milliseconds.

Each output of the 33298 has its own over current shutdown circuitry. Over temperature, and the over voltage faults are not affected by the SFPD pin's state.

Both load current sensing and output voltage sensing are incorporated for Short Fault detection with actual detection occurring slightly *after* the onset of current limit. The current limit circuitry incorporates a SENSEFET<sup>™</sup> approach to measure the total drain current. This calls for the current through a small number of cells in the power MOSFET to be measured and the result multiplied by a constant, giving the total current. Wherein output shutdown circuitry measures the drain-to-source voltage, shutting down the output if its threshold (V<sub>Thres</sub>) is exceeded.

Short fault detection is accomplished by sensing the output voltage and comparing it to V<sub>Thres</sub>. The lowest V<sub>Thres</sub> requires a voltage of 2.5 V to be sensed. For an enabled output, with V<sub>DD</sub> =  $5.0 \pm 0.5$  V, an output voltage in excess of 3.5 V *will* be detected as a *short*, or over current condition, while voltages less than 2.5 V will *not* be detected as *shorts*.

## **OVER CURRENT RECOVERY**

If the SFPD pin is in a high logic state, the circuit returns to normal operation automatically after the short circuit is removed (unless thermal shutdown has occurred).

If the SFPD pin is grounded and over current shutdown occurs, removing the short circuit will result in the output remaining OFF until the next write cycle. If the short circuit is *not* removed, the output will turn ON for the delay time (70 to  $250 \ \mu$ s) and then turn OFF for every write cycle commanding a turn ON.

## SFPD PIN VOLTAGE SELECTION

Since the voltage condition of the SFPD pin controls the activation of the short fault protection (i.e., shutdown) mode equally for all eight outputs, the load having the longest duration of in-rush current determines what voltage (state) the SFPD pin should be. Usually if at least one load is, an incandescent lamp for example, the in-rush current on that input will be milliseconds in duration. Therefore, setting SFPD at 5.0 V will prevent shutdown of the output due to the in-rush current. The system relies only on the over temperature shutdown to protect the outputs and the loads. The 33298 was designed to switch GE194 incandescent lamps, or equivalents, with the SFPD pin in a grounded state. Considerably larger lamps can be switched with the SFPD pin held in a high logic state.

Sometimes both a delay period greater than 70 to 250 µs (current limiting of the output) followed by an immediate over current shutdown is necessary. This can be accomplished by programming the SFPD pin to 5.0 V for the extended delay period, allowing the outputs to remain ON in a current limited mode, then grounding it to accomplish the immediate shutdown after a period of time. Additional external circuitry is required to implement this type of function. An MCU parallel output port can be devoted to controlling the SFPD voltage during and after the delay period, is often a much better method. In either case, care should be taken to execute the SFPD start-up routine every time start-up or reset occurs.

## UNDER VOLTAGE SHUTDOWN

An under voltage V<sub>DD</sub> condition will result in the global shutdown of all outputs. The under voltage threshold is between 2.5 V and 3.5 V. When V<sub>DD</sub> goes below the threshold, all outputs are turned OFF, thereby resetting the Serial Output Data register to indicate the same.

An under voltage condition at the V<sub>PWR</sub> pin will *not* cause output shutdown and reset. When V<sub>PWR</sub> is between 5.5 V and 9.0 V, the outputs will operate per the command word. However, the status as reported by the SO pin may not be accurate below 9.0 V V<sub>PWR</sub>. Proper operation at V<sub>PWR</sub> voltages below 5.5 V are not be guaranteed.

## DECIPHERING FAULT TYPE

The 33298 SO pin can be used to determine what kind of system fault has occurred. With eight outputs having open load, over current, over temperature, and over voltage faults; a total of 25 different faults are possible. The SO status word received by the MCU will be compared with the word sent to the 33298 during the previous write cycle. For a specific output, if the SO bit compares with the corresponding SI bit of the previous word; the output is operating normal with no fault. Only when the SO bit and previous word SI bit differ is there a fault indicated. If the two words are *not* the same, the MCU should be programmed to determine which output or outputs are faulted.

If, for a specific output, the initial SI command bit were logic high, the output would be programmed to be OFF; if,

upon the next command word being entered, a logic low came back on SO, for that specific output's corresponding bit, an Output-OFF Open-Load fault would be indicated. The resulting SO bit, for that specific output, would be different from that entered during the previous word for that SI bit, indicating the fault. The eight output-off open-load faults are therefore most easily detected.

If for a specific output, the initial SI command bit were a logic low, calling for the output to be programmed *on*; upon the next word command being entered, the corresponding bit came back with a logic high on SO, an output over current fault would be indicated. An over current fault is always reported by the SO output and is independent of the logic state existing on the SFPD pin. When the SFPD pin is in a logic high state, an over current condition will be reported on the SO pin. However, limiting output current is in effect and the output is permitted to operate if the over current condition does not drive output into an over temperature fault. An over temperature fault will shutdown the specific output effected for the duration of the over temperature condition.

Over current and over temperature faults are often related. Turning the effected output switches OFF and waiting for some time to allow the output to cool down should make these types of faults go away. *Soft* over current faults can sometimes be determined over hard short faults and over temperature faults by observing the time required for the device to recover. However, in general over current and over temperature faults can not be differentiated in normal application usage.

An advantage of the synchronous serial output is multiple faults can be detected with only one (SO) pin being used for fault status reporting.

If  $V_{PWR}$  experiences an over voltage condition, all outputs will immediately be turned OFF and remain latched off. A new

command word is required to turn the outputs back on following an over voltage condition.

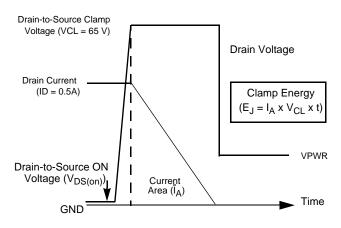

#### **OUTPUT VOLTAGE CLAMPING**

Each output of the 33298 incorporates an internal voltage clamp to provide fast turn-off and transient protection of the output. Each clamp independently limits the drain to source voltage to 53 V at drain currents of 0.5 A and keeps the output transistors from avalanching by causing the transient energy to be dissipated in the linear mode. See Figure 19. The total energy clamped ( $E_J$ ) can be calculated by multiplying the current area under the current curve ( $I_A$ ) times the clamp voltage ( $V_{CL}$ ) times the duration the clamp is active (t).

Characterization of the output clamps, using a single pulse non-repetitive method at 0.5 A, indicate the maximum energy to be 50 mJ at  $150^{\circ}$ C junction temperature per output.

Figure 21. Output Voltage Clamping

## THERMAL CHARACTERIZATION

#### THERMAL MODEL

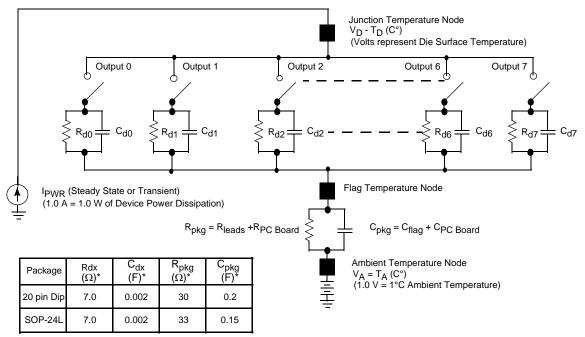

Logic functions take up a very small area of the die and generate negligible power. In contrast, the output transistors take up most of the die area and are the primary contributors of power generation. The thermal model illustrated in Figure 20 was developed for the 33298 mounted on a typical PC board. The model is accurate for both steady state and transient thermal conditions. The components  $R_{D0}$  through  $R_{D7}$  represent the steady state thermal resistance of the silicon die for transistor outputs 0 through 7, while  $C_{D0}$  through  $C_{D7}$  represent the corresponding thermal capacitance of the silicone die translator outputs and plastic. The device area and die thickness determine the values of these specific components.

The thermal impedance of the package from the internal mounting flag to the outside environment is represented by the terms  $R_{pkg}$  and  $C_{pkg}$ . The steady state thermal resistance of leads and the PC board make up the steady state package thermal resistance,  $R_{pkg}$ . The thermal capacitance of the package is made up of the combined capacitance of the flag

and the PC board. The mode compound was not modeled as a specific component but it is factored into the other overall component values.

The battery voltage in the thermal model represents the ambient temperature the device and PC board are subjected to. The  $I_{PWR}$  current source represents the total power dissipation and is calculated by totalling the power dissipation of each individual output transistor. This is easily accomplished by knowing  $R_{DS(on)}$  and load current of the individual outputs.

Very satisfactory steady state and transient results are experienced with this thermal model. Tests indicate the model accuracy to have less than 10 percent error. Output interaction with an adjacent output is believed to be the main contributor to the thermal inaccuracy. Tests indicate little or no detectable thermal affects caused by distant output transistors isolated by one or more other outputs. Tests were conducted with the device mounted on a typical PC board placed horizontally in a 33 cubic inch still air enclosure. The PC board was made of FR4 material measuring 2.5 by 2.5 inches, having double sided circuit traces of 1.0 ounce copper soldered to each device pin. The board temperature was measured with thermal couple soldered to the board surface one inch away from the center of the device. The ambient temperature of the enclosure was measured with a second thermal couple located over the center of one inch distance from device.

## THERMAL PERFORMANCE

Figure 20 illustrates the worst case thermal component parameters values for the 33298 in the 20-pin plastic power DIP and the SOP-24 wide body surface mount package. pins 5, 6, 15, and 16 of the power DIP package are connected directly to the lead frame flag. The parameter values indicated take into account adjacent output combinations. The characterization was conducted over power dissipation levels of 0.7 to 17 W. The junction-to-ambient temperature thermal resistance was found to be  $37^{\circ}$ C/W with a single output active ( $31^{\circ}$ C/W with all outputs dissipating equal power) and in conjunction with this, the thermal resistance from junction to PC board (R<sub>junction-board</sub>) was found to be  $27^{\circ}$ C/W (board temperature, measure one inch from device center). Additionally, the thermal resistance from junction-toheatsink lead was found to approximate  $10^{\circ}$ C/W. Devoting additional PC board metal around the heatsinking pins improved  $R_{pka}$  from 30° to 28° C/W.

The SOP-24 package has pins 5, 6, 7, 8, 17, 18, 19, and 20 of the package connected directly to the lead frame flag. Characterization was conducted in the same manner as with the DIP package. The junction-to-ambient temperature resistance was found to be 40°C/W with a single output active (34°C/W with all outputs dissipating equal power0 and the thermal resistance from junction-to-PC board ( $R_{junction-board}$ ) to be 30°C/W (board temperature, measure one inch from device center). The junction-to-heatsink lead resistance was found again to approximate 10°C/W. Devoting additional PC board metal around the heatsinking pins for this package improved the  $R_{okg}$  from 33° to 31°C/W.

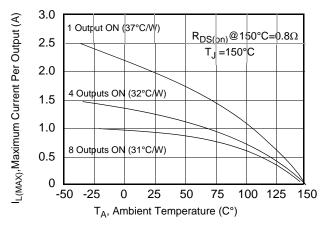

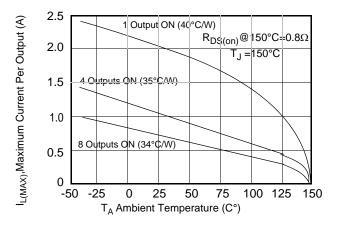

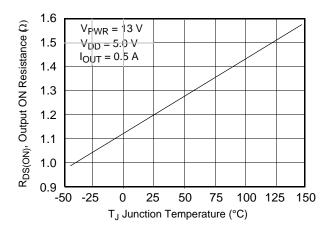

The total power dissipation available is dependent on the number of outputs enabled at any one time. At 25°C the  $R_{DS(on)}$  in 450 m $\Omega$  with a coefficient of 6500 ppm/°C. For the junction temperature to remain below 150°C, the maximum available power dissipation must decrease as the ambient temperature increases. Figures 21 and 22 depict the per output limit of current at ambient temperatures necessary when one, four, or eight outputs are enable ON. Figure 23 illustrates how the  $R_{DS(on)}$  output value is affected by junction temperature.

\*  $\Omega$  = °C/W, F = W s/°C, I<sub>PWR</sub> = W, and V<sub>A</sub> = °C

Figure 22. Thermal Model (Electrical Equivalent)

Figure 23. Maximum DIP Package Steady State Output Current vs. Ambient Temperature

Figure 24. Maximum SOP Package Steady State Output Current vs. Ambient Temperature

Figure 25. Maximum Output ON Resistance vs. Junction Temperature

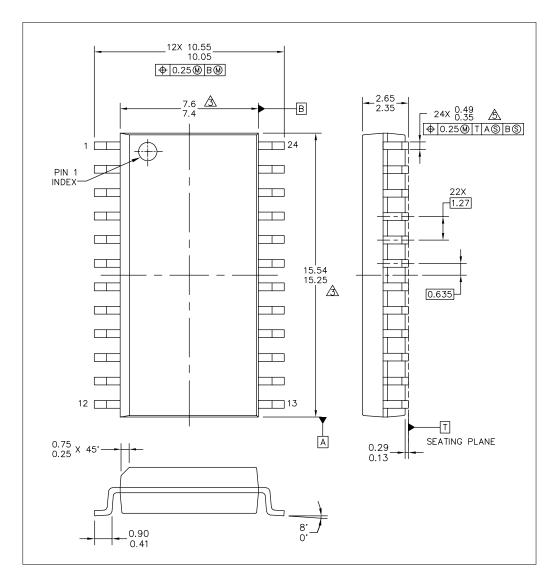

## PACKAGE DIMENSIONS

## PACKAGE DIMENSIONS

For the most current package revision, visit <u>www.freescale.com</u> and perform a keyword search using the "98A" listed below.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA    | LOUTLINE      | PRINT VERSION NO | T TO SCALE  |

|---------------------------------------------------------|--------------|---------------|------------------|-------------|

| TITLE: 24LD SOIC W/B, 1.2                               | 27 PITCH     | DOCUMENT NO   | ): 98ASB42344B   | REV: F      |