## Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

## **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

## THIS SPEC IS OBSOLETE

Spec No: 002-08376

Spec Title: MB39A136 2CH PFM/PWM DC/DC CONVERTER

IC WITH SYNCHRONOUS RECTIFICATION

Replaced by: NONE

# 2ch PFM/PWM DC/DC Converter IC with Synchronous Rectification

MB39A136 is 2ch step-down DC/DC converter IC of the current mode N-ch/N-ch synchronous rectification method. It contains the enhanced protection features, and supports the symmetrical-phase method and the ceramic capacitor. MB39A136 realizes rapid response, high efficiency, and low ripple voltage, and its high-frequency operation enables the miniaturization of inductors and I/O capacitors.

#### **Features**

■ High efficiency

■ For frequency setting by external resistor : 100 kHz to 1 MHz

■ Error Amp threshold voltage : 0.7 V ± 1.0%

■ Minimum output voltage value : 0.7 V

■ Wide range of power-supply voltage : 4.5 V to 25 V

■ PFM/PWM auto switching mode and fixed PWM mode selectable

■ Supports Symmetrical-Phase method

■ With built-in over voltage protection function

■ With built-in under voltage protection function

■ With built-in over current protection function

■ With built-in over-temperature protection function

■ With built-in soft start/stop circuit without load dependence

■ With built-in synchronous rectification type output steps for N-ch MOS FET

■ Standby current : 0 [µA] Typ

■ Small package : TSSOP-24

## **Application**

- Digital TV

- Photocopiers

- Surveillance cameras

- Set-top boxes (STB)

- DVD players, DVD recorders

- Projectors

- IP phones

- Vending machine

- Consoles and other non-portable devices

## Contents

| Pin Assignment                           | 3  | 3 |

|------------------------------------------|----|---|

| Pin Description                          |    |   |

| Block Diagram                            |    |   |

| Absolute Maximum Ratings                 | 6  | ò |

| <b>Recommended Operating Conditions.</b> |    | 7 |

| Electrical Characteristics               | 8  | 3 |

| Typical Characteristics                  |    | 2 |

| Function Description                     |    |   |

| Current Mode                             |    |   |

| Protection Function Table                |    |   |

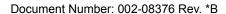

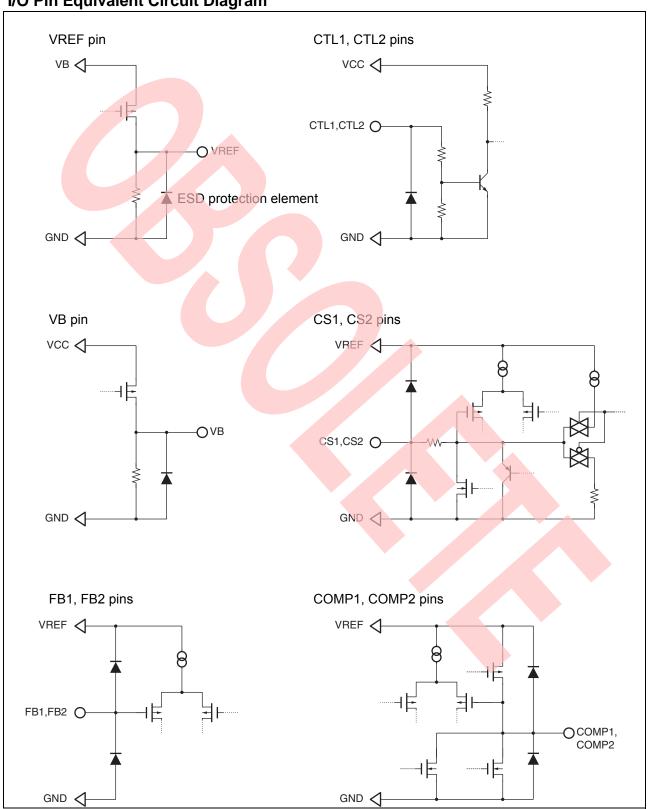

| I/O Pin Equivalent Circuit Diagram       | 19 | ) |

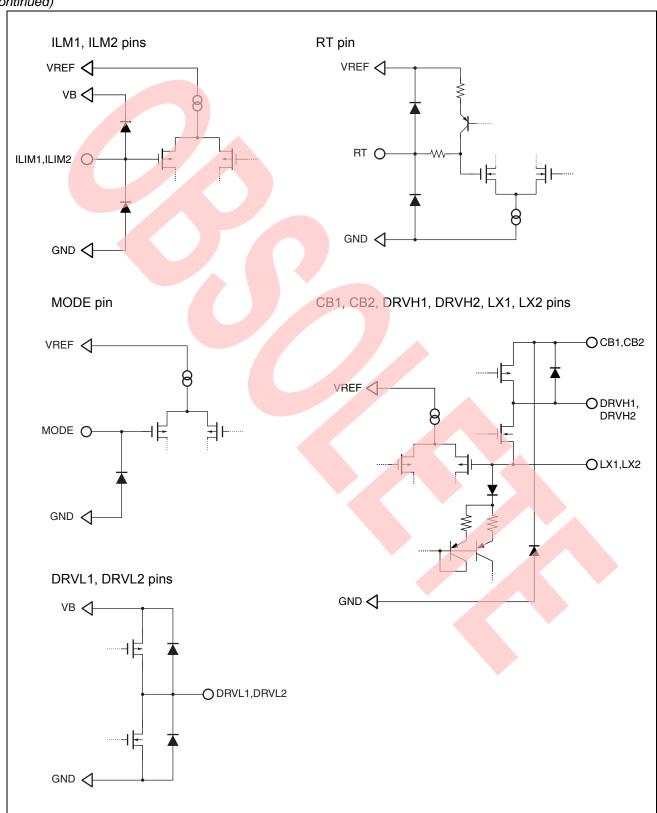

| Example Application Circuit              |    |   |

| Parts List                               |    |   |

| Application Note                    | 24         |

|-------------------------------------|------------|

| Reference Data                      | <b>4</b> 1 |

| Usage Precaution                    | 43         |

| Ordering Information                | 44         |

| EV Board Ordering Information       | 44         |

| RoHS Compliance Information Of      |            |

| Lead (Pb) Free Version              | 45         |

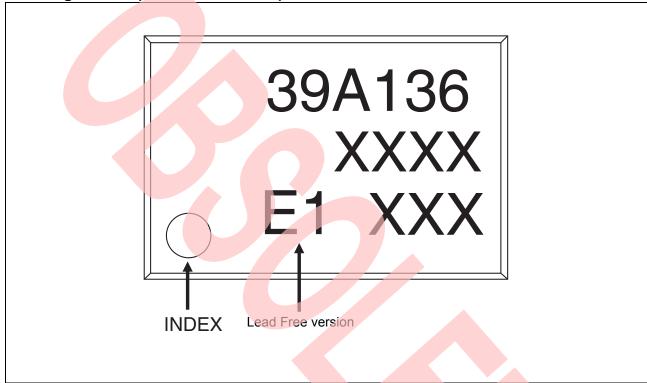

| Marking Format (Lead Free version)  | 45         |

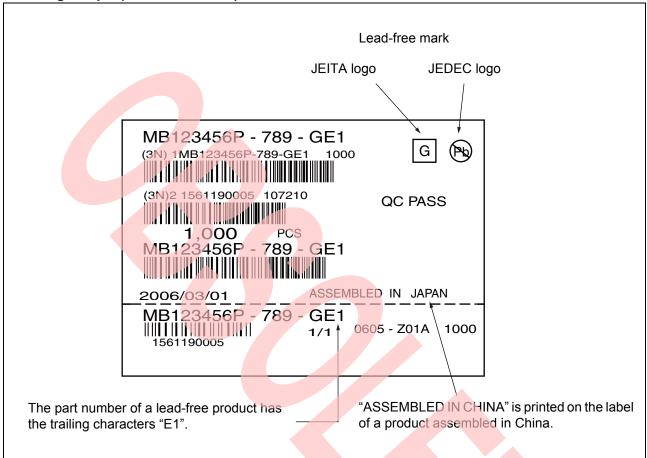

| Labeling Sample (Lead free version) | 46         |

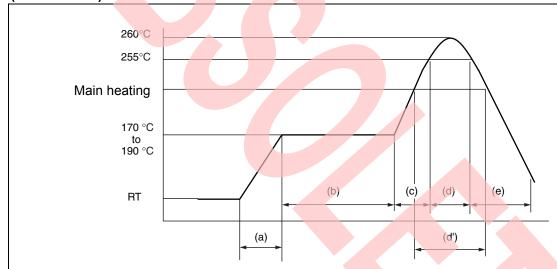

| MB39A136PFT Recommended Conditions  |            |

| Of Moisture Sensitivity Level       | 47         |

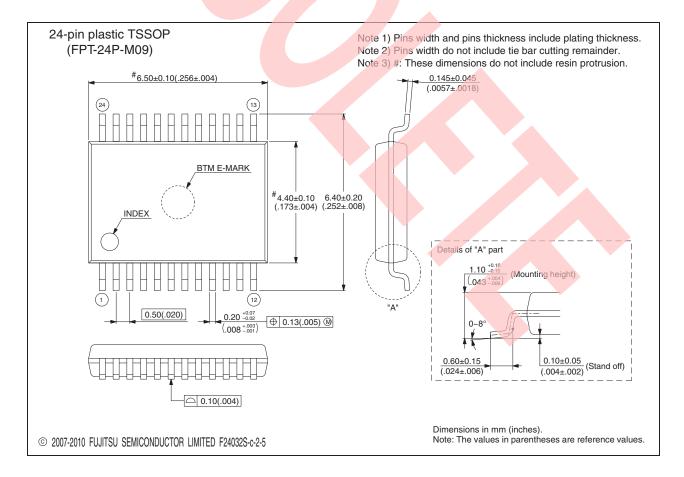

| Package Dimensions                  | 48         |

| Major Changes                       | 49         |

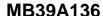

1. Pin Assignment

## 2. Pin Description

| Pin No. | Symbol | I/O | Description                                                                                                                                                     |

|---------|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CTL1   | I   | CH1 control pin.                                                                                                                                                |

| 2       | CS1    | I   | CH1 soft-start time setting capacitor connection pin.                                                                                                           |

| 3       | FB1    |     | CH1 Error amplifier inverted input pin.                                                                                                                         |

| 4       | COMP1  | 0   | CH1 error amplifier output pin.                                                                                                                                 |

| 5       | ILIM1  | I   | CH1 over current detection level setting voltage input pin.                                                                                                     |

| 6       | RT     | -   | Oscillation frequency setting resistor connection pin.                                                                                                          |

| 7       | VREF   | 0   | Reference voltage output pin.                                                                                                                                   |

| 8       | CTL2   | 1   | CH2 control pin.                                                                                                                                                |

| 9       | ILIM2  | I   | CH2 over current detection level setting voltage input pin.                                                                                                     |

| 10      | COMP2  | 0   | CH2 error amplifier output pin.                                                                                                                                 |

| 11      | FB2    |     | CH2 Error amplifier inverted input pin.                                                                                                                         |

| 12      | CS2    | 1   | CH2 soft-start time setting capacitor connection pin.                                                                                                           |

| 13      | MODE   | I   | PFM/PWM switch pin. (CH1 and CH2 commonness) It becomes fixed PWM operation with the VREF connection, and it becomes PFM/PWM operation with the GND connection. |

| 14      | CB2    | -   | CH2 connection pin for boot strap capacitor.                                                                                                                    |

| 15      | DRVH2  | 0   | CH2 output pin for external high-side FET gate drive.                                                                                                           |

| 16      | LX2    | _   | CH2 inductor and external high-side FET source connection pin.                                                                                                  |

| 17      | DRVL2  | 0   | CH2 output pin for external low-side FET gate drive.                                                                                                            |

| 18      | GND    | _   | Ground pin.                                                                                                                                                     |

| 19      | VB     | 0   | Bias voltage output pin.                                                                                                                                        |

| 20      | VCC    | _   | Power supply pin for reference voltage and control circuit.                                                                                                     |

| 21      | DRVL1  | 0   | CH1 output pin for external low-side FET gate drive.                                                                                                            |

| 22      | LX1    | _   | CH1 inductor and external high-side FET source connection pin.                                                                                                  |

| 23      | DRVH1  | 0   | CH1 output pin for external high-side FET gate drive.                                                                                                           |

| 24      | CB1    | _   | CH1 connection pin for boot strap capacitor.                                                                                                                    |

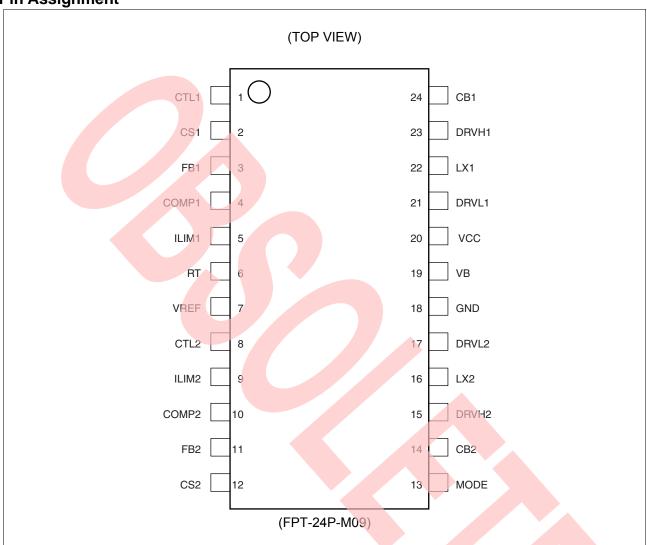

## 3. Block Diagram

## 4. Absolute Maximum Ratings

| Davamatav                 | Symbol            | Conditions                                 | Ra          | ting                    | Unit   |

|---------------------------|-------------------|--------------------------------------------|-------------|-------------------------|--------|

| Parameter                 | Symbol            | Conditions                                 | Min         | Max                     | - Unit |

| Power-supply voltage      | $V_{VCC}$         | VCC pin                                    | _           | 27                      | V      |

| CB pin input voltage      | V <sub>CB</sub>   | CB1, CB2 pins                              | _           | 32                      | V      |

| LX pin input voltage      | V <sub>LX</sub>   | LX1, LX2 pins                              | _           | 27                      | V      |

| Voltage between CB and LX | V <sub>CBLX</sub> | _                                          | _           | 7                       | V      |

| Control input voltage     | $V_1$             | CTL1, CTL2 pins                            | _           | 27                      | V      |

| Input voltage             | V <sub>FB</sub>   | FB1, FB2 pins                              | _           | V <sub>VREF</sub> + 0.3 | V      |

|                           | V <sub>ILIM</sub> | ILIM1, ILIM2 pins                          | _           | V <sub>VREF</sub> + 0.3 | V      |

|                           | V <sub>CSx</sub>  | CS1, CS2 pins                              | _           | V <sub>VREF</sub> + 0.3 | V      |

|                           | V <sub>MODE</sub> | MODE pin                                   | _           | V <sub>VB</sub> + 0.3   | V      |

| Output current            | I <sub>OUT</sub>  | DC DRVL1, DRVL2 pins,<br>DRVH1, DRVH2 pins | _           | 60                      | mA     |

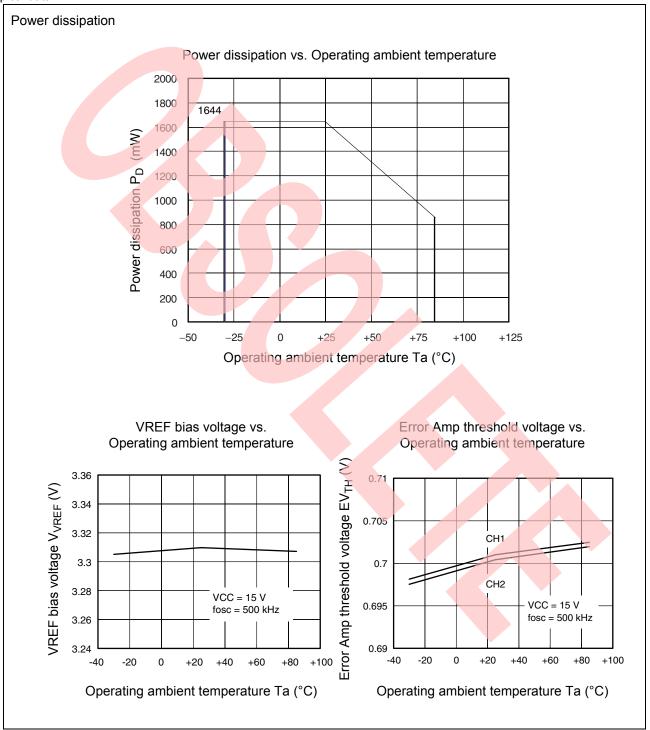

| Power dissipation         | P <sub>D</sub>    | Ta ≤ + 25°C                                | _           | 1644                    | mW     |

| Storage temperature       | T <sub>STG</sub>  | -                                          | <b>– 55</b> | + 150                   | °C     |

**WARNING:** Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

## 5. Recommended Operating Conditions

| Parameter                          | Symbol            | Conditions                                                                         |            | Value  |            | Unit    |

|------------------------------------|-------------------|------------------------------------------------------------------------------------|------------|--------|------------|---------|

| Parameter                          | Syllibol          | Conditions                                                                         | Min        | Тур    | Max        | - Offic |

| Power supply voltage               | V <sub>VCC</sub>  | _                                                                                  | 4.5        | _      | 25.0       | V       |

| CB pin input voltage               | V <sub>CB</sub>   |                                                                                    | _          | _      | 30         | V       |

| Reference voltage output current   | IVREF             | 7                                                                                  | - 100      | _      | _          | μΑ      |

| Bias output current                | I <sub>VB</sub>   | -                                                                                  | <b>–</b> 1 | _      | _          | mA      |

| CTL pin input voltage              | VI                | CTL1, CTL2 pins                                                                    | 0          | _      | 25         | V       |

|                                    | $V_{FB}$          | FB1, FB2 pins                                                                      | 0          | _      | $V_{VREF}$ | V       |

| Input voltage                      | V <sub>ILIM</sub> | ILIM1, ILIM2 pins                                                                  | 0.3        | _      | 1.94       | V       |

|                                    | V <sub>CS</sub>   | CS1, CS2 pins                                                                      | 0          | _      | $V_{VREF}$ | V       |

|                                    | V <sub>MODE</sub> | MODE pin                                                                           | 0          | _      | $V_{VREF}$ | V       |

| Peak output current                | l <sub>out</sub>  | DRVH1, DRVH2 pins<br>DRVL1, DRVL2 pins<br>Duty ≤ 5% (t = 1/f <sub>OSC</sub> ×Duty) | - 1200     | _      | + 1200     | mA      |

| Operation frequency range          | f <sub>OSC</sub>  | -                                                                                  | 100        | 500    | 1000       | kHz     |

| Timing resistor                    | R <sub>RT</sub>   | RT pin                                                                             | -          | 47     | _          | kΩ      |

| Soft start capacitor               | C <sub>CS</sub>   | CS1, CS2 pins                                                                      | 0.0075     | 0.0180 | _          | μF      |

| CB pin capacitor                   | C <sub>CB</sub>   | CB1, CB2 pins                                                                      | -          | 0.1    | 1.0        | μF      |

| Reference voltage output capacitor | C <sub>VREF</sub> | VREF pin                                                                           | -          | 0.1    | 1.0        | μF      |

| Bias voltage output capacitor      | C <sub>VB</sub>   | VB pin                                                                             | _          | 2.2    | 10         | μF      |

| Operating ambient temperature      | Та                | -                                                                                  | - 30       | + 25   | + 85       | °C      |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

> Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

## 6. Electrical Characteristics

(Ta = +25°C, VCC pin = 15 V, CTL pin = 5 V, VREF pin = 0 A, VB pin = 0A)

|                                      |                                                               |                    | Pin   | = +25 C, VCC piii = 15 V, V                     |        | Value  |       |      |  |

|--------------------------------------|---------------------------------------------------------------|--------------------|-------|-------------------------------------------------|--------|--------|-------|------|--|

| Pa                                   | arameter                                                      | Symbol             | No.   | Conditions                                      | Min    | Тур    | Max   | Unit |  |

|                                      | Output voltage                                                | V <sub>VREF</sub>  | 7     | _                                               | 3.24   | 3.30   | 3.36  | V    |  |

| Reference<br>Voltage Block           | Input stability                                               | VREF<br>LINE       | 7     | VCC pin = 4.5 V to 25 V                         | _      | 1      | 10    | mV   |  |

| [REF]                                | Load stability                                                | VREF<br>LOAD       | 7     | VREF pin = 0 A to<br>– 100 μA                   | _      | 1      | 10    | mV   |  |

|                                      | Short-circuit output current                                  | VREF<br>IOS        | 7     | VREF pin = 0 V                                  | - 14.5 | - 10.0 | - 7.5 | mA   |  |

|                                      | Output voltage                                                | V <sub>VB</sub>    | 19    | _                                               | 4.85   | 5.00   | 5.15  | V    |  |

| Bias Voltage<br>Block                | Input stability                                               | VB<br>LINE         | 19    | VCC pin = 6 V to 25 V                           | _      | 10     | 100   | mV   |  |

| [VB Reg.]                            | Load stability                                                | VB<br>LOAD         | 19    | VB pin = 0 A to − 1 mA                          | _      | 10     | 100   | mV   |  |

|                                      | Short-circuit output current                                  | VB<br>IOS          | 19    | VB pin = 0 V                                    | - 200  | - 140  | - 100 | mA   |  |

|                                      | Threshold voltage                                             | V <sub>TLH1</sub>  | 19    | VB pin                                          | 4.0    | 4.2    | 4.4   | V    |  |

| Under voltage                        |                                                               | V <sub>THL1</sub>  | 19    | VB pin                                          | 3.4    | 3.6    | 3.8   | V    |  |

| Lockout                              | Hysteresis width                                              | V <sub>H1</sub>    | 19    | VB pin − 0.6* −                                 |        |        |       | V    |  |

| Protection<br>Circuit Block          | Threshold                                                     | V <sub>TLH2</sub>  | 7     | VREF pin                                        | 2.7    | 2.9    | 3.1   | V    |  |

| [UVLO]                               | voltage                                                       | V <sub>THL2</sub>  | 7     | VREF pin                                        | 2.5    | 2.7    | 2.9   | V    |  |

|                                      | Hysteresis width                                              | V <sub>H2</sub>    | 7     | VREF pin                                        |        | 0.2*   | _     | V    |  |

|                                      | Charge current                                                | I <sub>CS</sub>    | 2, 12 | CTL1, CTL2 pins = 5 V,<br>CS1, CS2 pins = 0 V   | - 7.9  | -5.5   | - 4.2 | μΑ   |  |

| Soft-start /<br>Soft-stop<br>Block   | Soft-start end voltage                                        | V <sub>CS</sub>    | 2, 12 | CTL1, CTL2 pins = 5 V                           | 2.2    | 2.4    | 2.6   | V    |  |

| [Soft-Start,<br>Soft-Stop]           | Electrical discharge resistance at soft-stop                  | R <sub>DISCG</sub> | 2, 12 | CTL1, CTL2 pins = 0 V,<br>CS1, CS2 pins = 0.5 V | 49     | 70     | 91    | kΩ   |  |

|                                      | Soft-stop<br>end voltage                                      | V <sub>DISCG</sub> | 2, 12 | CTL1, CTL2 pins = 0 V                           | _      | 0.1*   | -     | V    |  |

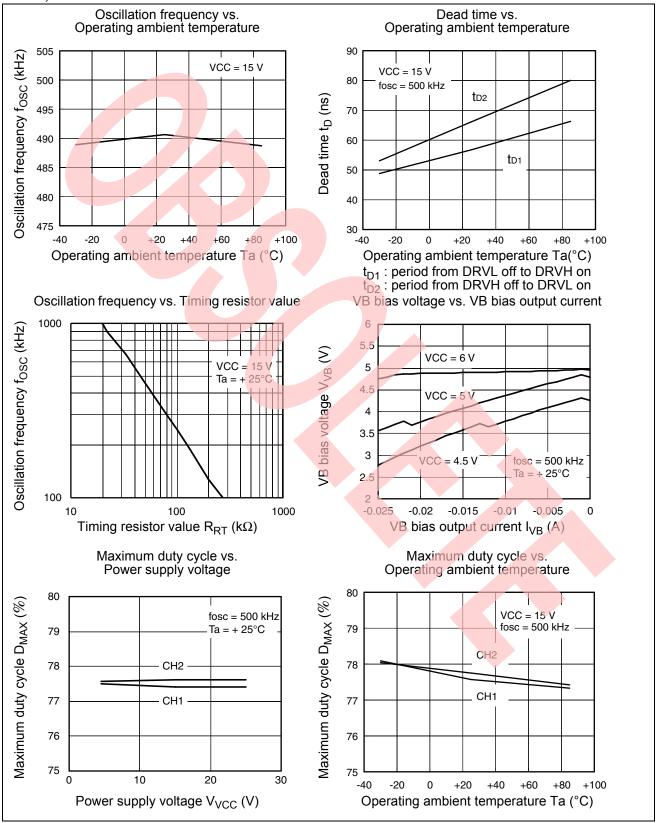

|                                      | Oscillation frequency                                         | f <sub>OSC</sub>   | 6     | RT pin = 47 k $\Omega$                          | 450    | 500    | 550   | kHz  |  |

| Clock<br>Generator<br>Block<br>[OSC] | Oscillation<br>frequency when<br>under voltage is<br>detected | f <sub>SHORT</sub> | 6     | RT pin = 47 k $\Omega$                          |        | 62.5   | _     | kHz  |  |

|                                      | Frequency<br>Temperature<br>variation                         | df/dT              | 6     | $Ta = -30^{\circ}C \text{ to } + 85^{\circ}C$   | _      | 3*     | _     | %    |  |

$(Ta = +25^{\circ}C, VCC pin = 15 V, CTL pin = 5 V, VREF pin = 0 A, VB pin = 0 A)$

| Dore                            | ameter                                      | Cumbal            | Pin    | Conditions                                         |            | Value                    |                   | Unit |

|---------------------------------|---------------------------------------------|-------------------|--------|----------------------------------------------------|------------|--------------------------|-------------------|------|

| Para                            | ameter                                      | Symbol            | No.    | Conditions                                         | Min        | Тур                      | Max               | Unit |

|                                 | Threshold                                   | EV <sub>TH</sub>  | 3, 11  | _                                                  | 0.693      | 0.700                    | 0.707             | V    |

|                                 | voltage                                     | EV <sub>THT</sub> | 3, 11  | $Ta = -30^{\circ}C \text{ to } +85^{\circ}C$       | 0.689*     | 0.700*                   | 0.711*            | V    |

|                                 | Input current                               | I <sub>FB</sub>   | 3, 11  | FB1, FB2 pins = 0 V                                | - 0.1      | 0                        | + 0.1             | μΑ   |

| Error Amp Block<br>[Error Amp1, | Output current                              | ISOURCE           | 4, 10  | FB1, FB2 pins = 0 V,<br>COMP1, COMP2 pins =<br>1 V | - 390      | - 300                    | - 210             | μΑ   |

| Error Amp2]                     |                                             | I <sub>SINK</sub> | 4, 10  | FB1, FB2 pins = VREF pin, COMP1, COMP2 pins = 1 V  | 8.4        | 12.0                     | 16.8              | mA   |

|                                 | Output clamp<br>voltage                     | V <sub>ILIM</sub> | 4, 10  | FB1, FB2 pins = 0 V,<br>ILIM1, ILIM2 pins = 1.5 V  | 1.35       | 1.50                     | 1.65              | V    |

|                                 | ILIM pin input current                      | I <sub>ILIM</sub> | 5, 9   | FB1, FB2 pins = 0 V,<br>ILIM1, ILIM2 pins = 1.5 V  | <b>–</b> 1 | 0                        | + 1               | μΑ   |

| Over-voltage<br>Protection      | Over-voltage detecting voltage              | V <sub>OVP</sub>  | 3, 11  | FB1, FB2 pins                                      | 0.776      | 0.805                    | 0.835             | V    |

| Circuit Block<br>[OVP Comp.]    | Over-voltage detection time                 | tove              | 3, 11  | -                                                  | 49         | 70                       | 91                | μs   |

| Under-voltage<br>Protection     | Under-voltage<br>detecting<br>voltage       | V <sub>UVP</sub>  | 3, 11  | FB1, FB2 pins                                      | 0.450      | 0.490                    | 0.531             | V    |

| Circuit Block<br>[UVP Comp.]    | Under-voltage detection time                | t <sub>UVP</sub>  | 3, 11  | -                                                  | _          | 512/<br>f <sub>OSC</sub> | _                 | s    |

| Over-temperature Protection     | Detection                                   | T <sub>OTPH</sub> | _      | Junction temperature                               | -          | + 160*                   | _                 | °C   |

| Circuit Block [OTP]             | temperature                                 | T <sub>OTPL</sub> | _      | Junction temperature                               |            | + 135*                   | _                 | °C   |

|                                 | Synchronous rectifi-<br>cation stop voltage | V <sub>THLX</sub> | 22, 16 | LX1, LX2 pins                                      | -          | 0*                       | _                 | mV   |

| PFM Control                     | PFM/PWM mode condition                      | V <sub>PFM</sub>  | 13     | MODE pin                                           | 0          |                          | 1.4               | V    |

| Circuit Block<br>(MODE)         | Fixed PWM mode condition                    | V <sub>PWM</sub>  | 13     | MODE pin                                           | 2.2        |                          | V <sub>VREF</sub> | V    |

|                                 | MODE pin input current                      | I <sub>MODE</sub> | 13     | MODE pin = 0 V                                     | -1         | 0                        | +1                | μΑ   |

$(Ta = +25^{\circ}C, VCC pin = 15 V, CTL pin = 5 V, VREF pin = 0 A, VB pin = 0 A)$

|                                     |                                      |                    |                   | a = +25°C, VCC pin = 15 V,                                                                                  | CTE piii |        | UA, VB pill = UA) |          |

|-------------------------------------|--------------------------------------|--------------------|-------------------|-------------------------------------------------------------------------------------------------------------|----------|--------|-------------------|----------|

| Para                                | meter                                | Symbol             | Pin No.           | Conditions                                                                                                  |          | Value  |                   | Unit     |

|                                     |                                      | J                  |                   |                                                                                                             | Min      | Тур    | Max               | <b>5</b> |

|                                     | High-side output on-resistance       | R <sub>ON_MH</sub> | 23, 15            | DRVH1, DRVH2 pins =<br>- 100 mA                                                                             | _        | 4      | 7                 | Ω        |

|                                     | on-resistance                        | R <sub>ON_ML</sub> | 23, 15            | DRVH1, DRVH2 pins = 100 mA                                                                                  | _        | 1.0    | 3.5               | Ω        |

|                                     | Low-side output                      | R <sub>ON_SH</sub> | 21, 17            | DRVL1, DRVL2 pins =<br>- 100 mA                                                                             | _        | 4      | 7                 | Ω        |

|                                     | on-resistance                        | R <sub>ON_SL</sub> | 21, 17            | DRVL1, DRVL2 pins = 100 mA                                                                                  | _        | 0.75   | 1.70              | Ω        |

| Output Block<br>[DRV]               | Output source current                | Source             | 23, 15,<br>21, 17 | LX1, LX2 pins = 0 V,<br>CB1, CB2 pins = 5 V<br>DRVH1, DRVH2 pins,<br>DRVL1, DRVL2 pins = 2.5 V<br>Duty ≤ 5% | _        | - 0.5* | _                 | A        |

|                                     | Output sink current                  | I <sub>SINK</sub>  | 23, 15            | LX1, LX2 pins = 0 V,<br>CB1, CB2 pins = 5 V<br>DRVH1, DRVH2 pins = 2.5 V<br>Duty ≤ 5%                       | _        | 0.9*   | _                 | A        |

|                                     |                                      |                    | 21, 17            | LX1, LX2 pins = 0 V,<br>CB1, CB2 pins = 5 V<br>DRVL1, DRVL2 pins = 2.5 V<br>Duty ≤ 5%                       | _        | 1.2*   | _                 | A        |

|                                     | Minimum on time                      | t <sub>ON</sub>    | 23, 15            | COMP1, COMP2 pins = 1 V                                                                                     | _        | 250*   | _                 | ns       |

|                                     | Maximum on-duty                      | D <sub>MAX</sub>   | 23, 15            | FB1, FB2 pins = 0 V                                                                                         | 75       | 80     | _                 | %        |

|                                     | Dead time                            | t <sub>D</sub>     | 23, 21,<br>15, 17 | LX1, LX2 pins = 0 V,<br>CB1, CB2 pins = 5 V                                                                 | -        | 60     | _                 | ns       |

|                                     | Maximum current sense voltage        | V <sub>RANGE</sub> | 22, 16            | VCC pin – LX1, LX2 pins                                                                                     |          | 220*   | _                 | mV       |

|                                     | Voltage conversion gain              | A <sub>LV</sub>    | 22, 16            | -                                                                                                           | 5.4      | 6.8    | 8.2               | V/V      |

| Level<br>Converter Block<br>[LVCNV] | Offset voltage at voltage conversion | V <sub>IO</sub>    | 22, 16            | -                                                                                                           | _        | 300    |                   | mV       |

|                                     | Slope<br>compensation<br>inclination | SLOPE              | 22, 16            | _                                                                                                           | -        | 2*     | -                 | V/V      |

|                                     | LX pin input current                 | I <sub>LX</sub>    | 22, 16            | LX1, LX2 pins = VCC pin                                                                                     | 320      | 420    | 600               | μΑ       |

## (Continued)

(Ta = +25°C, VCC pin = 15 V, CTL pin = 5 V, VREF pin = 0 A, VB pin = 0 A)

| Parameter                     |                      | Symbol            | Pin No.  | Conditions                                                            | Value |      |     | Unit |

|-------------------------------|----------------------|-------------------|----------|-----------------------------------------------------------------------|-------|------|-----|------|

|                               |                      | Symbol            | FIII NO. | Conditions                                                            | Min   | Тур  | Max | Onit |

|                               | ON condition         | V <sub>ON</sub>   | 1, 8     | CTL1, CTL2 pins                                                       | 2     | _    | 25  | V    |

|                               | OFF condition        | V <sub>OFF</sub>  | 1, 8     | CTL1, CTL2 pins                                                       | 0     | _    | 0.8 | V    |

| Control Block<br>[CTL1, CTL2] | Hysteresis width     | V <sub>H</sub>    | 1, 8     | CTL1, CTL2 pins                                                       | _     | 0.4* | _   | V    |

|                               | Input current        | I <sub>CTLH</sub> | 1, 8     | CTL1, CTL2 pins = 5 V                                                 | _     | 25   | 40  | μΑ   |

|                               |                      | I <sub>CTLL</sub> | 1, 8     | CTL1, CTL2 pins = 0 V                                                 | _     | 0    | 1   | μΑ   |

| Comoral                       | Standby current      | Iccs              | 20       | CTL1, CTL2 pins = 0 V                                                 | _     | 0    | 10  | μΑ   |

| General                       | Power-supply current | I <sub>cc</sub>   | 20       | LX1, LX2 pins = 0 V,<br>FB1, FB2 pins = 1.0 V,<br>MODE pin = VREF pin | _     | 3.3  | 4.7 | mA   |

<sup>\*:</sup> This value is not be specified. This should be used as a reference to support designing the circuits.

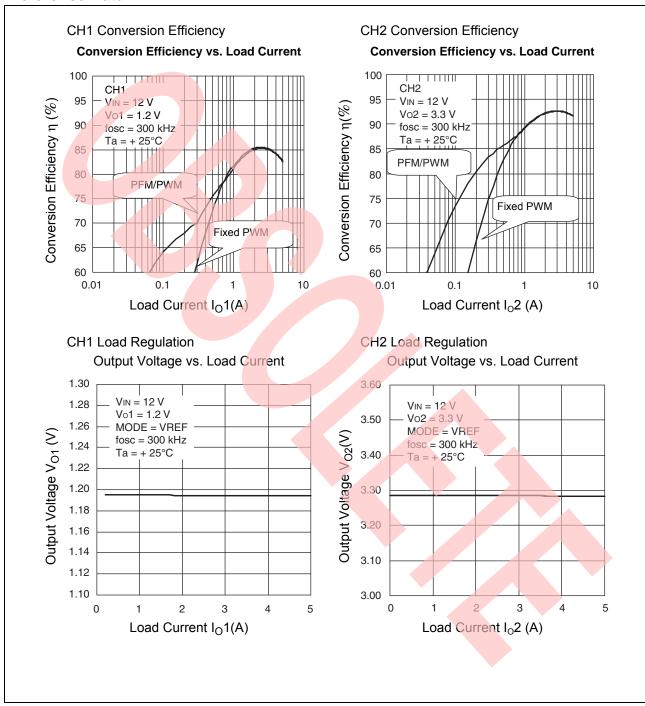

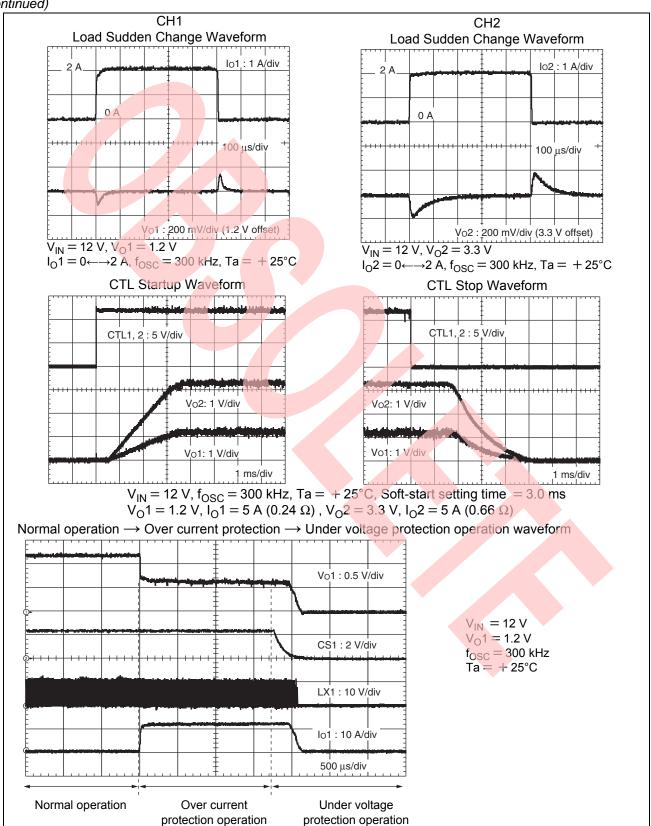

## 7. Typical Characteristics

#### ■ Typical data

## 8. Function Description

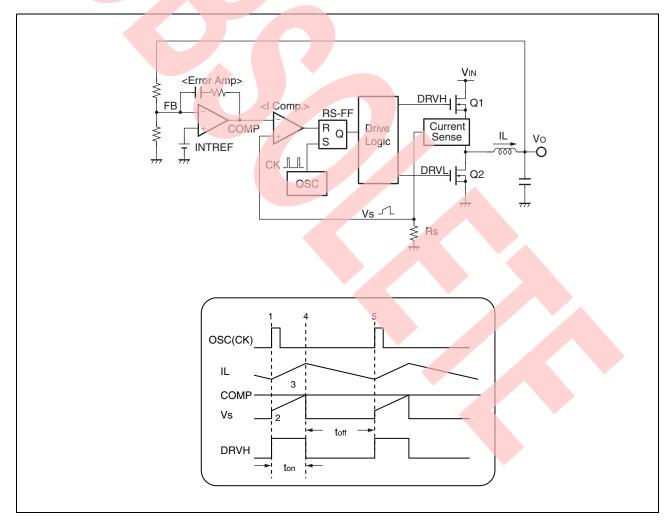

#### 8.1 Current Mode

It uses the current waveform from the switching (Q1) as a control waveform to control the output voltage, as described below:

- 1. The clock (CK) from the internal clock generator (OSC) sets RS-FF and turns on the high-side FET.

- 2. Turning on the high-side FET causes the inductor current (IL) rise. Generate Vs that converts this current into the voltage.

- 3. The current comparator (I Comp.) compares this Vs with the output (COMP) from the error amplifier (Error Amp) that is negative-feedback from the output voltage (Vo).

- 4. When I Comp. detects that Vs exceeds COMP, it resets RS-FF and turns off high-side FET.

- 5. The clock (CK) from the clock generator (OSC) turns on the high-side FET again.

Thus, switching is repeated.

Operate so that the FB electrical potential may become INTREF electrical potential, and stabilize the output voltage as a feedback control.

#### 8.1.1 Reference Voltage Block (REF)

The reference voltage circuit (REF) generates a temperature-compensated reference voltage (3.3 [V] Typ) using the voltage supplied from the VCC pin. The voltage is used as the reference voltage for the IC's internal circuit. The reference voltage can be used to supply a load current of up to 100  $\mu$ A to an external device through the VREF pin.

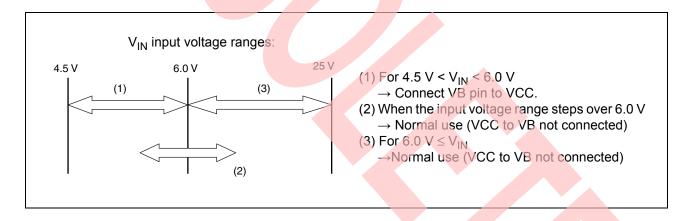

#### 8.1.2 Bias Voltage Block (VB Reg.)

Bias Voltage Block (VB Reg.) generates the reference voltage used for IC's internal circuit, using the voltage supplied from the VCC pin. The reference voltage is a temperature-compensated stable voltage (5 [V] Typ) to supply a current of up to 100 mA through the VB pin.

#### 8.1.3 Under Voltage Lockout Protection Circuit Block (UVLO)

The circuit protects against IC malfunction and system destruction/deterioration in a transitional state or a momentary drop when a bias voltage (VB) or an internal reference voltage (VREF) starts. It detects a voltage drop at the VB pin or the VREF pin and stops IC operation. When voltages at the VB pin and the VREF pin exceed the threshold voltage of the under voltage lockout protection circuit, the system is restored.

#### 8.1.4 Soft-start/Soft-stop Block (Soft-Start, Soft-Stop)

#### Soft-start

It protects a rush current or an output voltage  $(V_Ox)$  from overshooting at the output start. Since the lamp voltage generated by charging the capacitor connecting to the CSx pin is used for the reference voltage of the error amplifier (Error Amp), it can set the soft-start time independent of a load of the output  $(V_Ox)$ . When the IC starts with "H" level of the CTLx pin, the capacitor at the CSx pin (CS) starts to be charged at 5.5  $\mu$ A. The output voltage  $(V_Ox)$  during the soft-start period rises in proportion to the voltage at the CSx pin generated by charging the capacitor at the CSx pin.

During the soft-start with 0.8 V > voltage at CS1 and CS2 pins, operations are as follows:

- Fixed PWM operation only (fixed PWM even if MODE pin is set to "L")

- Over-voltage protection function and under-voltage protection function are invalid.

#### Soft-stop

It discharges electrical charges stored in a smoothing capacitor at output stop. Setting the CTLx pin to "L" level starts the soft-stop function independent of a load of output (Vox). Since the capacitor connecting to the CSx pin starts to discharge through the IC-built-in soft-stop discharging resistance (70 [k $\Omega$ ] Typ) when the CTLx pin sets at "L" level enters its lamp voltage into the error amplifier (Error Amp), the soft-stop time can be set independent of a load of output (Vox). When discharging causes the voltage at the CSx pin to drop below 100 mV (Typ), the IC shuts down and changes to the stand-by state. In addition, the soft-stop function operates after the under-voltage protection circuit block (UVP Comp.) is latched or after the over-temperature protection circuit block (OTP) detects over-temperature.

During the soft-stop with, 0.8 V > voltage at CS1 and CS2 pins, operations are as follows:

- Fixed PWM operation only (fixed PWM even if MODE pin is set to "L")

- Over-voltage protection function and under-voltage protection function are invalid.

#### 8.1.5 Clock Generator Block (OSC)

The clock generator has the built-in oscillation frequency setting capacitor and generates a clock that 180° phase shifted from each channel by connecting the oscillation frequency setting resistor to the RT pin (Symmetrical-Phase method).

#### 8.1.6 Error Amp Block (Error Amp1, Error Amp2)

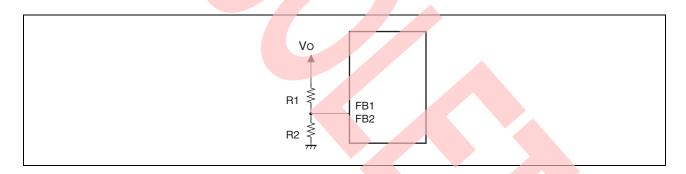

The error amplifiers (Error Amp1 and Error Amp2) detect the output voltage from the DC/DC converter and output to the current comparators (I Comp.1 and I Comp.2). The output voltage setting resistor externally connected to FB1 and FB2 pins allows an arbitrary output voltage to be set.

In addition, since an external resistor and an external capacitor serially connected between COMP1 and FB1 pins and between COMP2 and FB2 pins allow an arbitrary loop gain to be set, it is possible for the system to compensate a phase stably.

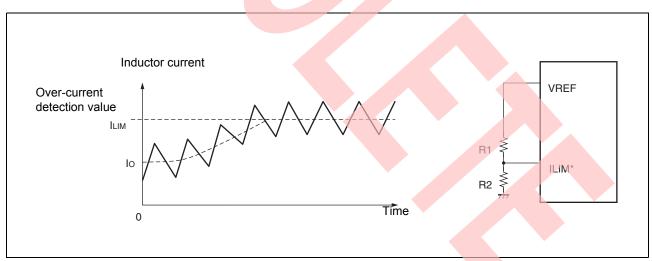

#### 8.1.7 Over Current Detection (Protection) Block (ILIM)

It is the current detection circuit to restrict an output current ( $I_{OX}$ ). The over current detection block (ILIM) compares an output waveform of the level converter of each channel (see "8.1.13" Level Converter Block (LVCNV)) with the ILIMx pin voltage in every cycle. As a load resistance ( $R_{OX}$ ) drops, a load current ( $I_{OX}$ ) increases. Therefore, the output waveform of the level converter exceeds the ILIM pin voltage of each channel. At this time, the output current can be restricted by turning off FET on the high-side and suppressing a peak value of the inductor current.

As a result, the output voltage  $(V_{OX})$  should drop.

Furthermore, if the output voltage drops and the electrical potential at the FBx pin drops below 0.3 V, the oscillation frequency (f<sub>OSC</sub>) drops to 1/8.

#### 8.1.8 Over-voltage Protection Circuit Block (OVP Comp.)

The circuit protects a device connecting to the output when the output voltage (VOX) rises.

It compares 1.15 times (Typ) of the internal reference voltage (INTREF) (0.7 V) that is non-inverting-entered into the error amplifier with the feedback voltage that is inverting-entered into the error amplifier and if it detects the state where the latter is higher than the former by 50  $\mu$ s (Typ). It stops the voltage output by setting the RS latch, setting the DRVHx pin to "L" level, setting the DRVLx pin to "H" level, turning off the high-side FETs, and turning on the low-side FETs.

The conditions below cancel the protection function:

- Setting CTL1 and CTL2 to "L".

- Setting the power supply voltage below the UVLO threshold voltage (V<sub>THL1</sub> and V<sub>THL2</sub>).

#### 8.1.9 Under-voltage Protection Circuit Block (UVP Comp.)

It protects a device connecting to the output by stopping the output when the output voltage (VOX) drops.

It compares 0.7 times (Typ) of the internal reference voltage (INTREF) (0.7 V) that is non-inverting-entered into the error amplifier with the feedback voltage that is inverting-entered into the error amplifier and if it detects the state where the latter is lower than the former by 512/fosc [s](Typ), it stops the voltage output for both channels by setting the RS latch.

The conditions below cancel the protection function:

- Setting CTL1 and CTL2 to "L".

- Setting the power supply voltage below the UVLO threshold voltage (V<sub>THL1</sub> and V<sub>THL2</sub>).

#### 8.1.10 Over temperature Protection Circuit Block (OTP)

The circuit protects an IC from heat-destruction. If the temperature at the joint part reaches +160°C, the circuit stops the voltage output for both channels by discharging the capacitor connecting to the CSx pin through the soft-stop discharging resistance (70 [k $\Omega$ ] Typ) in the IC.

In addition, if the temperature at the joint part drops to +135°C, the output restarts again through the soft-start function. Make sure to design the DC/DC power supply system so that the over temperature protection does not start frequently.

#### 8.1.11 PFM Control Circuit Block (MODE)

It sets the control mode of the IC and makes control at automatic PFM/PWM switching

| MODE pin connection | Control mode                | Features                                                                                                                               |

|---------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| "L" (GND)           | Automatic PFM/PWM switching | Highly-efficient at light load                                                                                                         |

| "H" (VREF)          | Fixed PWM                   | Stable oscillation frequency Stable switching ripple voltage Excellent in rapid load change characteristic at heavy load to light load |

#### Automatic PFM/PWM switching mode operation

It compares the LX1 pin and the LX2 pin voltages with GND electrical potential at Di Comp. In the comparison, the negative voltage at the LX pin causes the low-side FET to set on, positive voltage causes it to set off (Di Comp. method). As a result, the method restricts the back flow of the inductor current at a light load and makes the switching of the inductor current discontinuous (DCM). Such an operation allows the oscillation frequency to drop, resulting in high efficiency at a light load.

#### 8.1.12 Output Block (DRV)

The output circuit is configured in CMOS type for both of the high-side and the low-side, allowing the external N-ch MOS FET to drive.

#### 8.1.13 Level Converter Block (LVCNV)

The circuit detects and converts the current when the high-side FET turns on. It converts the voltage waveform between drain side (VCC pin voltage) and the source side (LX1 and LX2 pin voltage) on the high-side FET into the voltage waveform for GND reference.

Note: x : Each channel number

#### 8.1.14 Control Block (CTL1, CTL2)

The circuit controls on/off of the output from the IC.

Control function table

| CTL1 |   | CTL2 | DC/I | OC conve | erter | DC/DC converter (V <sub>O</sub> 2) | Remarks |

|------|---|------|------|----------|-------|------------------------------------|---------|

| L    | L |      | OFF  |          |       | OFF                                | Standby |

| Н    | L |      | ON   |          |       | OFF                                | _       |

| L    | Н |      | OFF  |          |       | ON                                 | _       |

| Н    | Н |      | ON   |          |       | ON                                 | _       |

## 9. Protection Function Table

The following table shows the state of each pin when each protection function operates.

| The fellowing table chows the state of each pin which each protection falled on operation. |                             |         |              |               |              |                                                                 |  |  |  |  |

|--------------------------------------------------------------------------------------------|-----------------------------|---------|--------------|---------------|--------------|-----------------------------------------------------------------|--|--|--|--|

| Protection Function                                                                        | Detection                   | Outpu   | ut of each p | in after dete | DC/DC output |                                                                 |  |  |  |  |

| Protection Function                                                                        | condition                   | VREF    | VB           | DRVHx         | DRVLx        | dropping operation                                              |  |  |  |  |

| Under Voltage Lock Out<br>Protection<br>(UVLO)                                             | VB < 3.6 V<br>VREF < 2.7 V  | < 2.7 V | < 3.6 V      | L             | L            | Self-discharge by load                                          |  |  |  |  |

| Under Voltage Protection (UVP)                                                             | FBx < 0.49 V                | 3.3 V   | 5 V          | L             | L            | Electrical discharge by soft-stop function                      |  |  |  |  |

| Over Voltage Protection (OVP)                                                              | FBx > 0.805 V               | 3.3 V   | 5 V          | L             | Н            | 0 V clamping                                                    |  |  |  |  |

| Over Current Protection (ILIM)                                                             | COMPx > ILIMx               | 3.3 V   | 5V           | switching     | switching    | The output voltage is dropping to keep constant output current. |  |  |  |  |

| Over Temperature<br>Protection<br>(OTP)                                                    | Tj > + 160°C                | 3.3 V   | 5 V          | L             | L            | Electrical discharge by soft-stop function                      |  |  |  |  |

| CONTROL<br>(CTL)                                                                           | CTLx : H→L<br>(CSx > 0.1 V) | 3.3 V   | 5 V          | L             | L            |                                                                 |  |  |  |  |

Note: x is the each channel number

## 10. I/O Pin Equivalent Circuit Diagram

## 11. Example Application Circuit

## 12. Parts List

| Component            | Item                                                        | Specification                                                                                                            | Vendor            | Package              | Parts Name                                      | Remark                    |

|----------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------|-------------------------------------------------|---------------------------|

| Q1                   | N-ch FET                                                    | $\begin{array}{l} \text{VDS} = 30 \text{ V}, \\ \text{ID} = 8 \text{ A}, \\ \text{Ron} = 21 \text{ m}\Omega \end{array}$ | RENESAS           | SO-8                 | μΡΑ2755                                         | Dual type<br>(2 elements) |

| Q2                   | N-ch FET                                                    | VDS = 30 V,<br>ID = 8 A,<br>Ron = 21 mΩ                                                                                  | RENESAS           | SO-8                 | μΡΑ2755                                         | Dual type<br>(2 elements) |

| D2                   | Diode                                                       | VF = 0.35 V<br>at IF = 0.2 A                                                                                             | ON Semi           | SOT-323              | BAT54AWT1                                       | Dual type                 |

| L1                   | Inductor                                                    | 1.5 μH<br>(6.2 mΩ, 8.9 A)                                                                                                | TDK               | _                    | VLF10040T-1R5N                                  |                           |

| L2                   | Inductor                                                    | 3.3 μH<br>(9.7 mΩ, 6.9 A)                                                                                                | TDK               | _                    | VLF10045T-3R3N                                  |                           |

| C1                   | Ceramic capacitor                                           | 22 μF (25 V)                                                                                                             | TDK               | 3225                 | C3225JC1E226M                                   |                           |

| C2-1<br>C2-2<br>C2-3 | Ceramic capacitor<br>Ceramic capacitor<br>Ceramic capacitor | 22 μF (10 V)<br>22 μF (10 V)<br>22 μF (10 V)                                                                             | TDK<br>TDK<br>TDK | 3216<br>3216<br>3216 | C3216JB1A226M<br>C3216JB1A226M<br>C3216JB1A226M | 3 capacitors in parallel  |

| C3-1<br>C3-2         | Ceramic capacitor<br>Ceramic capacitor                      | 22 μF (25 V)<br>22 μF (25 V)                                                                                             | TDK<br>TDK        | 3225<br>3225         | C3225JC1E226M<br>C3225JC1E226M                  | 2 capacitors in parallel  |

| C4-1<br>C4-2<br>C4-3 | Ceramic capacitor<br>Ceramic capacitor<br>Ceramic capacitor | 22 μF (10 V)<br>22 μF (10 V)<br>22 μF (10 V)                                                                             | TDK<br>TDK<br>TDK | 3216<br>3216<br>3216 | C3216JB1A226M<br>C3216JB1A226M<br>C3216JB1A226M | 3 capacitors in parallel  |

| C5                   | Ceramic capacitor                                           | 0.1 μF (50 V)                                                                                                            | TDK               | 1608                 | C1608JB1H104K                                   |                           |

| C6                   | Ceramic capacitor                                           | 0.1 μF (50 V)                                                                                                            | TDK               | 1608                 | C1608JB1H104K                                   |                           |

| C7                   | Ceramic capacitor                                           | 0.022 μF (50 V)                                                                                                          | TDK               | 1608                 | C1608JB1H223K                                   |                           |

| C8                   | Ceramic capacitor                                           | 0.022 μF (50 V)                                                                                                          | TDK               | 1608                 | C1608JB1H223K                                   |                           |

| C9                   | Ceramic capacitor                                           | 820 pF (50 V)                                                                                                            | TDK               | 1608                 | C1608CH1H821J                                   |                           |

| C11                  | Ceramic capacitor                                           | 1000 pF (50 V)                                                                                                           | TDK               | 1608                 | C1608CH1H102J                                   |                           |

| C13                  | Ceramic capacitor                                           | 0.01 μF (50 V)                                                                                                           | TDK               | 1608                 | C1608JB1H103K                                   |                           |

| C14                  | Ceramic capacitor                                           | 2.2 μF (16 V)                                                                                                            | TDK               | 1608                 | C1608JB1C225K                                   |                           |

| C15                  | Ceramic capacitor                                           | 0.1 μF (50 V)                                                                                                            | TDK               | 1608                 | C1608JB1H104K                                   |                           |

| R8-1<br>R8-2         | Resistor                                                    | 1.6 kΩ<br>9.1 kΩ                                                                                                         | SSM<br>SSM        | 1608<br>1608         | RR0816P162D<br>RR0816P912D                      | 2 capacitors in series    |

| R9                   | Resistor                                                    | 15 kΩ                                                                                                                    | SSM               | 1608                 | RR0816P153D                                     |                           |

| R11                  | Resistor                                                    | 56 kΩ                                                                                                                    | SSM               | 1608                 | RR0816P563D                                     |                           |

| R12                  | Resistor                                                    | 47 kΩ                                                                                                                    | SSM               | 1608                 | RR0816P473D                                     |                           |

| R14-1<br>R14-2       | Resistor                                                    | 1.8 kΩ<br>39 kΩ                                                                                                          | SSM<br>SSM        | 1608<br>1608         | RR0816P182D<br>RR0816P393D                      | 2 capacitors in series    |

| R15                  | Resistor                                                    | 11 kΩ                                                                                                                    | SSM               | 1608                 | RR0816P113D                                     |                           |

## (Continued)

| Component | Item     | Specification | Vendor | Package | Parts Name  | Remark |

|-----------|----------|---------------|--------|---------|-------------|--------|

| R17       | Resistor | 56 kΩ         | SSM    | 1608    | RR0816P563D |        |

| R18       | Resistor | 56 kΩ         | SSM    | 1608    | RR0816P563D |        |

| R21       | Resistor | 82 kΩ         | SSM    | 1608    | RR0816P823D |        |

| R23       | Resistor | 22 kΩ         | SSM    | 1608    | RR0816P223D |        |

| R25       | Resistor | 56 kΩ         | SSM    | 1608    | RR0816P563D |        |

RENESAS

: Renesas Electronics Corporation : ON Semiconductor : TDK Corporation : SUSUMU Co.,Ltd. ON Semi TDK SSM

### 13. Application Note

#### Setting method for PFM/PWM and fixed PWM modes

For the setting method for each mode, see "Function Description 8.1.11 PFM Control Circuit Block (MODE)".

#### Cautions at PFM/PWM mode

If a load current drops rapidly because of rapid load change and others, it tends to take a lot of time to restore overshooting of an output voltage.

As a result, the over-voltage protection may operate.

In this case, solution are possible by the addition of the load resistance of value to be able to restore the output voltage in the over-voltage detection time.

#### Setting method of output voltage

Set it by adjusting the output voltage setting zero-power resistance ratio.

$$V_O = \frac{R1 + R2}{R2} \times 0.7$$

V<sub>O</sub> : Output setting voltage [V] R1, R2 : Output setting resistor value [Ω]

Make sure that the setting does not exceed the maximum on-duty. Calculate the on-duty by the following formula:

$$D_{MAX\_Min} = \frac{V_O + R_{ON\_Sync} \times I_{OMAX}}{V_{IN} - R_{ON\_Main} \times I_{OMAX} + R_{ON\_Sync} \times I_{OMAX}}$$

$\begin{array}{ll} D_{MAX\_Min} & : \mbox{ Minimum value of the maximum on-duty cycle} \\ V_{IN} & : \mbox{ Power supply voltage of switching system [V]} \end{array}$

V<sub>O</sub> : Output setting voltage [V]

$\begin{array}{ll} R_{ON\_Main} & : \mbox{High-side FET ON resistance } [\Omega] \\ R_{ON\_Sync} & : \mbox{Low-side FET ON resistance } [\Omega] \end{array}$

I<sub>OMAX</sub> : Maximum load current [A]

#### Oscillation frequency setting method

Set it by adjusting the RT pin resistor value.

$$f_{OSC} = \frac{1.09}{R_{RT} \times 40 \times 10^{-12} + 300 \times 10^{-9}}$$

$R_{RT}$ : RT resistor value [ $\Omega$ ] fosc: Oscillation frequency [Hz]

The oscillation frequency must set for on-time  $(t_{ON})$  to become 300ns or more. Calculate the on-time by the following formula.

$$t_{ON} = \frac{V_O}{V_{IN} \times f_{OSC}}$$

t<sub>ON</sub> : On-time [s]

V<sub>IN</sub> : Power supply voltage of switching system [V]

V<sub>O</sub> : Output setting voltage [V] f<sub>OSC</sub> : Oscillation frequency [Hz]

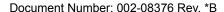

#### Setting method of soft-start time

Calculate the soft-start time by the following formula.

$$t_S = 1.4 \times 10^5 \times C_{CS}$$

: Soft-start time [s] (Time to becoming output 100%)

C<sub>CS</sub>: CS pin capacitor value [F]

Calculate delay time until the soft-start beginning by the following formula.

$$t_{d1} = 30 \times C_{VB} + 290 \times C_{VREE} + 1.455 \times 10^4 \times C_{CS}$$

t<sub>d1</sub> : Delay time including VB voltage and VREF voltage starts [s]

C<sub>CS</sub>: CS pin capacitor value [F] C<sub>VB</sub>: VB pin capacitor value [F]

C<sub>VREE</sub>: VREF pin capacitor value [F] (0.1 [μF] Typ)

Calculate delay time for starting while one channel has already started (UVLO released : VB, VREF output before) by the following formula.

$t_{d2} = 1.455 \times 10^4 \times C_{CS}$

t<sub>d2</sub> : Delay time for starting while one channel has already started [s]

C<sub>CS</sub>: CS pin capacitor value [F]

Calculate the discharge time at the soft-stop by the following formula.

$$\begin{split} t_{\text{dis}} &= 1.44 \times 10^5 \times C_{CS} \\ t_{\text{dis}} &: \text{Discharge time [s]} \\ C_{CS} &: \text{CS pin capacitor value [F]} \end{split}$$

In addition, calculate the delay time to the discharge starting by the following formula.

$t_{\text{d3}} = 7.87 \times 10^4 \times C_{\text{CS}}$

t<sub>d3</sub> : Delay time until discharge start [s]

C<sub>CS</sub> : CS pin capacitor value [F]

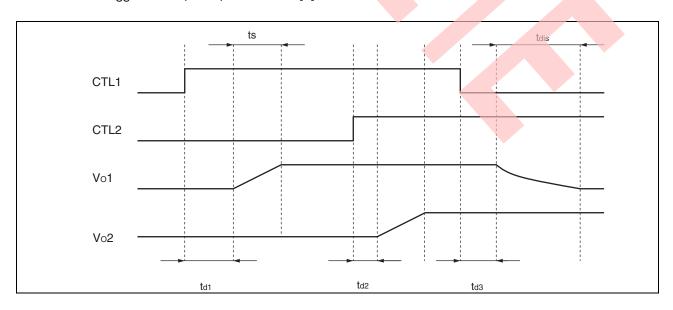

#### ■ Simultaneous operation of plural channels

Soft-start/soft-stop operation according to the same timing as two channels can be achieved by even connecting it as shown in the figure below at the power supply on/off.

#### <Connection example 1> When you adjust the soft-start time

Make the CS capacitor common. Connect CTL1 and CTL2.

Note: In this case, the soft-start time (ts), the discharge time (tdis), and the delay time (td1, td2, td3) decrease in the half value of compared with when CS capacitor is connected to each channel.

#### Setting method of over current detection value

It is possible to set over-current detection value (I<sub>LIM</sub>) by adjusting the over-current detection setting resistor value ratio. Calculate the over current detection setting resistor value by the following formula.

$$I_{LIM} = \frac{\frac{3.3 \times R2}{R1 \times R2} - 0.3}{6.8 \times R_{ON}} + \frac{V_{IN} - V_{O}}{L} \times (200 \times 10^{-9} - \frac{V_{O}}{2 \times f_{OSC} \times V_{IN}})$$

$$200 \times 10^{3} \ge R1 + R2 \ge 30 \times 10^{3}$$

I<sub>LIM</sub>: Over current detection value [A]

R1, R2 :  $I_{LIM}$  setting resistor value  $[\Omega]^*$

L : Inductor value [H]

V<sub>IN</sub>: Power supply voltage of switching system [V]

V<sub>O</sub> : Output setting voltage [V] f<sub>OSC</sub> : Oscillation frequency [Hz]

$R_{ON}$ : High-side FET ON resistance [ $\Omega$ ]

\* Since the over current detection value depends on the on-resistance of FET, the over current detection setting resistor value ratio should be adjusted in consideration of the temperature characteristics of the on-resistance. When the temperature at the FET joint part rises by + 100 °C, the on-resistance of FET increases to about 1.5 times.

\* If the over current detection function is not used, connect the ILIM pin (ILIM1 and ILIM2) to the VREF pin.

#### Selection of smoothing inductor

The inductor value selects the value that the ripple current peak-to-peak value becomes 50% or less of the maximum load current as a rough standard. Calculate the inductor value in this case by the following formula.

$$L \geq \frac{V_{IN} - V_{O}}{LOR \times I_{OMAX}} \times \frac{V_{O}}{V_{IN} \times f_{OSC}}$$

L : Inductor value [H]

IOMAX : Maximum load current [A]

LOR : Ripple current peak-to-peak value of Maximum load current ratio (=0.5)

V<sub>IN</sub> : Power supply voltage of switching system [V]

V<sub>O</sub>: Output setting voltage [V] fosc: Oscillation frequency [Hz]

An inductor ripple current value limited on the principle of operation is necessary for this device. However, when it uses the high-side FET of the low Ron resistance, the switching ripple voltage become small, and the inductor ripple current value may become insufficient. This should be solved by the oscillation frequency or reducing the inductor value.

Select the one of the inductor value that meets a requirement listed below.

$$L \leq \frac{V_{IN} - V_{O}}{\Delta V_{RON}} \times \frac{V_{O}}{V_{IN} \times f_{OSC}} \times R_{ON}$$

L : Inductor value [H]

V<sub>IN</sub>: Power supply voltage of switching system [V]

V<sub>O</sub> : Output setting voltage [V] f<sub>OSC</sub> : Oscillation frequency [Hz]

$\Delta V_{RON}$ : Ripple voltage [V] (20 mV or more is recommended)

$R_{ON}$ : High-side FET ON resistance [ $\Omega$ ]

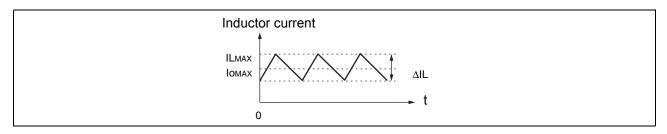

It is necessary to calculate the maximum current value that flows to the inductor to judge whether the electric current that flows to the inductor is a rated value or less. Calculate the maximum current value of the inductor by the following formula.

$$IL_{MAX} \ge Io_{MAX} + \frac{\Delta IL}{2}$$

,  $\Delta IL = \frac{V_{IN} - V_{O}}{L} \times \frac{V_{O}}{V_{IN} \times f_{OSC}}$

IL<sub>MAX</sub>: Maximum current value of inductor [A]

Io<sub>MAX</sub> : Maximum load current [A]

ΔIL : Ripple current peak-to-peak value of inductor [A]

L : Inductor value [H]

V<sub>IN</sub> : Power supply voltage of switching system [V]

V<sub>O</sub> : Output setting voltage [V] f<sub>OSC</sub> : Oscillation frequency [Hz]

#### Selection of SWFET

The switching ripple voltage generated between drain and sources on high-side FET is necessary for this device operation. Select the one of the SWFET of on-resistance that satisfies the following formula.

$$\mathsf{R}_{\mathsf{ON\_Main}} \geq \frac{\Delta \mathsf{V}_{\mathsf{RON\_Main}}}{\Delta \mathsf{IL}} \; \; , \; \mathsf{R}_{\mathsf{ON\_Main}} \leq \frac{\mathsf{V}_{\mathsf{RONMAX}}}{\mathsf{I}_{\mathsf{LIM}} + \; \frac{\Delta \mathsf{IL}}{2}}$$

$R_{ON\ Main}$ : High-side FET ON resistance [ $\Omega$ ]

ΔIL : Ripple current peak-to-peak value of inductor [A]

ΔV<sub>RON Main</sub>: High-side FET ripple voltage [V] (20mV or more is recommended)

: Over current detection value [A]

V<sub>RONMAX</sub>: Maximum current sense voltage [V] (240mV or less is recommended)

Select FET ratings with a margin enough for the input voltage and the load current. Ratings with the over-current detection setting value or more are recommended.

Calculate a necessary rated value of high-side FET and low-side FET by the following formula.

$$I_D > Io_{MAX} + \frac{\Delta IL}{2}$$

I<sub>D</sub> : Rated drain current [A]

Io<sub>MAX</sub> : Maximum load current [A]

ΔIL : Ripple current peak-to-peak value of inductor [A]

$$V_{DS} > V_{IN} \\$$

V<sub>DS</sub> : Rated voltage between drain and source [V]V<sub>IN</sub> : Power supply voltage of switching system [V]

$$V_{GS} > V_{B}$$

V<sub>GS</sub>: Rated voltage between gate and source [V]

V<sub>B</sub> : VB voltage [V]

Moreover, it is necessary to calculate the loss of SWFET to judge whether a permissible loss of SWFET is a rated value or less. Calculate the loss on high-side FET by the following formula.

$$P_{MainFET} = P_{RON\_Main} + P_{SW\_Main}$$

P<sub>MainFET</sub>: High-side FET loss [W]

P<sub>RON Main</sub>: High-side FET conduction loss [W]

P<sub>SW Main</sub> : High-side FET SW loss [W]

#### High-side FET conduction loss

$$\mathsf{P}_{\mathsf{RON\_Main}} = \mathsf{Io}_{\mathsf{MAX}}^{\phantom{\mathsf{MAX}}2} \times \phantom{\frac{\mathsf{V}_{\mathsf{O}}}{\mathsf{V}_{\mathsf{IN}}}} \times \mathsf{R}_{\mathsf{ON\_Main}}$$

P<sub>RON Main</sub>: High-side FET conduction loss [W]

I<sub>OMAX</sub>: Maximum load current [A]

V<sub>IN</sub> : Power supply voltage of switching system [V]

V<sub>O</sub> : Output voltage [V]

$R_{ON\ Main}$ : High-side FET ON resistance [ $\Omega$ ]

#### High-side FET SW loss

$$P_{SW\_Main} = \frac{V_{IN} \times f_{OSC} \times (I_{btm} \times t_r + I_{top} \times t_f)}{2}$$

P<sub>SW\_Main</sub>: High-side FET SW loss [W]

V<sub>IN</sub> : Power supply voltage of switching system [V]

f<sub>OSC</sub> : Oscillation frequency [Hz]

| Ibtm | : Ripple current bottom value of inductor [A] |

| Itop | : Ripple current top value of inductor [A] |

| tr | : Turn-on time on high-side FET[s] |

| tf | : Turn-off time on high-side FET[s] |

Calculate the  $I_{btm}$ , the  $I_{top}$ , the  $t_r$  and the  $t_f$  simply by the following formula.

$$I_{btm} = I_{OMAX} - \frac{\Delta IL}{2}$$

$$I_{top} = I_{OMAX} + \frac{\Delta IL}{2}$$

$$t_{r} = \frac{Q_{gd} \times 4}{5 - V_{gs} (on)} \qquad t_{f} = \frac{Q_{gd} \times 1}{V_{gs} (on)}$$

I<sub>OMAX</sub> : Maximum load current [A]

$\Delta$ IL : Ripple current peak-to-peak value of inductor [A]

$Q_{gd}$  : Quantity of charge between gate and drain on high-side FET [C]  $V_{gs}$  (on) : Voltage between gate and source in  $Q_{gd}$  on high-side FET [V]

Calculate the loss on low-side FET by the following formula.

$$P_{SyncFET} = P_{Ron\_Sync}^* = Io_{MAX}^2 \times (1 - \frac{V_O}{V_{IN}}) \times R_{on\_Sync}$$

P<sub>SyncFET</sub>: Low-side FET loss [W]

PRon Sync : Low-side FET conduction loss [W]

: Maximum load current [A]

V<sub>IN</sub> Power supply voltage of switching system [V]

V<sub>O</sub> : Output voltage [V]

$R_{\text{on Sync}}$ : Low-side FET on-resistance [ $\Omega$ ]

\*: The transition voltage of the voltage between drain and source on low-side FET is generally small, and the switching loss is omitted here for the small one as it is possible to disregard it.

The gate drive power of SWFET is supplied by LDO in IC, therefore all SWFET allowable maximum total charge (QgTotalMax) of 2ch is determined by the following formula.

QgTotalMax ≤

$$\frac{0.095}{f_{OSC}}$$

QgTotalMax : SWFET allowable maximum total charge [C]

f<sub>OSC</sub> : Oscillation frequency [Hz]

#### Selection of fly-back diode

When the conversion efficiency is valued, the improved property of the conversion efficiency is possible by the addition of the fly-back diode. Thought it is usually unnecessary. The effect is achieved in the condition where the oscillation frequency is high or output voltage is lower. Select schottky barrier diode (SBD) that the forward current is as small as possible. In this DC/DC control IC, the period for the electric current flows to fly back diode is limited to synchronous rectification period (60 ns \_ 2) because of using the synchronous rectification method. Therefore, select the one that the electric current of fly back diode doesn't exceed ratings of forward current surge peak (IFSM). Calculate the forward current surge peak ratings of fly back diode by the following formula.

$$I_{FSM} \ge I_{OMAX} + \frac{\Delta IL}{2}$$

I<sub>ESM</sub>: Forward current surge peak ratings of fly back diode [A]

Io<sub>MAX</sub> : Maximum load current [A]

ΔIL : Ripple current peak-to-peak value of inductor [A]

Calculate ratings of the fly-back diode by the following formula:

$$V_{R}$$

$Fly > V_{IN}$

$V_{R\_Fly}$ : Reverse voltage of fly-back diode direct current [V]

V<sub>IN</sub>: Power supply voltage of switching system [V]

#### Selection of output capacitor

This device supports a small ceramic capacitor of the ESR. The ceramic capacitor that is low ESR is an ideal to reduce the ripple voltage compared with other capacitor. Use the tantalum capacitor and the polymer capacitor of the low ESR when a mass capacitor is needed as the ceramic capacitor can not support. To the output voltage, the ripple voltage by the switching operation of DC/DC is generated. Discuss the lower bound of output capacitor value according to an allowable ripple voltage. Calculate the output ripple voltage from the following formula.

$$\Delta V_{O} = \left(\frac{1}{2\pi \times f_{OSC} \times C_{O}} + ESR\right) \times \Delta IL$$

$\Delta V_{O}$ : Switching ripple voltage [V]

ESR : Series resistance component of output capacitor [Ω]

ΔIL : Ripple current peak-to-peak value of inductor [A]

C<sub>O</sub>: Output capacitor value [F] f<sub>OSC</sub>: Oscillation frequency [Hz]

#### Notes:

• The ripple voltage can be reduced by raising the oscillation frequency and the inductor value besides capacitor.

• Capacitor has frequency characteristic, the temperature characteristic, and the electrode bias characteristic, etc. The effective capacitor value might become extremely small depending on the condition. Note the effective capacitor value in the condition.

Calculate ratings of the output capacitor by the following formula:

$$V_{CO} > V_{O}$$

V<sub>CO</sub>: Withstand voltage of the output capacitor [V]

V<sub>O</sub> : Output voltage [V]

Note: Select the capacitor rating with withstand voltage allowing a margin enough for the output voltage.

In addition, use the allowable ripple current with an enough margin, if it has a rating. Calculate an allowable ripple current of the output capacitor by the following formula:

Irms

$$\geq \frac{\Delta IL}{2\sqrt{3}}$$

Irms : Allowable ripple current (effective value) [A]

ΔIL : Ripple current peak-to-peak value of inductor [A]

#### Selection of input capacitor

Select the input capacitor whose ESR is as small as possible. The ceramic capacitor is an ideal. Use the tantalum capacitor and the polymer capacitor of the low ESR when a mass capacitor is needed as the ceramic capacitor can not support. To the power supply voltage, the ripple voltage by the switching operation of DC/DC is generated. Discuss the lower bound of input capacitor according to an allowable ripple voltage. Calculate the ripple voltage of the power supply from the following formula.

$$\Delta V_{IN} = \frac{I_{OMAX}}{C_{IN}} \times \frac{V_{O}}{V_{IN} \times f_{OSC}} + ESR \times (I_{OMAX} + \frac{\Delta IL}{2})$$

△V<sub>IN</sub> : Switching system power supply ripple voltage peak-to-peak value [V]

I<sub>OMAX</sub>: Maximum load current value [A]

C<sub>IN</sub>: Input capacitor value [F]

V<sub>IN</sub>: Power supply voltage of switching system [V]

V<sub>O</sub> : Output setting voltage [V] f<sub>OSC</sub> : Oscillation frequency [Hz]

ESR : Series resistance component of input capacitor  $[\Omega]$  : Ripple current peak-to-peak value of inductor [A]

#### Notes:

- The ripple voltage of the power supply can be reduced by raising the oscillation frequency besides capacitor.

- Capacitor has frequency characteristic, the temperature characteristic, and the electrode bias characteristic, etc. The effective capacitor value might become extremely small depending on the condition. Note the effective capacitor value in the condition.

Calculate ratings of the input capacitor by the following formula:

$$V_{CIN} > V_{IN}$$

V<sub>CIN</sub>: Withstand voltage of the input capacitor [V]V<sub>IN</sub>: Power supply voltage of switching system [V]

Note: Select the capacitor rating with withstand voltage with margin enough for the input voltage.

In addition, use the allowable ripple current with an enough margin, if it has a rating. Calculate an allowable ripple current by the following formula:

Irms

$$\geq I_{OMAX} \times \frac{\sqrt{V_O \times (V_{IN} - V_O)}}{V_{IN}}$$

Irms : Allowable ripple current (effective value) [A]

I<sub>OMAX</sub>: Maximum load current value [A]

V<sub>IN</sub>: Power supply voltage of switching system [V]

V<sub>O</sub>: Output voltage [V]

### Selection of boot strap diode

Select Schottky barrier diode (SBD), that forward current is as small as possible. The electric current that drives the gate of high-side FET flows to SBD of the bootstrap circuit. Calculate the mean current by the following formula. Select it so as not to exceed the electric current ratings.

$$I_D \ge Q_g \times f_{OSC}$$

: Forward current [A]

Q<sub>q</sub> : Total quantity of charge of gate on high-side FET [C]

f<sub>OSC</sub>: Oscillation frequency [Hz]

Calculate ratings of the boot strap diode by the following formula:

$$V_{R\_BOOT} > V_{IN}$$

V<sub>R BOOT</sub>: Reverse voltage of boot strap diode direct current [V]

V<sub>IN</sub> : Power supply voltage of switching system [V]

## Selection of boot strap capacitor

To drive the gate of high-side FET, the bootstrap capacitor must have enough stored charge. Therefore, a minimum value as a target is assumed the capacitor which can store electric charge 10 times that of the Qg on high-side FET. And select the boot strap capacitor.

$$C_{BOOT} \ge 10 \times \frac{Qg}{V_B}$$

C<sub>BOOT</sub>: Boot strap capacitor [F]

Qg : Amount of gate charge on high-side FET [C]

V<sub>B</sub> : VB voltage [V]

Calculate ratings of the boot strap capacitor by the following formula:

$$V_{CBOOT} > V_{B}$$

V<sub>CBOOT</sub>: Withstand voltage of the boot strap capacitor [V]

V<sub>B</sub> : VB voltage [V]

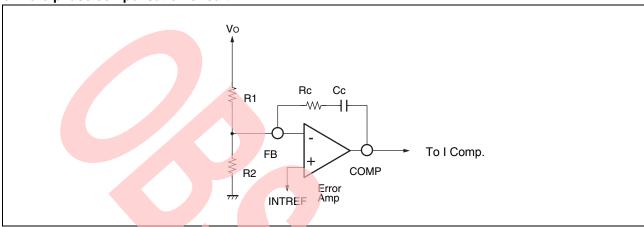

## Design of phase compensation circuit

Assume the phase compensation circuit of 1pole-1zero to be a standard in this device.

## 1pole-1zero phase compensation circuit

As for crossover frequency ( $f_{CO}$ ) that shows the band width of the control loop of DC/DC. The higher it is, the more excellent the rapid response becomes, however, the possibility of causing the oscillation due to phase margin shortage increases. Though this crossover frequency ( $f_{CO}$ ) can be arbitrarily set, make 1/10 of the oscillation frequencies (fosc) a standard, and set it to the upper limit. Moreover, set the phase margin at least to 30°C, and 45°C or more if possible as a reference.

Set the constants of Rc and Cc of the phase compensation circuit using the following formula as a target.

$$R_{C} = \frac{(V_{IN} - V_{O}) A_{LVCNV} \times R_{ON\_Main} \times f_{CO} \times 2\pi \times C_{O} \times V_{O}}{V_{IN} \times f_{OSC} \times L \times I_{OMAX}} \times R1$$

$$C_C = \frac{C_O \times V_O}{R_C \times I_{OMAX}}$$

$R_C$ : Phase compensation resistor value  $[\Omega]$  $C_C$ : Phase compensation capacitor value [F]

V<sub>IN</sub>: Power supply voltage of switching system [V]

$V_{O}$  : Output setting voltage [V]  $f_{OSC}$  : Oscillation frequency [Hz]

I<sub>OMAX</sub> : Maximum load current value [A]

L : Inductor value [H]

C<sub>O</sub>: Output capacitor value [F]

$\begin{array}{ll} R_{ON\_Main} & : \mbox{High-side FET ON resistance}[\Omega] \\ R1 & : \mbox{Output setting resistor value } [\Omega] \\ A_{LVCNV} & : \mbox{Level converter voltage gain } [V/V] \\ \end{array}$

On-duty  $\leq 50\%$  :  $A_{LVCNV} = 6.8$ On-duty > 50% :  $A_{LVCNV} = 13.6$

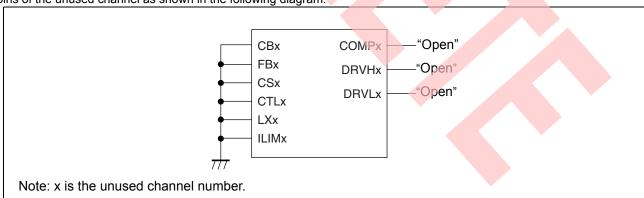

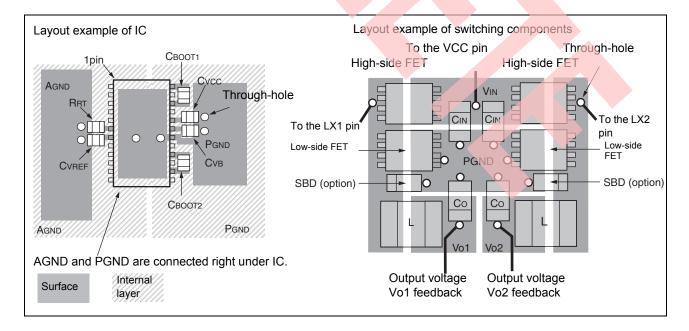

f<sub>CO</sub>: Cross-over frequency (arbitrary setting) [Hz]