# THIS SPEC IS OBSOLETE

Spec No: 002-08367

## Spec Title: MB39A123 6 CH DC/DC CONVERTER IC WITH SYNCHRONOUS RECTIFICATION DATASHEET

Replaced by: None

### MB39A123

## 6 ch DC/DC Converter IC with Synchronous Rectification Datasheet

### Description

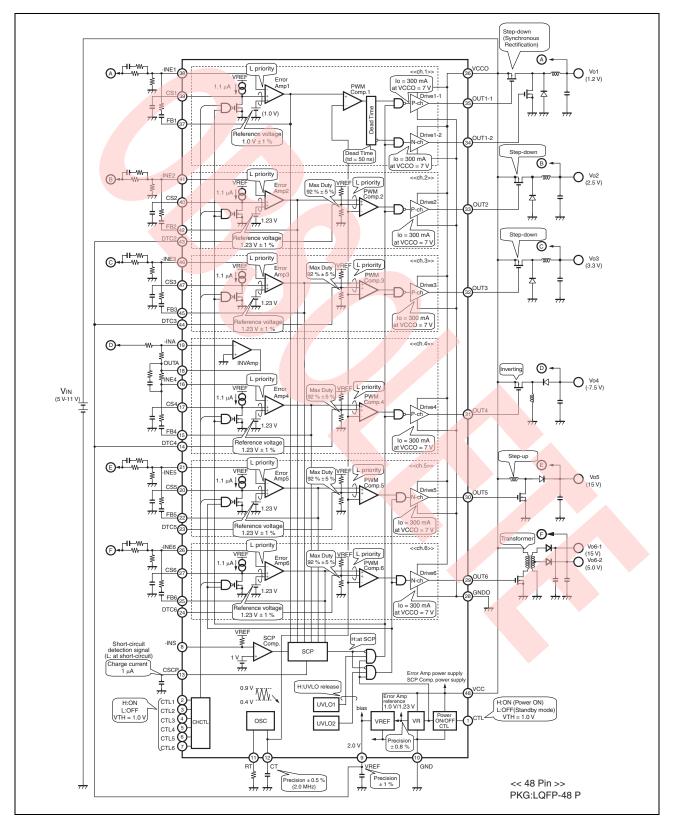

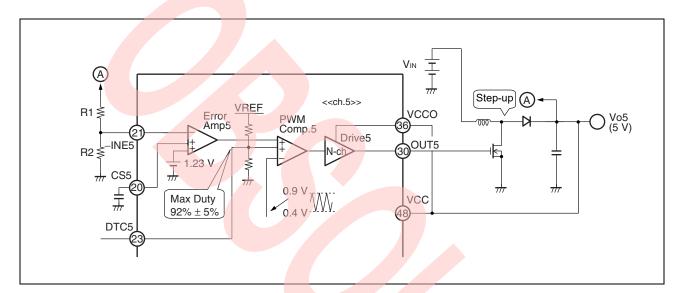

MB39A123 is a 6-channel DC/DC converter IC using pulse width modulation (PWM), and it is suitable for up conversion, down conversion, and up/down conversion. MB39A123 is built in 6 channels into LQFP-48P package and this IC can control and soft-start at each channel. MB39A123 is suitable for power supply of high performance potable instruments such as a digital still camera (DSC).

#### Features

- Supports for step-down with synchronous rectification (ch.1)

- Supports for step-down and up/down Zeta conversion (ch.2 to ch.4)

- Supports for step-up and up/down Sepic conversion (ch.5, ch.6)

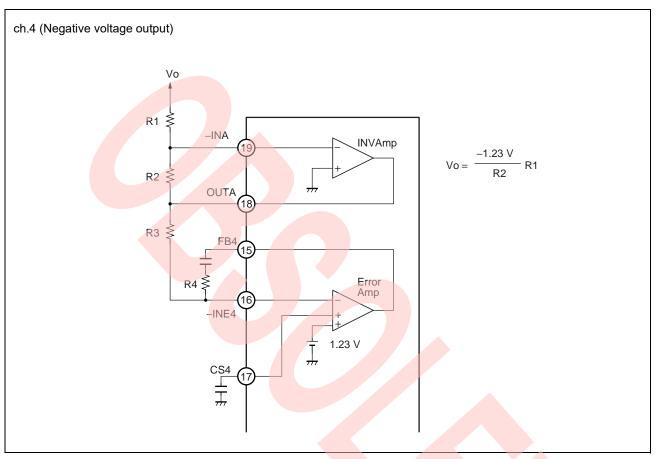

- Negative voltage output (Inverting amplifier) (ch.4)

- Low voltage start-up (ch.5, ch.6) : 1.7 V

- Power supply voltage range : 2.5 V to 11 V

- Reference voltage : 2.0 V ± 1%

- Error amplifier reference voltage : 1.0 V ± 1% (ch.1), 1.23 V ± 1% (ch.2 to ch.6)

- Oscillation frequency range : 200 kHz to 2.0 MHz

- Standby current : 0 µA (Typ)

- Built-in soft-start circuit independent of loads

- Built-in totem-pole type output for MOS FET

- Short-circuit detection capability by external signal (–INS terminal)

- Package : LQFP-48 pin

#### Applications

- Digital still camera (DSC)

- Digital video camera (DVC)

- Surveillance camera etc.

### **Block Diagram**

### Contents

| Pin Descriptions                                  |    |

|---------------------------------------------------|----|

|                                                   | 6  |

| Absolute Maximum Ratings                          | 0  |

| Recommended Operating Conditions                  | 7  |

| Electrical Characteristics                        |    |

| Typical Characteristics                           | 11 |

| Functional Description                            | 15 |

| DC/DC Converter Function                          | 15 |

| Channel Control Function                          |    |

| Protection Function                               | 16 |

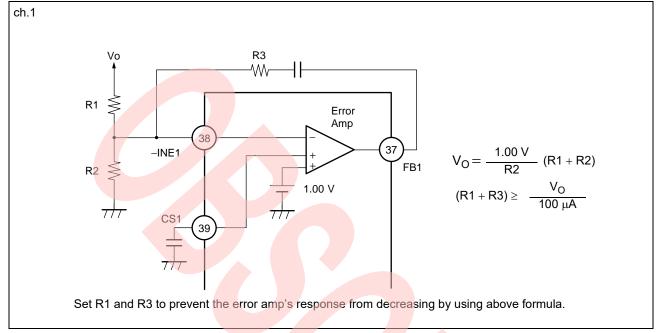

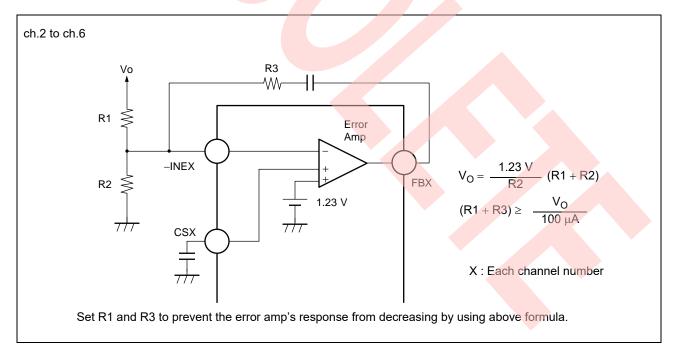

| Setting the Output Voltage                        | 17 |

| Setting the Triangular Wave Oscillation Frequency | 18 |

| Setting the Soft-Start Time                       | 19 |

| Processing When Not Using CS Terminal             |    |

| Setting the Time Constant for Timer-Latch         |    |

| Short-Circuit Protection Circuit                  | 21 |

| Processing When Not Using CSCP Terminal           | 22 |

| Setting the Dead Time (ch.2 to ch.6)              | 23 |

| Processing When Not Using ch.4 INV AMP            |    |

| Operation Explanation when CTL Turns ON and OFF   |    |

| About Low-Voltage Operation                    | 29 |

|------------------------------------------------|----|

| I/O Equivalent Circuit                         |    |

| Usage Precautions                              |    |

| Ordering Information                           |    |

| EV Board Ordering Information                  |    |

| RoHS Compliance information of Pb-free Version |    |

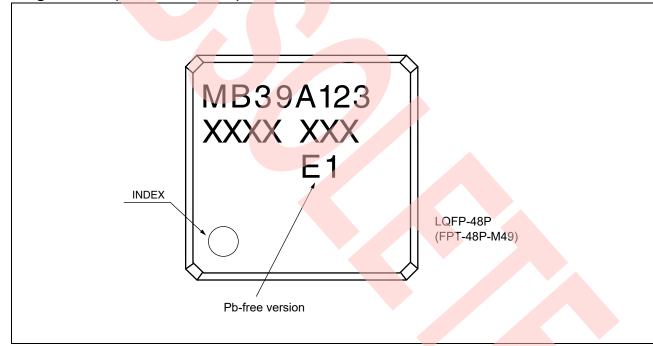

| Marking Format (Pb-free Version)               |    |

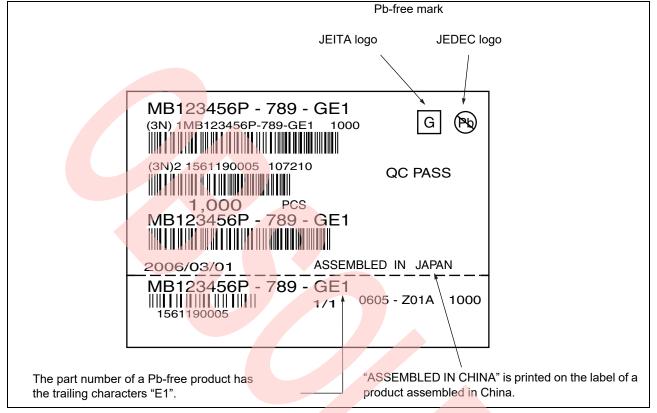

| Labeling Sample (Pb-free Version)              |    |

| MB39A123PMT Recommended Conditions of          |    |

| Moisture Sensitivity Level                     | 33 |

| Mounting Conditions                            |    |

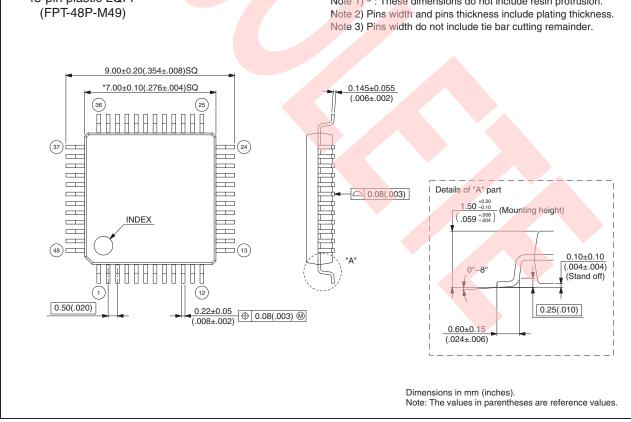

| Package Dimensions                             | 35 |

| Document History Page                          | 36 |

| Sales, Solutions, and Legal Information        |    |

| Worldwide Sales and Design Support             |    |

| Products                                       |    |

| PSoC®Solutions                                 |    |

| Cypress Developer Community                    |    |

| Technical Support                              |    |

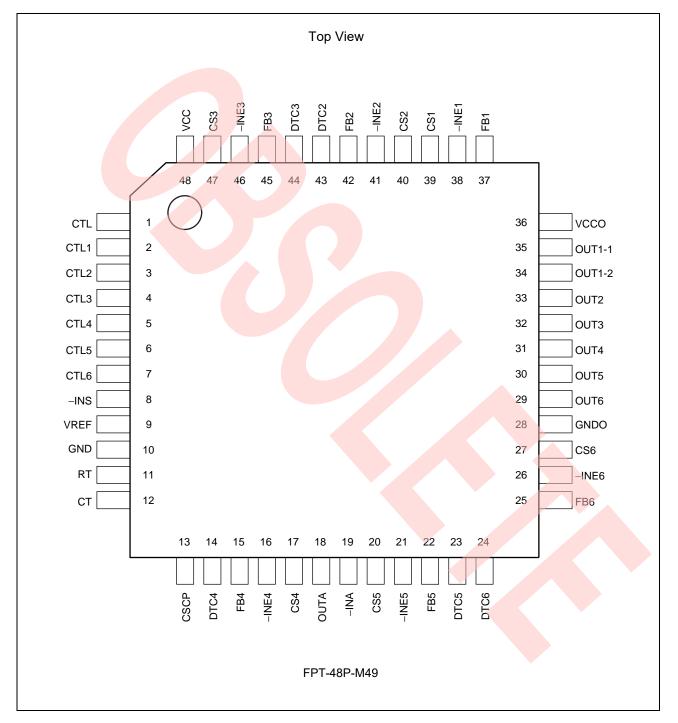

### **Pin Assignments**

### **Pin Descriptions**

| Block Name | Pin No. | Pin Name | I/O | Description                                                                                 |  |  |  |  |  |  |  |

|------------|---------|----------|-----|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|            | 37      | FB1      | 0   | ch.1: Error amplifier output terminal                                                       |  |  |  |  |  |  |  |

|            | 38      | -INE1    | I   | ch.1: Error amplifier inverted input terminal                                               |  |  |  |  |  |  |  |

| ch.1       | 39      | CS1      | -   | ch.1: Soft-start setting capacitor connection terminal                                      |  |  |  |  |  |  |  |

|            | 35      | OUT1-1   | 0   | ch.1: P-ch drive output terminal (External main side FET gate driving)                      |  |  |  |  |  |  |  |

|            | 34      | OUT1-2   | 0   | ch.1: N-ch drive output terminal (External synchronous rectification side FET gate driving) |  |  |  |  |  |  |  |

|            | 43      | DTC2     |     | ch.2: Dead time control terminal                                                            |  |  |  |  |  |  |  |

|            | 42      | FB2      | 0   | ch.2: Error amplifier output terminal                                                       |  |  |  |  |  |  |  |

| ch.2       | 41      | -INE2    |     | ch.2: Error amplifier inverted input terminal                                               |  |  |  |  |  |  |  |

|            | 40      | CS2      | -   | ch.2: Soft-start setting capacitor connection terminal                                      |  |  |  |  |  |  |  |

|            | 33      | OUT2     | 0   | ch.2: P-ch drive output terminal                                                            |  |  |  |  |  |  |  |

|            | 44      | DTC3     | I   | ch.3: Dead time control terminal                                                            |  |  |  |  |  |  |  |

|            | 45      | FB3      | 0   | ch.3: Error amplifier output terminal                                                       |  |  |  |  |  |  |  |

| ch.3       | 46      | -INE3    | 1   | c <mark>h.3:</mark> Error amplifier invert <mark>e</mark> d input terminal                  |  |  |  |  |  |  |  |

|            | 47      | CS3      | -   | ch.3: Soft-start setting capacitor connection terminal                                      |  |  |  |  |  |  |  |

|            | 32      | OUT3     | 0   | ch.3: P-ch drive output terminal                                                            |  |  |  |  |  |  |  |

|            | 14      | DTC4     | Ι   | ch.4: Dead time control terminal                                                            |  |  |  |  |  |  |  |

|            | 15      | FB4      | 0   | ch.4: Error amplifier output terminal                                                       |  |  |  |  |  |  |  |

|            | 16      | -INE4    | Ι   | ch.4: Error amplifier inverted input terminal                                               |  |  |  |  |  |  |  |

| ch.4       | 17      | CS4      | -   | ch.4: Soft-start setting capacitor connection terminal                                      |  |  |  |  |  |  |  |

|            | 31      | OUT4     | 0   | ch.4: P-ch drive output terminal                                                            |  |  |  |  |  |  |  |

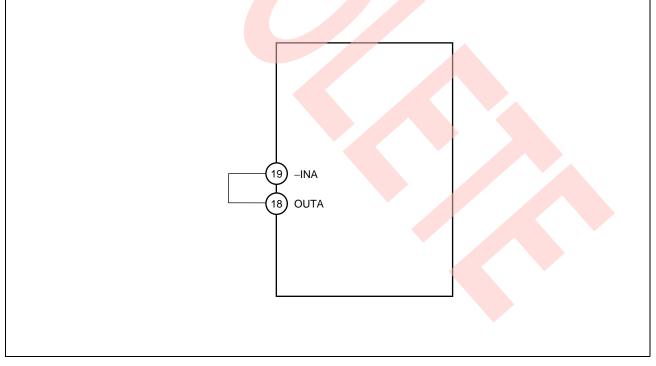

|            | 19      | -INA     | I   | Inverting amplifier input terminal                                                          |  |  |  |  |  |  |  |

|            | 18      | OUTA     | 0   | Inverting amplifier output terminal                                                         |  |  |  |  |  |  |  |

|            | 23      | DTC5     | I   | ch.5: Dead time control terminal                                                            |  |  |  |  |  |  |  |

|            | 22      | FB5      | 0   | ch.5: Error amplifier output terminal                                                       |  |  |  |  |  |  |  |

| ch.5       | 21      | -INE5    | I   | ch.5: Error amplifier inverted input terminal                                               |  |  |  |  |  |  |  |

|            | 20      | CS5      | -   | ch.5: Soft-start setting capacitor connection terminal                                      |  |  |  |  |  |  |  |

|            | 30      | OUT5     | 0   | ch.5: N-ch drive output terminal                                                            |  |  |  |  |  |  |  |

| ch.6       | 24      | DTC6     | I   | ch.6: Dead time control terminal                                                            |  |  |  |  |  |  |  |

|            | 25      | FB6      | 0   | ch.6: Error amplifier output terminal                                                       |  |  |  |  |  |  |  |

|            | 26      | -INE6    | I   | ch.6: Error amplifier inverted input terminal                                               |  |  |  |  |  |  |  |

|            | 27      | CS6      | -   | ch.6: Soft-start setting capacitor connection terminal                                      |  |  |  |  |  |  |  |

|            | 29      | OUT6     | 0   | ch.6: N-ch drive output terminal                                                            |  |  |  |  |  |  |  |

| 080        | 12      | СТ       | _   | Triangular wave frequency setting capacitor connection terminal                             |  |  |  |  |  |  |  |

| OSC        | 11      | RT       | -   | Triangular wave frequency setting resistor connection terminal                              |  |  |  |  |  |  |  |

| Block Name     | Pin No.  | Pin Name | I/O                               | Description                                                   |

|----------------|----------|----------|-----------------------------------|---------------------------------------------------------------|

|                | 1        | CTL      | I                                 | Power supply control terminal                                 |

|                | 2        | CTL1     | I                                 | ch.1 control terminal                                         |

|                | 3        | CTL2     | I                                 | ch.2 control terminal                                         |

|                | 4        | CTL3     | I                                 | ch.3 control terminal                                         |

| Control        | 5        | CTL4     | I                                 | ch.4 control terminal                                         |

|                | 6 CTL5 I |          |                                   | ch.5 control terminal                                         |

|                | 7        | CTL6     |                                   | ch.6 control terminal                                         |

|                | 13       | CSCP     | -                                 | Short-circuit detection circuit capacitor connection terminal |

|                | 8        | -iNS     | Ι                                 | Short-circuit detection comparator inverted input terminal    |

|                | 36       | VCCO     | -                                 | Drive output block power supply terminal                      |

|                | 48       | VCC      | -                                 | Power supply terminal                                         |

| Power 9 VREF O |          | 0        | Reference voltage output terminal |                                                               |

|                | 28       | GNDO     | -                                 | Drive output block ground terminal                            |

|                | 10       | GND      | -                                 | Ground terminal                                               |

## Absolute Maximum Ratings

| Parameter            | Symbol           | Conditions                                             | Rat | Unit              |      |

|----------------------|------------------|--------------------------------------------------------|-----|-------------------|------|

| Falameter            | Symbol           | conditions                                             | Min | Max               | Onit |

| Power supply voltage | V <sub>CC</sub>  | VCC, VC <mark>CO terminals</mark>                      | _   | 12                | V    |

| Output current       | Ι <sub>Ο</sub>   | OUT1-1, OUT1-2, OUT2 to OUT6 terminals                 | -   | 20                | mA   |

| Peak output current  | I <sub>OP</sub>  | OUT1-1, OUT1-2, OUT2 to OUT6 terminals Duty $\leq 5\%$ | -   | 400               | mA   |

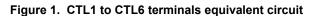

| Power dissipation    | PD               | Ta ≤ +25°C (LQFP-48P)                                  | _   | 2000 <sup>1</sup> | mW   |

| Storage temperature  | T <sub>STG</sub> | -                                                      | -55 | +125              | °C   |

Warning: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

<sup>1.</sup> When mounted on a 117 mm × 84 mm × 0.8 mm FR-4 boards.

### **Recommended Operating Conditions**

| Parameter                          | Symbol           | Conditions                                                               |       | Value |                       | Unit |  |

|------------------------------------|------------------|--------------------------------------------------------------------------|-------|-------|-----------------------|------|--|

| Falameter                          | Symbol           | Conditions                                                               | Min   | Тур   |                       |      |  |

| Start power supply voltage         | V <sub>CC</sub>  | ch.5, ch.6, VCC, VCCO terminals                                          | 1.7   | -     | 11                    | V    |  |

| Power supply voltage               | Vcc              | VCC, VCCO terminals                                                      | 2.5   | 4     | 11                    | V    |  |

| Reference voltage output current   | IREF             | VREF terminal                                                            | -1    | -     | 0                     | mA   |  |

| Input voltage                      | VINE             | -INE1 to -INE6 terminals                                                 | 0     | -     | $V_{CC} - 0.9$        | V    |  |

|                                    |                  | -INA terminal                                                            | - 0.2 | -     | V <sub>CC</sub> - 1.8 | V    |  |

|                                    |                  | -INS terminal                                                            | 0     | -     | V <sub>REF</sub>      | V    |  |

|                                    | V <sub>DTC</sub> | DTC2 to DTC6 terminals                                                   | 0     | -     | V <sub>REF</sub>      | V    |  |

| Control input voltage              | V <sub>CTL</sub> | CTL, CTL1 to CTL6 terminals                                              | 0     | -     | 11                    | V    |  |

| Output current                     | lo               | OUT1-1, OUT1-2, OUT2 to OUT6<br>terminals                                | -15   | -     | +15                   | mA   |  |

| Total gate charge of external FET  | Qg               | OUT1-1, OUT1-2, OUT2 to OUT6<br>terminals connection FET<br>fosc = 2 MHz | _     | 2.6   | 7.5                   | nC   |  |

| Oscillation frequency              | fosc             | -                                                                        | 0.2   | 1.0   | 2.0                   | MHz  |  |

| Timing capacitor                   | CT               | -                                                                        | 27    | 100   | 680                   | pF   |  |

| Timing resistor                    | R <sub>T</sub>   | -                                                                        | 3.0   | 6.8   | 39                    | kΩ   |  |

| Soft-start capacitor               | CS               | CS1 to CS6 terminals                                                     | -     | 0.1   | 1.0                   | μF   |  |

| Short-circuit detection capacitor  | C <sub>SCP</sub> | -                                                                        | -     | 0.1   | 1.0                   | μF   |  |

| Reference voltage output capacitor | C <sub>REF</sub> | -                                                                        | -     | 0.1   | 1.0                   | μF   |  |

| Operating ambient temperature      | Та               | -                                                                        | -30   | +25   | +85                   | °C   |  |

**Warning:** The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

### **Electrical Characteristics**

| (VCC = VCCO = ) | $4 \text{ V}, \text{ Ta} = +25^{\circ}\text{C}$ |

|-----------------|-------------------------------------------------|

|-----------------|-------------------------------------------------|

| Ba                                                 | Parameter                       |                                         |                       | Conditions                                                                                             |       | Value |       | Unit |

|----------------------------------------------------|---------------------------------|-----------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| Fa                                                 | rameter                         | Symbol                                  | Pin No.               | Conditions                                                                                             | Min   | Тур   | Max   | Unit |

| Reference Voltage                                  | Output voltage                  | V <sub>REF1</sub>                       | 9                     | VREF = 0 mA                                                                                            | 1.98  | 2.00  | 2.02  | V    |

| Block [VREF]                                       |                                 | V <sub>REF2</sub>                       | 9                     | $V_{CC} = 2.5 V$ to 11 V                                                                               | 1.975 | 2.000 | 2.025 | V    |

|                                                    |                                 | V <sub>REF3</sub>                       | 9                     | VREF = 0 mA to $-1$ mA                                                                                 | 1.975 | 2.000 | 2.025 | V    |

|                                                    | Input stability                 | Line                                    | 9                     | $V_{CC} = 2.5 \text{ V to } 11 \text{ V}^2$                                                            | -     | 2     | -     | mV   |

|                                                    | Load stability                  | Load                                    | 9                     | VREF = 0 mA to $-1 \text{ mA}^2$                                                                       | -     | 2     | -     | mV   |

|                                                    | Temperature stability           | ΔV <sub>REF</sub> /V <sub>R</sub><br>EF | 9                     | $Ta = 0^{\circ}C \text{ to } +85^{\circ}C^2$                                                           | -     | 0.20  | -     | %    |

|                                                    | Short-circuit output<br>current | los                                     | 9                     | $VREF = 0 V^2$                                                                                         | -     | -130  | -     | mA   |

| Under voltage                                      | Threshold voltage               | V <sub>TH1</sub>                        | 35                    | V <sub>CC</sub> = ⊥                                                                                    | 1.7   | 1.8   | 1.9   | V    |

| lockout protection                                 | Hysteresis width                | V <sub>H1</sub>                         | 35                    | -                                                                                                      | 0.05  | 0.1   | 0.2   | V    |

| (ch.1 to ch.4)<br>[UVLO1]                          | Reset voltage                   | V <sub>RST1</sub>                       | 35                    | V <sub>cc</sub> = ¥                                                                                    | 1.55  | 1.7   | 1.85  | V    |

| Under voltage                                      | Threshold voltage               | V <sub>TH2</sub>                        | 30                    | V <sub>cc</sub> = _⊼                                                                                   | 1.35  | 1.5   | 1.65  | V    |

| lockout protection<br>circuit Block                | Hysteresis width                | V <sub>H2</sub>                         | 30                    | -                                                                                                      | 0.02  | 0.05  | 0.1   | V    |

| (ch.5, ch.6)<br>[UVLO2]                            | Reset voltage                   | V <sub>RST2</sub>                       | 30                    | V <sub>CC</sub> = $-\frac{1}{2}$                                                                       | 1.27  | 1.45  | 1.63  | V    |

| Short-circuit                                      | Threshold voltage               | V <sub>TH</sub>                         | 13                    | -                                                                                                      | 0.65  | 0.70  | 0.75  | V    |

| detection Block<br>[SCP]                           | Input source current            | I <sub>CSCP</sub>                       | 13                    | -                                                                                                      | -1.4  | -1.0  | -0.6  | μΑ   |

| Triangular Wave<br>Oscillator Block                | Oscillation frequency           | fosc1                                   | 29 to 35              | $C_{T} = 100 \text{ pF},$<br>$R_{T} = 6.8 \text{ k}\Omega$                                             | 0.95  | 1.0   | 1.05  | MHz  |

| [OSC]                                              |                                 | fosc2                                   | 29 to 35              | $C_{T} = 100 \text{ pF}, R_{T} = 6.8 \text{ k}\Omega$<br>$V_{CC} = 2.5 \text{ V to } 11 \text{ V}$     | 0.945 | 1.0   | 1.055 | MHz  |

|                                                    | Frequency Input stability       | ∆f <sub>OSC</sub> /<br>f <sub>OSC</sub> | 29 to 35              | $C_{T} = 100 \text{ pF}, R_{T} = 6.8 \text{ k}\Omega$<br>$V_{CC} = 2.5 \text{ V to } 11 \text{ V}^{2}$ | -     | 1.0   | -     | %    |

|                                                    | Frequency temperature stability | ∆f <sub>OSC</sub> /<br>f <sub>OSC</sub> | 29 to 35              | C <sub>T</sub> = 100 pF, R <sub>T</sub> = 6.8 kΩ<br>Ta = 0°C to +85°C <sup>2</sup>                     | -     | 1.0   | -     | %    |

| Soft-Start Block<br>(ch.1 to ch.6) [CS1<br>to CS6] | Charge current                  | I <sub>CS</sub>                         | 17,20,27,<br>39,40,47 | CS1 to CS6 = $0$ V                                                                                     | -1.45 | -1.1  | -0.75 | μΑ   |

| Da                                | romotor               | Symbol                            | Din No.               | Conditions                                                                                                                 |       | Unit  |       |      |

|-----------------------------------|-----------------------|-----------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| Parameter                         |                       | Symbol                            | Pin No.               | Conditions                                                                                                                 | Min   | Тур   | Мах   | Unit |

| Error Amp Block<br>(ch.1)         | Reference voltage     | V <sub>TH1</sub>                  | 38                    | V <sub>CC</sub> = 2.5 V to 11 V<br>Ta = +25°C                                                                              | 0.990 | 1.000 | 1.010 | V    |

| [Error Amp1]                      |                       | V <sub>TH2</sub>                  | 38                    | $V_{CC} = 2.5 \text{ V to } 11 \text{ V}$<br>Ta = 0°C to +85°C <sup>2</sup>                                                | 0.988 | 1.000 | 1.012 | V    |

|                                   | Temperature stability | $\Delta V_{TH}/V_{TH}$            | 38                    | $Ta = 0^{\circ}C \text{ to } +85^{\circ}C^2$                                                                               | -     | 0.1   | -     | %    |

|                                   | Input bias current    | Ι <sub>Β</sub>                    | 38                    | -INE1 = 0 V                                                                                                                | -120  | -30   | -     | nA   |

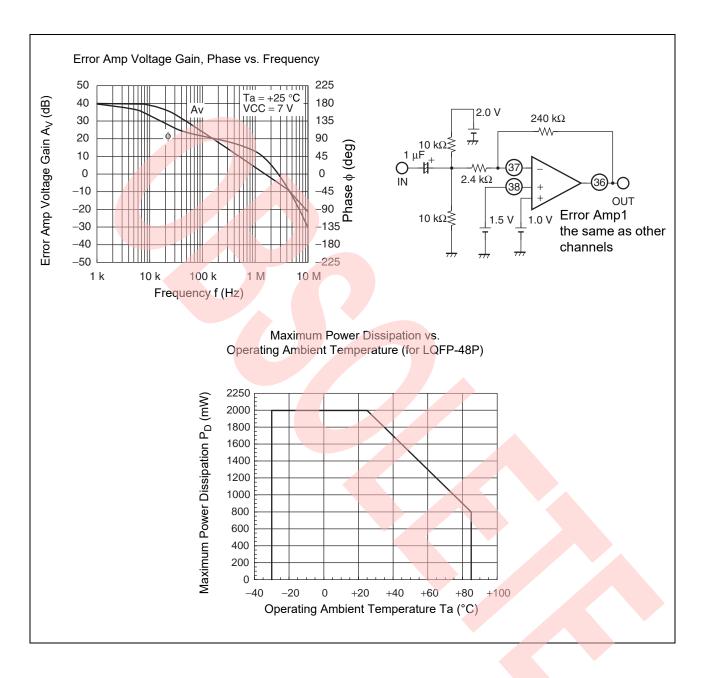

|                                   | Voltage gain          | A <sub>V</sub>                    | 37                    | DC <sup>2</sup>                                                                                                            | -     | 100   | -     | dB   |

|                                   | Frequency bandwidth   | BW                                | 37                    | $A_V = 0 dB^2$                                                                                                             | -     | 1.4   | -     | MHz  |

|                                   | Output voltage        | V <sub>OH</sub>                   | 37                    | -                                                                                                                          | 1.7   | 1.9   | -     | V    |

|                                   |                       | V <sub>OL</sub>                   | 37                    | -                                                                                                                          | -     | 40    | 200   | mV   |

|                                   | Output source current | ISOURCE                           | 37                    | FB1 = 0.65 V                                                                                                               | -     | -2    | —1    | mA   |

|                                   | Output sink current   | I <sub>SINK</sub>                 | 37                    | FB1 = 0.65 V                                                                                                               | 150   | 200   | _     | μΑ   |

| Error Amp Block<br>(ch.2 to ch.6) | Reference voltage     | V <sub>TH3</sub>                  | 16, 21, 26,<br>41, 46 | V <sub>CC</sub> = 2.5 V to 11 V<br>Ta = +25°C                                                                              | 1.217 | 1.230 | 1.243 | V    |

| [Error Amp2 to Error<br>Amp6]     |                       | V <sub>TH4</sub>                  | 16, 21, 26,<br>41, 46 | $\frac{V_{CC}}{Ta} = 2.5 \text{ V to } 11 \text{ V}$ $\frac{V_{CC}}{Ta} = 0^{\circ} \text{C to } +85^{\circ} \text{C}^{2}$ | 1.215 | 1.230 | 1.245 | V    |

|                                   | Temperature stability | ΔV <sub>TH</sub> /V <sub>TH</sub> | 16, 21, 26,<br>41, 46 | $Ta = 0^{\circ}C \text{ to } +85^{\circ}C^2$                                                                               | -     | 0.1   | -     | %    |

|                                   | Input bias current    | I <sub>B</sub>                    | 16, 21, 26,<br>41, 46 | -INE2 to $-INE6 = 0$ V                                                                                                     | -120  | -30   | -     | nA   |

|                                   | Voltage gain          | Av                                | 15, 22, 25,<br>42, 45 | DC <sup>2</sup>                                                                                                            | -     | 100   | -     | dB   |

|                                   | Frequency bandwidth   | BW                                | 15, 22, 25,<br>42, 45 | $A_V = 0 dB^2$                                                                                                             | -     | 1.4   | -     | MHz  |

|                                   | Output voltage        | V <sub>OH</sub>                   | 15, 22, 25,<br>42, 45 | -                                                                                                                          | 1.7   | 1.9   | -     | V    |

|                                   |                       | V <sub>OL</sub>                   | 15, 22, 25,<br>42, 45 | -                                                                                                                          |       | 40    | 200   | mV   |

| Error Amp Block<br>(ch.2 to ch.6) | Output source current | I <sub>SOURCE</sub>               | 15, 22, 25,<br>42, 45 | FB2  to  FB6 = 0.65  V                                                                                                     | -     | -2    | -1    | mA   |

| [Error Amp2 to Error<br>Amp6]     | Output sink current   | I <sub>SINK</sub>                 | 15, 22, 25,<br>42, 45 | FB2  to  FB6 = 0.65  V                                                                                                     | 150   | 200   | -     | μΑ   |

| Inverting Amp Block               | Input offset voltage  | V <sub>IO</sub>                   | 18                    | OUTA = 1.23V                                                                                                               | -10   | 0     | + 10  | mV   |

| (ch.4)<br>[Inv Amp]               | Input bias current    | Ι <sub>Β</sub>                    | 19                    | -INA = 0V                                                                                                                  | -120  | -30   | -     | nA   |

| [                                 | Voltage gain          | A <sub>V</sub>                    | 18                    | DC <sup>2</sup>                                                                                                            | -     | 100   | -     | dB   |

|                                   | Frequency bandwidth   | BW                                | 18                    | $A_V = 0 dB^2$                                                                                                             | -     | 1.0   | -     | MHz  |

|                                   | Output voltage        | V <sub>OH</sub>                   | 18                    | -                                                                                                                          | 1.7   | 1.9   | -     | V    |

|                                   |                       | V <sub>OL</sub>                   | 18                    | -                                                                                                                          | -     | 40    | 200   | mV   |

|                                   | Output source current | ISOURCE                           | 18                    | OUTA = 1.23V                                                                                                               | -     | -2    | -1    | mA   |

|                                   | Output sink current   | I <sub>SINK</sub>                 | 18                    | OUTA = 1.23V                                                                                                               | 150   | 200   | -     | μΑ   |

| PWM Comparator                    | Threshold voltage     | V <sub>T0</sub>                   | 34, 35                | Duty cycle = $0\%$                                                                                                         | 0.35  | 0.4   | 0.45  | V    |

| Block (ch.1)<br>[PWM Comp.1]      |                       | V <sub>T100</sub>                 | 34, 35                | Duty cycle = 100%                                                                                                          | 0.85  | 0.9   | 0.95  | V    |

| De                                           | rameter                 | Cumhal              | Pin No.              | Conditions                                                                         |      | Value   |      | Unit |

|----------------------------------------------|-------------------------|---------------------|----------------------|------------------------------------------------------------------------------------|------|---------|------|------|

| Pa                                           | Symbol                  | PIN NO.             | Conditions           | Min                                                                                | Тур  | Тур Мах |      |      |

| PWM Comparator                               | Threshold               | V <sub>T0</sub>     | 29 to 33             | Duty cycle = 0%                                                                    | 0.35 | 0.4     | 0.45 | V    |

| Block (ch.2 to ch.6)<br>[PWM Comp.2 to       | voltage                 | V <sub>T100</sub>   | 29 to 33             | Duty cycle = 100%                                                                  | 0.85 | 0.9     | 0.95 | V    |

| PWM Comp.6]                                  | Maximum duty cycle      | Dtr                 | 29 to 33             | $\begin{array}{l} C_T = 100 \ pF, \\ R_T = 6.8 \ k\Omega \end{array}$              | 87   | 92      | 97   | %    |

| Output Block<br>(ch.1 to ch.6)               | Output source current   | I <sub>SOURCE</sub> | 29 to 35             | $\begin{array}{l} \text{Duty} \leq 5\% \\ \text{OUT} \ = 0 \ \text{V} \end{array}$ | -    | -130    | -75  | mA   |

| [Drive1 to Drive6]                           | Output sink current     | ISINK               | 29 to 35             | $\begin{array}{l} \text{Duty} \leq 5\% \\ \text{OUT} \ = 4 \ V \end{array}$        | 75   | 130     | _    | mA   |

|                                              | Output on resistor      | R <sub>OH</sub>     | 29 to 35             | OUT = -15  mA                                                                      | -    | 18      | 27   | Ω    |

|                                              |                         | R <sub>OL</sub>     | 29 to 35             | OUT = 15 mA                                                                        | _    | 18      | 27   | Ω    |

|                                              | Dead time               | t <sub>D1</sub>     | <mark>34</mark> , 35 | OUT2 ↓ - OUT1 ↓ 2                                                                  | _    | 50      | -    | ns   |

|                                              |                         | t <sub>D2</sub>     | <mark>34,</mark> 35  | OUT1 🖌 – OUT2 🛧 2                                                                  | _    | 50      | -    | ns   |

| Short-Circuit                                | Threshold voltage       | V <sub>TH</sub>     | 35                   | -                                                                                  | 0.97 | 1.00    | 1.03 | V    |

| Detection<br>Comparator Block<br>[SCP Comp.] | Input bias current      | Ι <sub>Β</sub>      | 8                    | -INS = 0 V                                                                         | -25  | -20     | -17  | μΑ   |

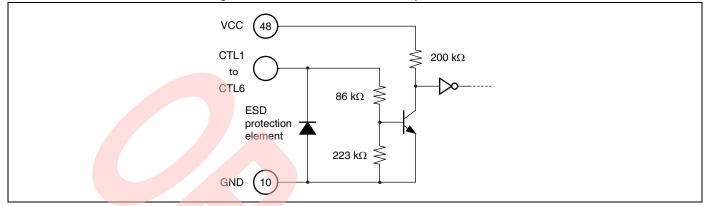

| Control Block                                | Output on condition     | VIH                 | 1 to 7               | CTL, CTL1 to CTL6                                                                  | 1.5  | _       | 11   | V    |

| (CTL,<br>CTL1 to CTL6)<br>[CTL, CHCTL]       | Output off<br>condition | VIL                 | 1 to 7               | CTL, CTL1 to CTL6                                                                  | 0    | -       | 0.5  | V    |

|                                              | Input current           | ICTLH               | 1 to 7               | CTL, CTL1 to CTL6 = $3 V$                                                          | 5    | 30      | 60   | μΑ   |

|                                              |                         | CTLL                | 1 to 7               | CTL, CTL1 to CTL6 = 0 V                                                            | _    | _       | 1    | μΑ   |

| General                                      | Standby                 | Iccs                | 48                   | CTL, CTL1 to $CTL6 = 0 V$                                                          | _    | 0       | 2    | μΑ   |

|                                              | current                 | I <sub>CCSO</sub>   | 36                   | CTL = 0 V                                                                          | -    | 0       | 1    | μΑ   |

|                                              | Power supply current    | I <sub>CC</sub>     | 48                   | CTL = 3 V                                                                          | -    | 4.5     | 6.8  | mA   |

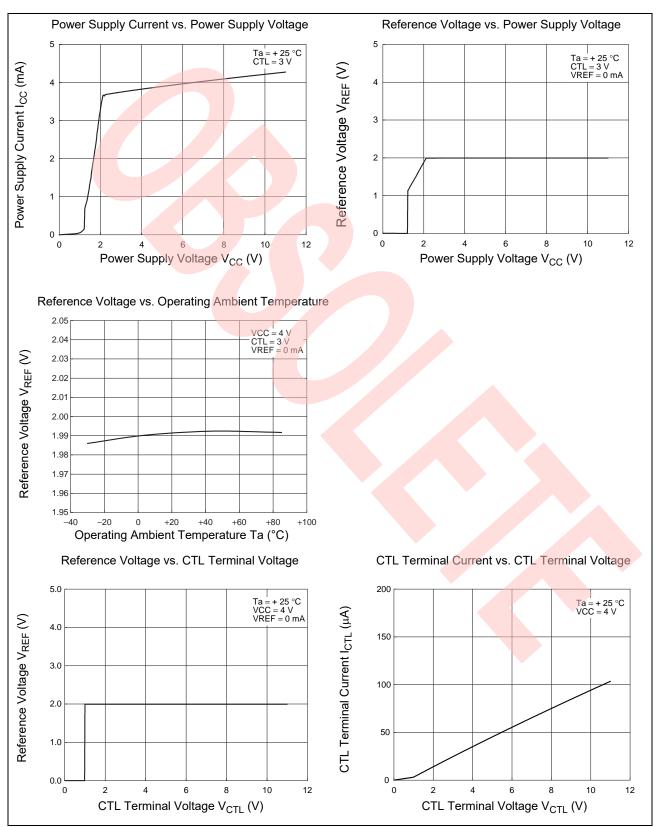

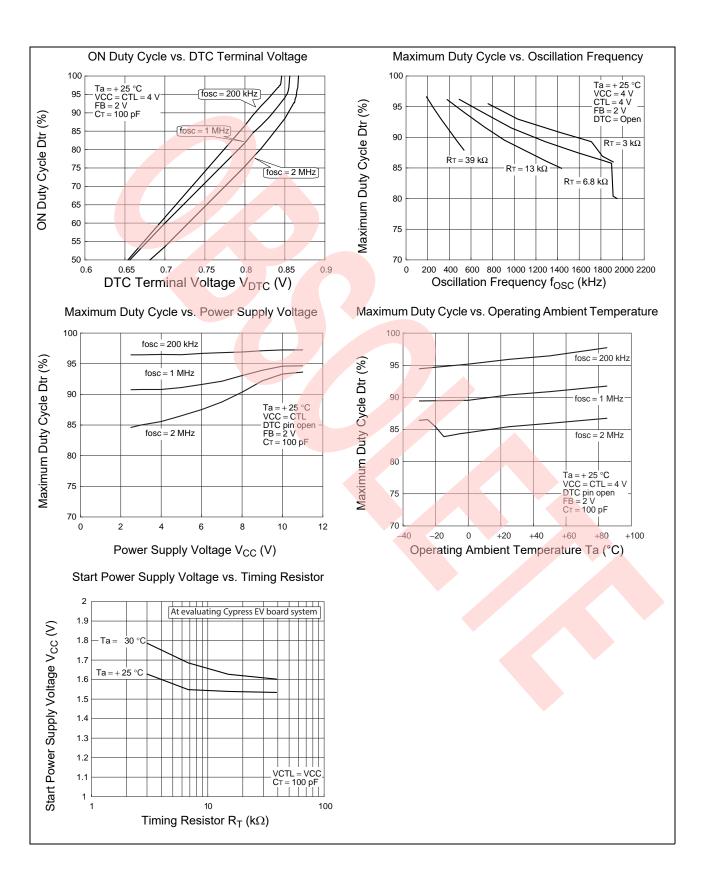

### **Typical Characteristics**

### Functional Description

#### **DC/DC Converter Function**

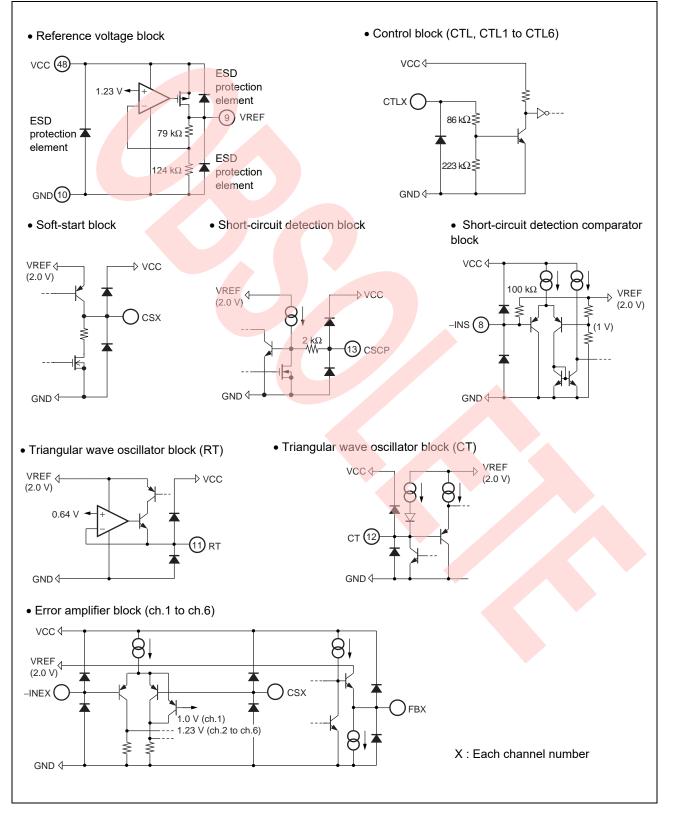

#### Reference voltage block (VREF)

The reference voltage circuit uses the voltage supplied from VCC terminal (pin 48) to generate a temperature compensated reference voltage (2.0 V Typ) used as the reference voltage for the internal circuits of the IC. It is also possible to supply the load current of up to 1 mA to external circuits as a reference voltage through the VREF terminal (pin 9).

#### Triangular wave oscillator block (OSC)

The triangular wave oscillator block generates the triangular wave oscillation waveform width of 0.4 V lower limit and 0.5 V amplitude by the timing resistor ( $R_T$ ) connected to the RT terminal (pin 11), and the timing capacitor ( $C_T$ ) connected to the CT terminal (pin 12). The triangular wave is input to the PWM comparator circuits on the IC.

#### Error amplifier block (Error Amp1 to Error Amp6)

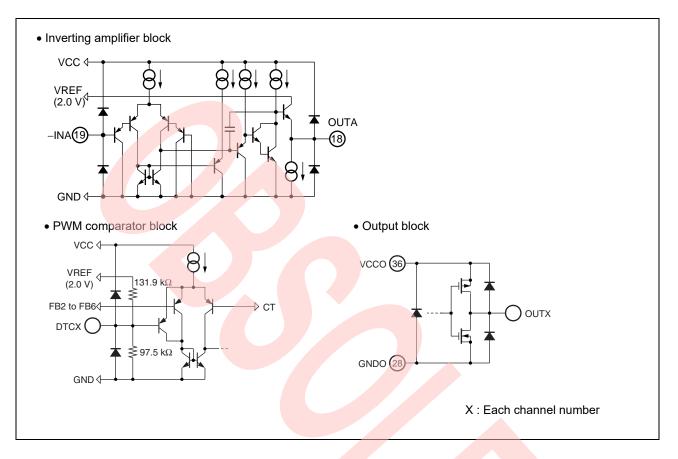

The error amplifier detects output voltage of the DC/DC converter and outputs PWM control signals. An arbitrary loop gain can be set by connecting a feedback resistor and capacitor from the output terminal to inverted input terminal of the error amplifier, enabling stable phase compensation for the system.

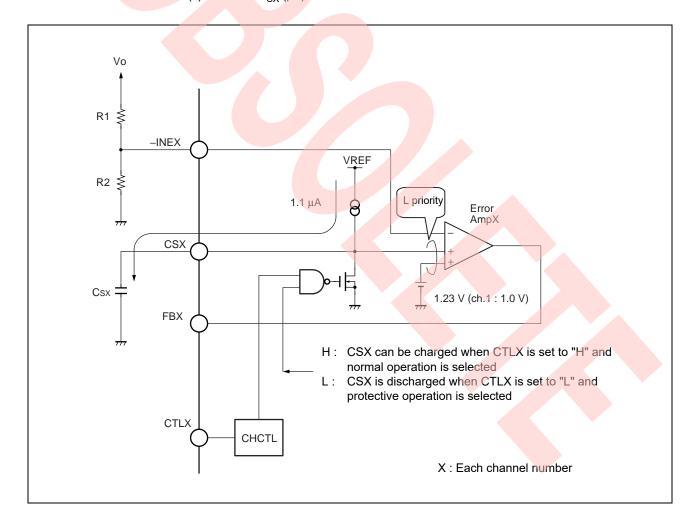

You can prevent surge currents when the IC is turned on by connecting soft-start capacitors to the CS1 terminal (pin 39) to CS6 terminal (pin 27) which are the noninverting input terminals of the error amplifier. The IC is started up at constant soft-start time intervals independent of the output load of the DC/DC converter.

#### PWM comparator block (PWM Comp.1 to PWM Comp.6)

The PWM comparator block is a voltage-pulse width converter that controls the output duty depending on the input/output voltage.

An output transistor is turned on, during intervals when the error amplifier output voltage and DTC voltage (ch.2 to ch.6) are higher than the triangular wave voltage.

#### Output block (Drive1 to Drive6)

The output circuit uses a totem-pole configuration and is capable of driving an external P-ch MOS FET (main side of ch.1, ch.2, ch.3 and ch.4) and N-ch MOS FET (synchronous rectification side of ch.1, ch.5 and ch.6).

#### **Channel Control Function**

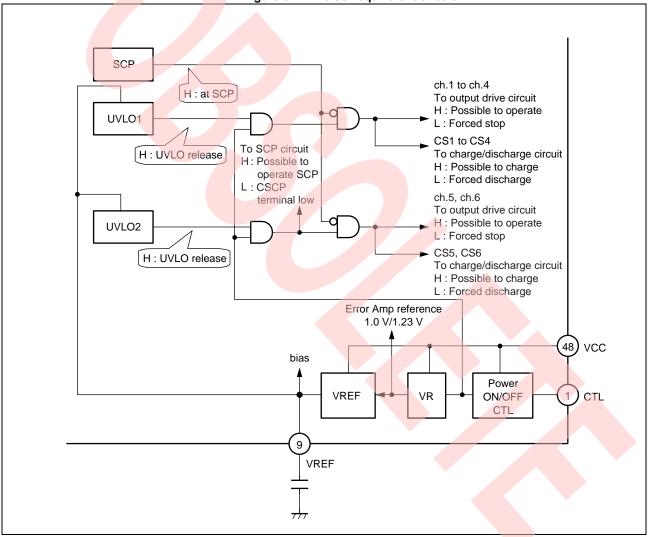

Use the CTL terminal (pin 1), CTL1 terminal (pin 2), CTL2 terminal (pin 3), CTL3 terminal (pin 4), CTL4 terminal (pin 5), CTL5 terminal (pin 6), and CTL6 terminal (pin 7) to set ON/OFF to the main and each channels.

| CTL | CTL1 | CTL2 | CTL3 | CTL4 | CTL5 | CTL6 | Power | ch.1 | ch.2 | ch.3 | ch.4 | ch.5 | ch.6 |

|-----|------|------|------|------|------|------|-------|------|------|------|------|------|------|

| L   | Х    | Х    | Х    | Х    | Х    | Х    | OFF   | OFF  | OFF  | OFF  | OFF  | OFF  | OFF  |

| Н   | L    | L    | L    | L    | L    | L    | ON    | OFF  | OFF  | OFF  | OFF  | OFF  | OFF  |

| Н   | Н    | L    | L    | L    | L    | L    | ON    | ON   | OFF  | OFF  | OFF  | OFF  | OFF  |

| Н   | L    | Н    | L    | L    | L    | L    | ON    | OFF  | ON   | OFF  | OFF  | OFF  | OFF  |

| Н   | L    | L    | Н    | L    | L    | L    | ON    | OFF  | OFF  | ON   | OFF  | OFF  | OFF  |

| Н   | L    | L    | L    | Н    | L    | L    | ON    | OFF  | OFF  | OFF  | ON   | OFF  | OFF  |

| Н   | L    | L    | L    | L    | Н    | L    | ON    | OFF  | OFF  | OFF  | OFF  | ON   | OFF  |

| Н   | L    | L    | L    | L    | L    | Н    | ON    | OFF  | OFF  | OFF  | OFF  | OFF  | ON   |

| Н   | Н    | Н    | Н    | Н    | Н    | Н    | ON    | ON   | ON   | ON   | ON   | ON   | ON   |

#### Table 1. ON/OFF setting conditions for each channel

Note that current which is over standby current flows into VCC terminal when the CTL terminal is in "L" level and one of the terminals between CTL1 to CTL6 terminals is set to "H" level. (Refer to the following circuit)

#### **Protection Function**

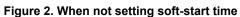

#### Timer-latch short-circuit protection circuit (SCP, SCP Comp.)

The short-circuit detection comparator (SCP) detects the output voltage level of each channel. If the output voltage of any channel is lower than the short-circuit detection voltage, the timer circuit is actuated to start charging to the capacitor (Cscp) externally connected to the CSCP terminal (pin 13).

When the capacitor (Cscp) voltage becomes about 0.7 V, the output transistor is turned off and the dead time is set to 100%.

The short-circuit detection from external input is capable by using -INS terminal (pin 8) on short-circuit detection comparator (SCP Comp.).

When the protection circuit is actuated, the power supply is rebooted or the CTL terminal (pin 1) is set to "L" level, resetting the latch as the voltage at the VREF terminal (pin 9) becomes 1.27 V (Min) or less (Refer to Setting the Time Constant for Timer-Latch Short-Circuit Protection Circuit on page 21).

#### Under voltage lockout protection circuit block (UVLO)

The transient state or a momentary decrease in the power supply voltage, which occurs when the power supply is turned on, may cause the control IC to malfunction, resulting in the breakdown or degradation of the system. To prevent such malfunctions, under voltage lockout protection circuit detects a decrease in internal reference voltage level with respect to the power supply voltage, turns off the output transistor, and sets the dead time to 100% while holding the CSCP terminal (pin 13) at the "L" level.

The system returns to the normal state when the power supply voltage reaches the reference voltage of the under voltage lockout protection circuit.

#### Protection circuit operating function table

The following table shows the output state that the protection circuit is operating.

| Operation circuit                        | OUT1-1 | OUT1-2 | OUT2 | OUT3 | OUT4 | OUT5 | OUT6 |

|------------------------------------------|--------|--------|------|------|------|------|------|

| Short-circuit protection circuit         | Н      | L      | Н    | Н    | Н    | L    | L    |

| Under voltage lockout protection circuit | Н      | L      | Н    | Н    | Н    | Ľ    | L    |

### Setting the Output Voltage

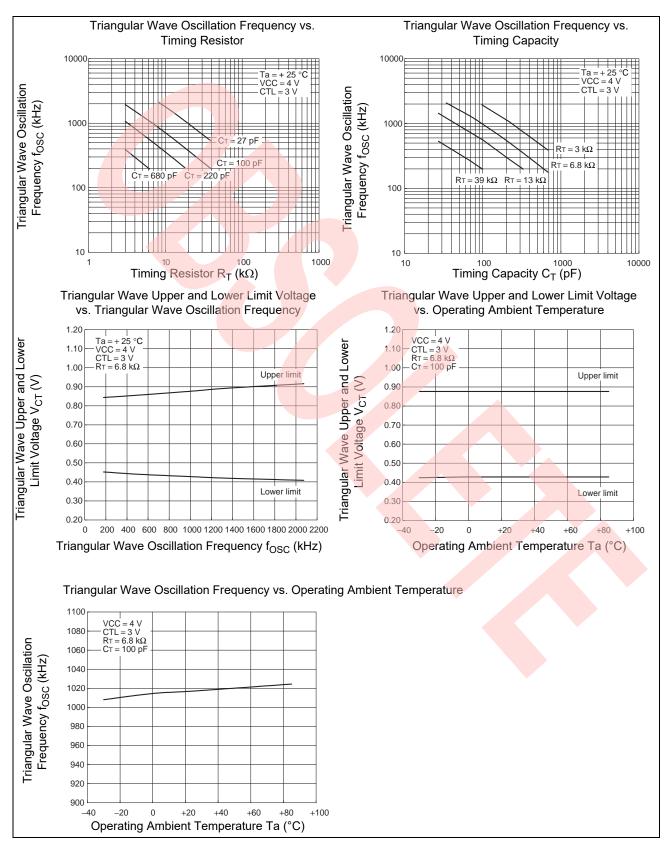

#### Setting the Triangular Wave Oscillation Frequency

The triangular wave oscillation frequency can be set by connecting a timing resistor ( $R_T$ ) to the RT terminal (pin 11) and a timing capacitor ( $C_T$ ) to the CT terminal (pin 12).

Triangular wave oscillation frequency :  $\ensuremath{\mathsf{f}_{\mathsf{OSC}}}$

$$f_{OSC} (kHz) := \frac{680000}{C_T (pF) \times R_T (k\Omega)}$$

#### Setting the Soft-Start Time

To prevent rush currents when the IC is turned on, you can set a soft-start by connecting soft-start capacitors ( $C_{S1}$  to  $C_{S6}$ ) to the CS1 terminal (pin 39) to CS6 terminal (pin 27) respectively.

As illustrated below, when each CTLX is set to "H" from "L", the soft-start capacitors ( $C_{S1}$  to  $C_{S6}$ ) externally connected to the CS1 to CS6 terminals are charged at about 1.1  $\mu$ A.

The error amplifier output (FB1 to FB6) is determined by comparison between the lower voltage of the two non-inverted input terminal voltage (1.23 V (ch.1 : 1.0 V), CS terminal voltage) and the inverted input terminal voltage (-INE1 to -INE6). The FB terminal voltage is decided for the soft-start period (CS terminal voltage < 1.23 V (ch.1 : 1.0 V)) by the comparison between -INE terminal voltage and CS terminal voltage. The DC/DC converter output voltage rises in proportion to the CS terminal voltage as the soft-start capacitor externally connected to the CS terminal is charged. The soft-start time is obtained from the following formula :

Soft-start time : ts (time until output voltage 100%)

ch.1 : ts (s) =

$$0.91 \times C_{S1} (\mu F)$$

ch.2 to ch.6 : ts (s) =  $1.12 \times C_{SX} (\mu F)$

X : Each channel number

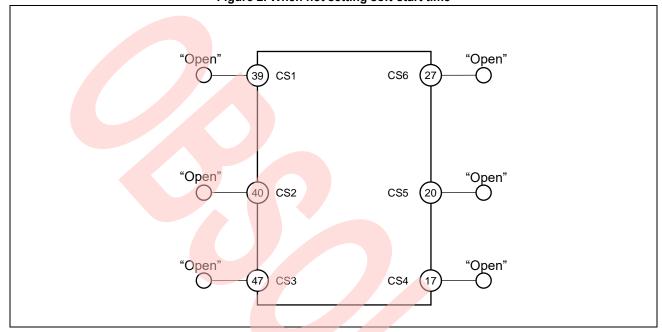

### **Processing When Not Using CS Terminal**

When soft-start function is not used, leave the CS1 terminal (pin 39), the CS2 terminal (pin 40), the CS3 terminal (pin 47), the CS4 terminal (pin 17), the CS5 terminal (pin 20) and the CS6 terminal (pin 27) open.

### Setting the Time Constant for Timer-Latch Short-Circuit Protection Circuit

Each channel uses the short-circuit detection comparator (SCP) to always compare the error amplifier's output level to the reference voltage.

While DC/DC converter load conditions are stable on all channels, the short-circuit detection comparator output remains at "L" level, and the CSCP terminal (pin 13) is held at "L" level.

If the load condition on a channel changes rapidly due to a short-circuit of the load, causing the output voltage to drop, the output of the short-circuit detection comparator on that channel goes to "H" level.

This causes the external short-circuit protection capacitor C<sub>SCP</sub> connected to the CSCP terminal (pin 13) to be charged at 1 µA.

Short-circuit detection time : t<sub>CSCP</sub>

.....  $t_{CSCP}$  (s) := 0.70  $\infty$  C<sub>SCP</sub> ( $\mu$ F)

When the capacitor  $C_{SCP}$  is charged to the threshold voltage ( $V_{TH} = 0.70$  V), the latch is set to and the external FET is turned off (dead time is set to 100%). At this time, the latch input is closed and CSCP terminal (pin 13) is held at "L" level.

The short-circuit detection from external input is capable by using -INS terminal (pin 8). In this case, the short-circuit detection operates when the -INS terminal voltage becomes the level of the threshold voltage ( $V_{TH} = IV$ ) or less.

Note that the latch is reset as the voltage at the VREF terminal (pin 9) is decreased to 1.27 V (Min) or less by either recycling the power supply or setting the CTL terminal (pin 1) to "L" level.

Figure 3. Timer-latch short-circuit protection circuit

### **Processing When Not Using CSCP Terminal**

To disable the timer-latch short-circuit protection circuit, connect the CSCP terminal (pin 13) to GND in the shortest distance.

Figure 4. Processing when not using the CSCP terminal

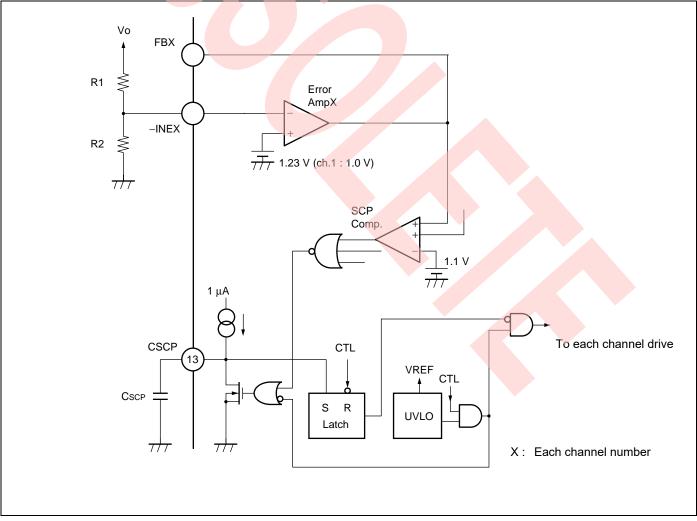

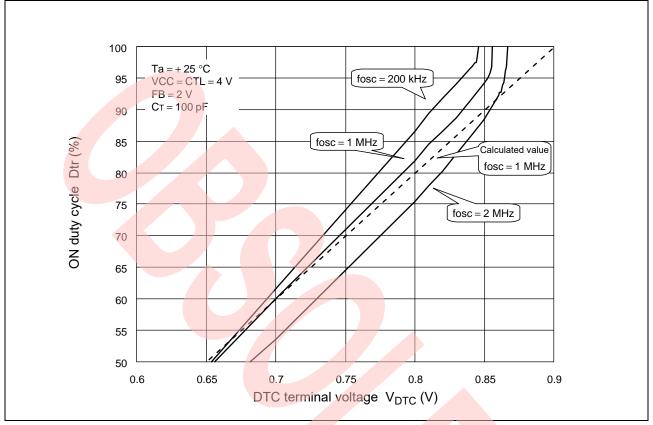

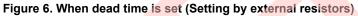

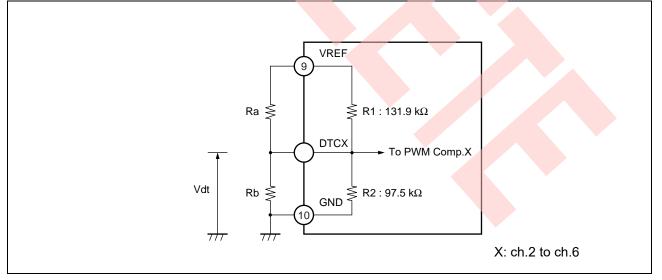

#### Setting the Dead Time (ch.2 to ch.6)

When the device is set for step-up or inverted output based on the step-up, step-up/down Zeta method, step up/down Sepic method, or flyback method, the FB terminal voltage may reach and exceed the triangular wave voltage due to load fluctuation. If this is the case, the output transistor is fixed to a full-ON state (ON duty = 100%). To prevent this, set the maximum duty of the output transistor.

When the DTC terminal is opened, the maximum duty is 92% (Typ) because of this IC built-in resistor which sets the DTC terminal voltage. This is based on the following setting:  $1MHz (R_T = 6.8k\Omega/C_T = 100pF)$ .

To disable the DTC terminal, connect it to the VREF terminal (pin 9) as illustrated below (when dead time is not set).

To change the maximum duty using external resistors, set the DTC terminal voltage by dividing resistance using the VREF voltage. Refer to Figure 6.

It is possible to set without regard for the built-in resistance value (including tolerance) when setting the external resistance value to 1/10 of the built-in resistance or less.

Note that the VREF load current must be set such that the total current for all the channels does not exceed 1 mA.

When the DTC terminal voltage is higher than the triangular wave voltage, the output transistor is turned on. The formula for calculating the maximum duty is as follows, assuming that the triangular wave amplitude and triangular wave lower limit voltage are about 0.5 V and 0.4 V, respectively.

DUTY (ON) Max :=

$$\frac{Vdt - 0.4 V}{0.5 V} \times 100 (\%)$$

$$Vdt = \frac{Rb}{Ra + Rb} \times VREF (V) \text{ (condition : } Ra < \frac{R1}{10}, Rb < \frac{R2}{10}$$

Note: DUTY obtained by the above-mentioned formula is a calculated value. For setting, refer to "ON Duty cycle vs. DTC terminal voltage".

The maximum duty varies depending on the oscillation frequency, regardless of settings in built-in or external resistors.

(This is due to the dependency of the peak value of a triangular wave on the oscillation frequency and  $R_T$ . Therefore, if  $R_T$  is greater, the maximum duty decreases, even when the same frequency is used.)

Furthermore, the maximum duty increases when the power supply voltage and the temperature are high. It is therefore recommended to set the duty, based on the Typical Characteristics on page 11 data, so that it does not exceed 95% under the worst conditions.

Figure 5. ON duty cycle vs. DTC terminal voltage

Setting example (for an aim maximum ON duty of 80% (Vdt = 0.8 V) with Ra = 13.7 k $\Omega$  and Rb = 9.1 k $\Omega$ )

■ Calculation using external resistors Ra and Rb only

$$Vdt = \frac{Rb}{Ra + Rb} \times VREF = 0.80 V$$

$$DUTY (ON) Max = \frac{Vdt - 0.4 V}{V} \times 100 (\%) = 80$$

• Calculation taking account of the built-in resistor (tolerance  $\pm$  20%) also

$$Vdt = \frac{(Rb, R2 \text{ Combined resistance})}{(Ra, R1 \text{ Combined resistance}) + (Rb, R2 \text{ Combined resistance})} \times VREF = 0.80 \text{ V} \pm 0.13\%$$

$$DUTY (ON) \text{ Max} = \frac{Vdt - 0.4 \text{ V}}{0.5 \text{ V}} \times 100 (\%) = 80\% \pm 0.2\% \cdots (2)$$

Based on (1) and (2) above, selecting external resistances to 1/10th or less of the built-in resistance enables the built-in resistance to be ignored.

As for the duty dispersion, please expect  $\pm 5\%$  at (fosc = 1 MHz) due to the dispersion of a triangular wave amplitude.

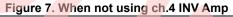

#### Processing When Not Using ch.4 INV AMP

Short-circuit the - INA terminal (pin 19) and OUTA terminal (pin 18) in the shortest distance when not using ch.4 INV Amp.

### **Operation Explanation when CTL Turns ON and OFF**

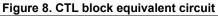

When CTL is turned on, internal reference voltage VR and VREF generate. When VREF exceeds each threshold voltage (VTH) of UVLO (under voltage lockout protection circuit), UVLO is released, and the operation of output drive circuit of each channel becomes possible.

When CTL is off, the CS and CSCP terminals are always set to "L" as soon as output drive circuit of each channel is fixed to full off even if UVLO is released. When VR and VREF fall and VREF decreases the threshold voltage (VRST) of UVLO (under voltage lockout protection circuit), output drive circuit becomes the UVLO state.

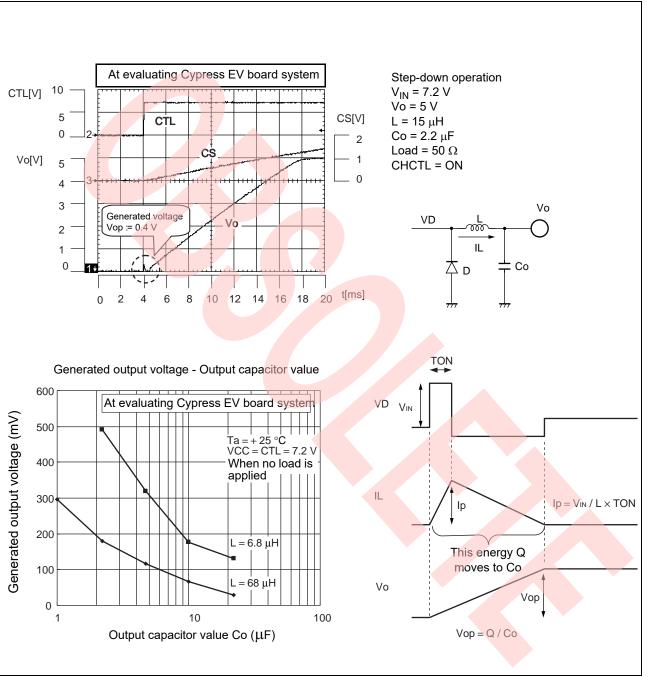

Figure 9. Operation waveform when CTL turning on and off

\*1: As shown in the sequence on the above figure, when turning off CTL while each CHCTL is turned on, intermission state may be generated due to noise around the CTL threshold voltage. To prevent this, it is recommended to turn off CTL with a slope of -1 V/50  $\mu$ s or higher so that the CTL voltage does not remain in the specified threshold voltage range (0.5 V to 1.5 V). If the above slope setting is difficult to achieve, it is recommended to turn off CTL after turning off all CHCTLs.

Moreover, a voltage remains in the FB terminal, when VCC is turned off at the same time as CTL and CHCTL, or when VCC is turned off at the same time as CTL while each CHCTL is still turned on. As this may lead to an overshoot upon restart, it is recommended to turn off V<sub>IN</sub> and CTL after turning off all the CHCTLs to reduce FB to 0 V. Likewise, it is recommended to turn off CHCTL with a slope of -1 V/50  $\mu$ s or higher.

\*2: When CTL and CHCTL are turned on at the same time, or when CTL is turned on while each CHCTL is turned on, there exists a period (approx. 200 ns) when the error Amp output voltage (FB) is higher than the triangular wave voltage (CT) upon the startup of VREF. As a result, when UVLO is released and then the Output Drive circuit of each channel becomes operable, the output transistor is turned on, generating a voltage at the DC/DC converter output.

The voltage to be generated (Vop) depends on L, Co and V<sub>IN</sub>. (See Figure 10) It should be noted that the above event does not occur when CTL is turned on while CHCTL is turned off. Therefore, it is recommended to turn on each CHCTL after turning on CTL.

#### Figure 10. Vo characteristics (Vop) when turning on CTL at CHCTL ON

#### **About Low-Voltage Operation**

1.7 V or more is necessary for the VCC terminal (pin 48) and the VCCO terminal (pin 36) for the self-power supply type to use the step-up circuit as the start voltage.

Even if thereafter  $V_{IN}$  voltage decreases to 1.5 V, operation is possible if the VCC terminal (pin 48) voltage and the VCCO terminal (pin 36) voltage rise to 2.5 V or more after start-up. However, it is necessary not to exceed the maximum duty set value by the duty due to the  $V_{IN}$  decrease. Including other channels, execute an enough operation margin confirmation when using it.

### I/O Equivalent Circuit

### **Usage Precautions**

Printed circuit board ground lines should be set up with consideration for common impedance. Take appropriate static electricity measures.

- Containers for semiconductor materials should have anti-static protection or be made of conductive material.

- After mounting, printed circuit boards should be stored and shipped in conductive bags or containers.

- Work platforms, tools, and instruments should be properly grounded.

- Working personnel should be grounded with resistance of 250 k $\Omega$  to 1 M $\Omega$  between body and ground. Do not apply a negative voltages.

- The use of negative voltages below -0.3 V may create parasitic transistors on LSI lines, which can cause abnormal operation.

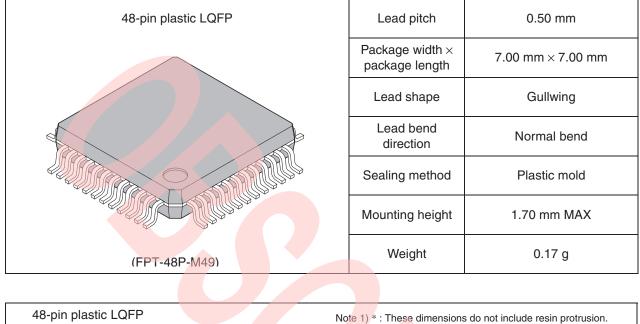

### **Ordering Information**

| Part Number | Package                            |  |

|-------------|------------------------------------|--|

| MB39A123PMT | 48-pin plastic LQFP (FPT-48P- M49) |  |

#### EV Board Ordering Information

| EV Board Part No. | EV Board Version No. | Remarks  |

|-------------------|----------------------|----------|

| MB39A123EVB-02    | Board Rev.1.0        | LQFP-48P |

### **RoHS Compliance information of Pb-free Version**

The Cypress LSI products with "E1" are compliant with the RoHS Directive, and has observed the standard of lead, cadmium, mercury, hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE).

The product that conforms to this standard is added "E1" at the end of the part number.

#### Marking Format (Pb-free Version)

### Labeling Sample (Pb-free Version)

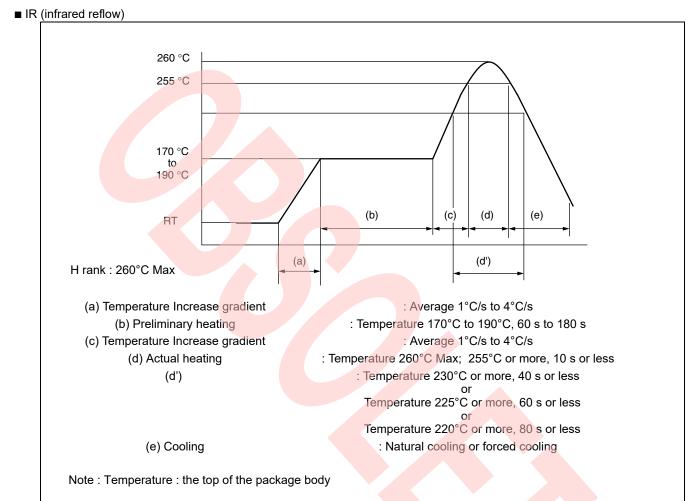

### MB39A123PMT Recommended Conditions of Moisture Sensitivity Level

| ltem               | Condition                                                 |                                                                                                                      |  |

|--------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|

| Mounting Method    | IR (infrared reflow) , warm air reflow                    |                                                                                                                      |  |

| Mounting times     | 2 times                                                   |                                                                                                                      |  |

| Storage period     | Before opening                                            | Please use it within two years after manufacture.                                                                    |  |

|                    | From opening to the second reflow                         | Less than 8 days                                                                                                     |  |

|                    | When the storage period after opening was exceeded        | Please process within 8 days<br>after baking (125°C ± 3°C, 24H+2H/-0H) .<br>Baking can be performed up to two times. |  |

| Storage conditions | 5°C to 30°C, 70%RH or less (the lowest possible humidity) |                                                                                                                      |  |

#### **Mounting Conditions**

■ JEDEC condition : Moisture Sensitivity Level 3 (IPC/JEDEC J-STD-020D)

Manual soldering (partial heating method)

| Item                | Condition                                                                                                  |                                                                                                                                         |  |

|---------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| Storage period      | Before opening                                                                                             | Within two years after manufacture                                                                                                      |  |

|                     | Between opening and mounting                                                                               | Within two years after manufacture<br>(No need to control moisture during the storage period<br>because of the partial heating method.) |  |

| Storage conditions  | 5°C to 30 °C, 70% RH or less (the lowest possible humidity)                                                |                                                                                                                                         |  |

| Mounting conditions | Temperature at the tip of a soldering iron: 400 °C Max<br>Time: Five seconds or below per pin <sup>3</sup> |                                                                                                                                         |  |

Note3. Make sure that the tip of a soldering iron does not come in contact with the package body.

### **Package Dimensions**

### **Document History Page**

#### Document Title: MB39A123 6 ch DC/DC Converter IC with Synchronous Rectification Datasheet Document Number: 002-08367

| Documer  | Document Number: 002-00307 |                    |                           |                                                                                                       |

|----------|----------------------------|--------------------|---------------------------|-------------------------------------------------------------------------------------------------------|

| Revision | ECN                        | Orig. of<br>Change | Submission<br>Date        | Description of Change                                                                                 |

| **       | -                          | TAOA               | 04/12/2012                | Migrated to Cypress and assigned document number 002-08367. No change to document contents or format. |

| *A       | 5544035                    | TAOA               | 1 <mark>2/14/2</mark> 016 | Migrated to Cypress datasheet template                                                                |

| *В       | 5798770                    | MASG               | 07/05/2017                | Adapted Cypress new logo.                                                                             |

| *C       | 645 <mark>5209</mark>      | ATTS               | 01/22/2019                | Obsoleted                                                                                             |

#### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless/RF                                           | cypress.com/wireless   |

|                                                       |                        |

#### PSoC<sup>®</sup> Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2006-2019. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and other sont, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or systems, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.