# S6AE102A / S6AE103A

**Energy Harvesting PMIC for Wireless Sensor Node**

Data Sheet (Preliminary)

**Notice to Readers:** This document states the current technical specifications regarding the Cypress product(s) described herein. The Preliminary status of this document indicates that product qualification has been completed, and that initial production has begun. Due to the phases of the manufacturing process that require maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications.

### Notice On Data Sheet Designations

Cypress Semiconductor Corp. issues data sheets with Advance Information or Preliminary designations to advise readers of product information or intended specifications throughout the product life cycle, including development, qualification, initial production, and full production. In all cases, however, readers are encouraged to verify that they have the latest information before finalizing their design. The following descriptions of Cypress data sheet designations are presented here to highlight their presence and definitions.

#### **Advance Information**

The Advance Information designation indicates that Cypress Semiconductor Corp. is developing one or more specific products, but has not committed any design to production. Information presented in a document with this designation is likely to change, and in some cases, development on the product may discontinue. Cypress Semiconductor Corp. therefore places the following conditions upon Advance Information content:

"This document contains information on one or more products under development at Cypress Semiconductor Corp. The information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Cypress Semiconductor Corp. reserves the right to change or discontinue work on this proposed product without notice."

#### Preliminary

The Preliminary designation indicates that the product development has progressed such that a commitment to production has taken place. This designation covers several aspects of the product life cycle, including product qualification, initial production, and the subsequent phases in the manufacturing process that occur before full production is achieved. Changes to the technical specifications presented in a Preliminary document should be expected while keeping these aspects of production under consideration. Cypress places the following conditions upon Preliminary content:

"This document states the current technical specifications regarding the Cypress product(s) described herein. The Preliminary status of this document indicates that product qualification has been completed, and that initial production has begun. Due to the phases of the manufacturing process that require maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications."

#### Combination

Some data sheets contain a combination of products with different designations (Advance Information, Preliminary, or Full Production). This type of document distinguishes these products and their designations wherever necessary, typically on the first page, the ordering information page, and pages with the DC Characteristics table and the AC Erase and Program table (in the table notes). The disclaimer on the first page refers the reader to the notice on this page.

#### **Full Production (No Designation on Document)**

When a product has been in production for a period of time such that no changes or only nominal changes are expected, the Preliminary designation is removed from the data sheet. Nominal changes may include those affecting the number of ordering part numbers available, such as the addition or deletion of a speed option, temperature range, package type, or VIO range. Changes may also include those needed to clarify a description or to correct a typographical error or incorrect specification. Cypress Semiconductor Corp. applies the following conditions to documents in this category:

"This document states the current technical specifications regarding the Cypress product(s) described herein. Cypress Semiconductor Corp. deems the products to have been in sufficient production volume such that subsequent versions of this document are not expected to change. However, typographical or specification corrections, or modifications to the valid combinations offered may occur."

Questions regarding these document designations may be directed to your local sales office.

# S6AE102A / S6AE103A

**Energy Harvesting PMIC for Wireless Sensor Node**

Data Sheet (Preliminary)

### 1. Description

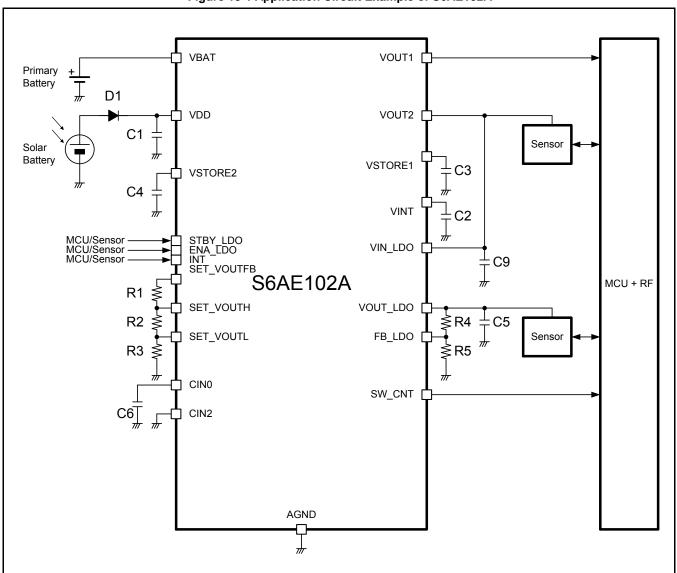

The S6AE102A/103A is a power management IC (PMIC) for energy harvesting that is built into circuits of solar cells connected in series, dual output power control circuits, output capacitor storage circuits, power switching circuits of primary batteries, a LDO, a comparator and timers. Super-low-power operation is possible using a consumption current of only 280 nA and startup power of only 1.2  $\mu$ W. As a result, even slight amounts of power generation can be obtained from compact solar cells under low-brightness environments of approximately 100 lx.

This IC stores power generated by solar cells to an output capacitor using built-in switch control, and it turns on the power switching circuit while the capacitor voltage is within a preset maximum and minimum range for supplying energy to a load. The output power control circuit has 2 outputs, and 1 of 2 outputs can control On and OFF of the power gating circuit using interrupt signal. The output capacitor storage circuits have 2 capacitor connection circuit for a storage of system load and a storage of surplus power, and if the power generated from solar cells is enough, the power is stored to the capacitor of surplus power storage. If the power generated from solar cells is not enough, energy can also be supplied in the same way as solar cells from the capacitor of surplus power.

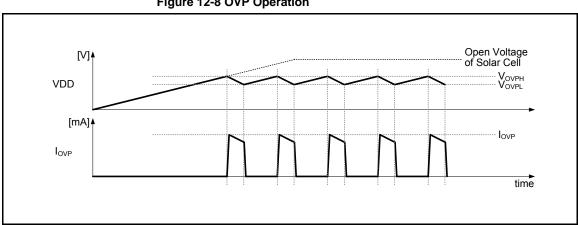

This IC has also an independent LDO. The LDO can provide stable voltage that a sensor requires. And also an independent comparator which can make voltage comparison signal output a lot of flexibility is built in. Also, an overvoltage protection (OVP) function is built into the input pins of the solar cells, and the open voltage of solar cells is used by this IC to prevent an overvoltage state.

The S6AE102A/103A is provided as a battery-free wireless sensor node solution that is operable by super-compact solar cells or non-disconnect energy harvesting based wireless sensor node solution with the capacitor of surplus storage or primary batteries for auxiliary power

This document states the current technical specifications regarding the Cypress product(s) described herein. The Preliminary status of this document indicates that product qualification has been completed, and that initial production has begun. Due to the phases of the manufacturing process that require maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications.

: 280 nA

#### **Features** 2.

| Operation input voltage range        |       |

|--------------------------------------|-------|

| <ul> <li>Solar cell power</li> </ul> | : 2.0 |

- : 2.0V to 5.5 V - Primary battery power : 2.0V to 5.5 V

- Adjustable output voltage range : 1.1V to 5.2V

- Low-consumption current

- Minimum input power at startup

- : 1.2 µW ■ Low-consumption current LDO : 400 nA

- Low-consumption current Timer : 30 nA

- Low-consumption current comparator : 20 nA (S6AE103A only)

- Hybrid control of solar cell and primary battery with power path control

- Solar powered power control without battery

- System power reduction control with power gating

- Power gating control with interrupt signal

- Power gating control with timer (S6AE103A only)

- Hybrid storage system for a storage of system load and a storage of surplus power

: 5.4V

- Power supply and switch control signal output for external path switch control

- Input overvoltage protection

- Compact QFN-20/QFN-24 package : 4 mm × 4 mm

#### **Applications** 3.

- Energy harvesting power system with a very small solar cell

- Bluetooth Smart<sup>®</sup> sensor

- Wireless HVAC sensor

- Wireless lighting control

- Security system

- Smart home / Building / Industrial wireless sensor

## **Table of Contents**

| 1.  | Descr  | iption                                | 3    |

|-----|--------|---------------------------------------|------|

| 2.  | Featu  | res                                   | 4    |

| 3.  | Applic | cations                               | 4    |

| 4.  | Produ  | ict Lineup                            | 7    |

| 5.  | Packa  | ages                                  | 7    |

| 6.  | Pin As | ssignment                             | 8    |

| 7.  | Pin D  | escriptions                           | 9    |

| 8.  | Block  | Diagram                               | . 10 |

| 9.  | Absol  | ute Maximum Ratings                   | . 12 |

| 10. | Recor  | mmended Operating Conditions          | . 13 |

| 11. | Electr | ical Characteristics                  | . 14 |

| 12. | Funct  | ional Description                     | . 17 |

|     | 12.1   | Power Supply Control                  | . 17 |

|     | 12.2   | Power Gating                          | . 28 |

|     | 12.3   | Discharge                             | . 33 |

|     | 12.4   | SW_CNT Control                        | . 33 |

|     | 12.5   | General-Purpose Comparator            | . 33 |

|     | 12.6   | LDO                                   | . 34 |

|     | 12.7   | Over Voltage Protection (OVP Block)   | . 34 |

| 13. | Applic | cation Circuit Example and Parts list | . 35 |

| 14. | Applic | cation Note                           | . 38 |

|     | 14.1   | Setting the Operation Conditions      | . 38 |

| 15. | Usage  | e Precaution                          | . 40 |

| 16. | RoHS   | Compliance Information                | . 40 |

| 17. | Order  | ing Information                       | . 40 |

| 18. | Packa  | age Dimensions                        | . 41 |

| 19. | Major  | Changes                               | . 43 |

# Figures

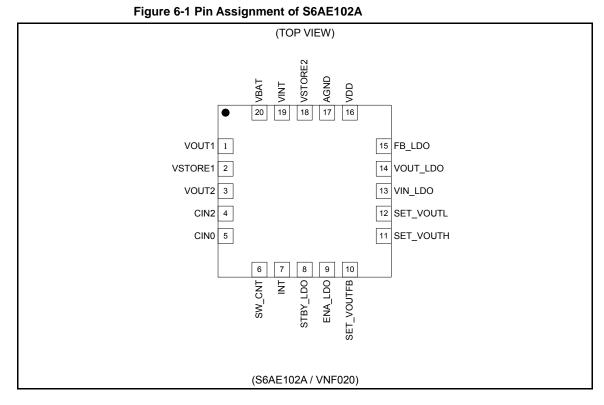

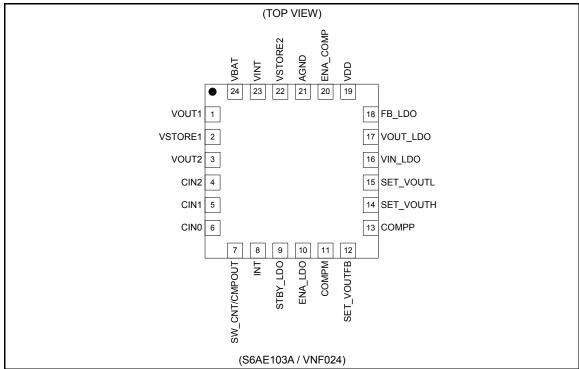

| Figure 6-1 Pin Assignment of S6AE102A                 | 8  |

|-------------------------------------------------------|----|

| Figure 6-2 Pin Assignment of S6AE103A                 | 8  |

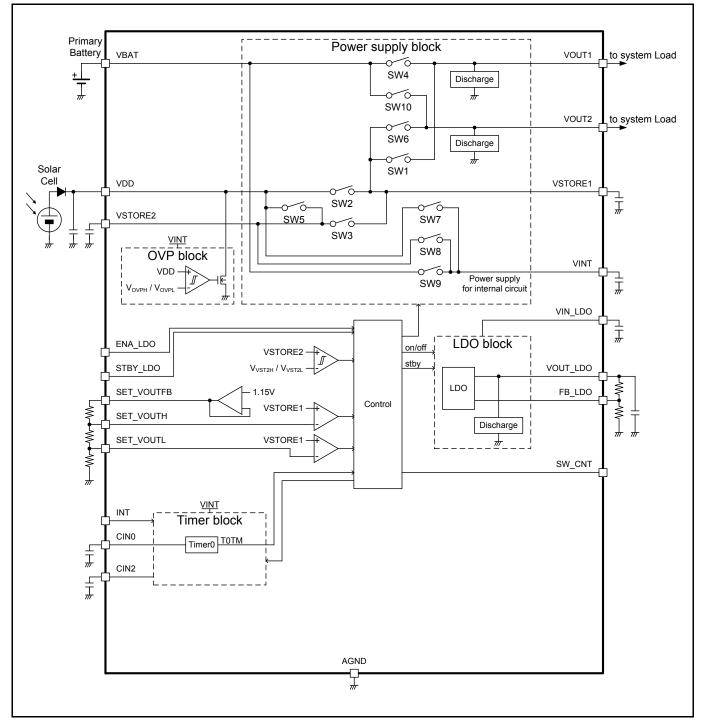

| Figure 8-1 Block Diagram of S6AE102A                  | 10 |

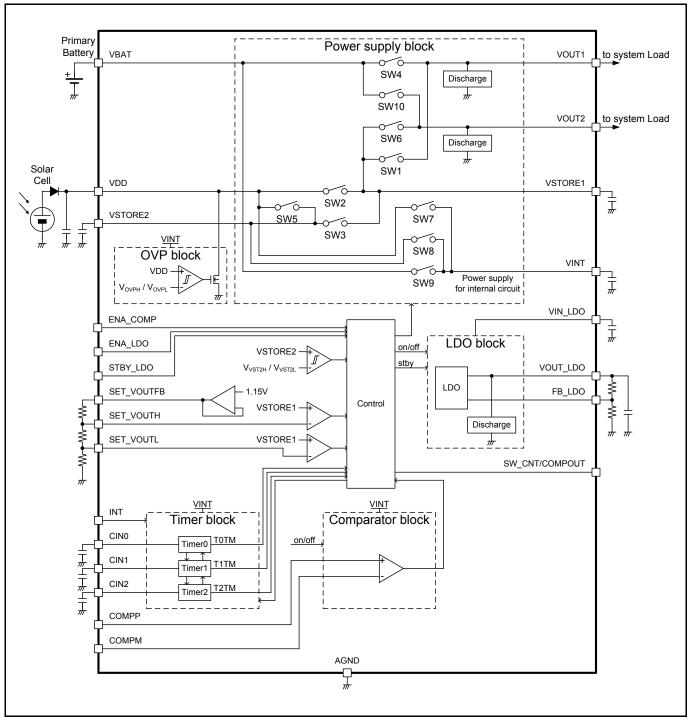

| Figure 8-2 Block Diagram of S6AE103A                  |    |

| Figure 12-1 VDD Input Power Operation                 | 19 |

| Figure 12-2 VBAT Input Power Operation                | 21 |

| Figure 12-3 VDD/VBAT Input Power Operation            | 23 |

| Figure 12-4 VDD/VSTORE2 Input Power Operation         | 25 |

| Figure 12-5 VSTORE2 Input Power Operation             |    |

| Figure 12-6 Power Gating Operation (VDD Input Power)  |    |

| Figure 12-7 Power Gating Operation (VBAT Input Power) |    |

| Figure 12-8 OVP Operation                             |    |

| Figure 13-1 Application Circuit Example of S6AE102A   |    |

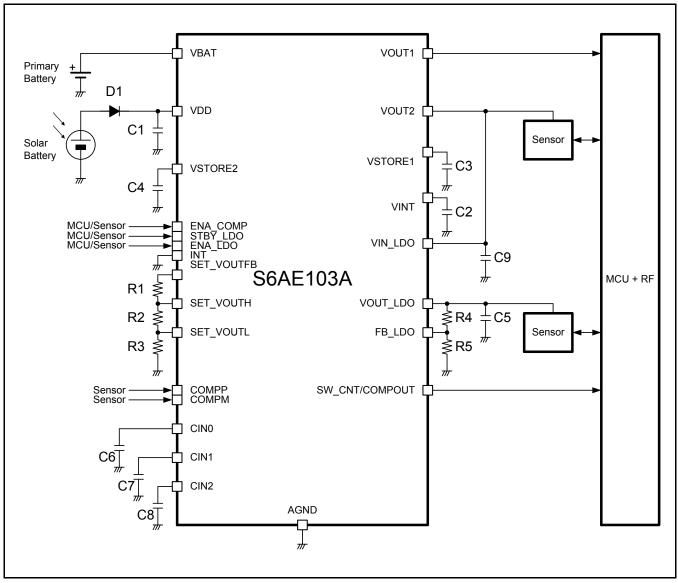

| Figure 13-2 Application Circuit Example of S6AE103A   |    |

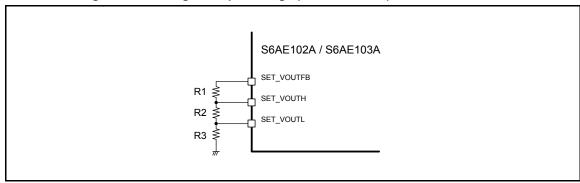

| Figure 14-1 Setting of Output Voltage (VOUT1, VOUT2)  |    |

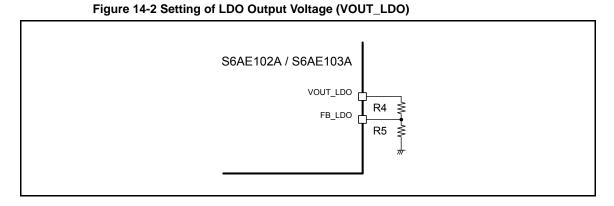

| Figure 14-2 Setting of LDO Output Voltage (VOUT_LDO)  |    |

| Figure 18-1 Package Dimensions of S6AE102A (VNF020)   |    |

| Figure 18-2 Package Dimensions of S6AE103A (VNF024)   | 42 |

## Tables

| Table 7-1 Pin Descriptions                                  | 9  |

|-------------------------------------------------------------|----|

| Table 11-1 Electrical Characteristics (System Overall)      | 14 |

| Table 11-2 Electrical Characteristics (Consumption Current) | 15 |

| Table 11-3 Electrical Characteristics (Switch)              | 15 |

| Table 11-4 Electrical Characteristics (LDO)                 | 16 |

| Table 11-5 Electrical Characteristics (Timer)               | 16 |

| Table 12-1 VINT Pin Voltage                                 | 17 |

| Table 12-2 Power Gating Operation Mode                      | 28 |

| Table 12-3 General-Purpose Comparator Operation             | 33 |

| Table 12-4 LDO Operation Mode                               | 34 |

| Table 13-1 Parts List                                       | 37 |

### 4. Product Lineup

#### Function

| Product Name                 | S6AE102A     | S6AE103A |  |  |  |

|------------------------------|--------------|----------|--|--|--|

| Pin count                    | 20           | 24       |  |  |  |

| Power supply voltage range   | 2.0V to      | 5.5 V    |  |  |  |

| Output voltage range         | 1.1V to 5.2V |          |  |  |  |

| Output channel               | 20           | ch       |  |  |  |

| LDO                          | 10           | ch       |  |  |  |

| Overvoltage protection (OVP) | VDD          | ) pin    |  |  |  |

| Timer                        | 1unit        | 3units   |  |  |  |

| Comparator                   | _            | 1ch      |  |  |  |

### 5. Packages

| Product Name<br>Package | S6AE102A | S6AE103A |

|-------------------------|----------|----------|

| VNF020                  | 0        | -        |

| VNF024                  | -        | 0        |

$\circ$ : Available

#### Note:

- See "18. Package Dimensions" for detailed information on each package.

### 6. Pin Assignment

Figure 6-2 Pin Assignment of S6AE103A

## 7. Pin Descriptions

| Pin No.              |            | Dia Nama       | I/O                    | Description                                                            |  |                                                 |

|----------------------|------------|----------------|------------------------|------------------------------------------------------------------------|--|-------------------------------------------------|

| S6AE102A             | S6AE103A   | Pin Name       |                        |                                                                        |  |                                                 |

| 1                    | 1          | VOUT1          | 0                      | Output voltage pin                                                     |  |                                                 |

| 2                    | 2          | VSTORE1        | 0                      | Storage output pin                                                     |  |                                                 |

| 3 3 VOUT2            |            |                | 0                      | Output voltage pin                                                     |  |                                                 |

| 4 4 CIN2<br>- 5 CIN1 |            | 01110          | _                      | Timer time 2 (T2) setting pin(for connecting capacitor)                |  |                                                 |

|                      |            | CIN2           | 0                      | For the pin setting, refer to "Table 12-2 Power Gating Operation Mode" |  |                                                 |

|                      | -          | 01114          | 0                      | Timer time 1 (T1) setting pin(for connecting capacitor)                |  |                                                 |

|                      |            | CINT           | 0                      | For the pin setting, refer to "Table 12-2 Power Gating Operation Mode" |  |                                                 |

| 5 6                  |            | CINO           | 0                      | Timer time 0 (T0) setting pin(for connecting capacitor)                |  |                                                 |

|                      |            | CIN0           | 0                      | For the pin setting, refer to "Table 12-2 Power Gating Operation Mode  |  |                                                 |

| -                    | 7          | SW_CNT/COMPOUT | 0                      | VOUT1 switch interlocking output pin / Comparator output pin           |  |                                                 |

| 6                    | -          | SW_CNT         | 0                      | VOUT1 switch interlocking output pin                                   |  |                                                 |

|                      |            |                |                        | Event driven mode control pin                                          |  |                                                 |

| 7 8                  |            | INT            | I.                     | For the pin setting, refer to "Table 12-2 Power Gating Operation Mode" |  |                                                 |

|                      |            |                |                        | (when being not used, connect this pin to AGND )                       |  |                                                 |

|                      |            |                |                        | LDO operation mode setting pin                                         |  |                                                 |

| 8                    | 9          | STBY_LDO       | I.                     | For the pin setting, refer to "Table 12-4 LDO Operation Mode"          |  |                                                 |

|                      |            |                |                        | (when being not used, connect this pin to AGND )                       |  |                                                 |

|                      |            |                |                        |                                                                        |  | LDO output control pin                          |

| 9                    | 10         | ENA_LDO        | I                      | For the pin setting, refer to "Table 12-4 LDO Operation Mode"          |  |                                                 |

|                      |            |                |                        |                                                                        |  |                                                 |

|                      | - 11 COMPM |                |                        | Comparator Input pin                                                   |  |                                                 |

| -                    | 11         | СОМРМ          |                        | (when being not used, leave this pin open)                             |  |                                                 |

| 10                   | 12         | SET_VOUTFB     | 0                      | Reference voltage output pin (for connecting resistor)                 |  |                                                 |

|                      |            | 001155         |                        | Comparator input pin                                                   |  |                                                 |

|                      |            | COMPP          | I                      | (when being not used, leave this pin open )                            |  |                                                 |

| 11                   | 14         | SET_VOUTH      | I                      | VOUT1, VOUT2 output voltage setting pin (for connecting resistor)      |  |                                                 |

| 12                   | 15         | SET_VOUTL      | I                      | VOUT1, VOUT2 output voltage setting pin (for connecting resistor)      |  |                                                 |

| 10                   |            |                |                        | LDO power input pin                                                    |  |                                                 |

| 13                   | 16         | VIN_LDO        |                        | (when being not used, connect this pin to AGND)                        |  |                                                 |

| 14                   | 17         | VOUT_LDO       | 0                      | LDO output pin                                                         |  |                                                 |

|                      |            |                |                        | LDO output voltage setting pin (for connecting resistor)               |  |                                                 |

| 15                   | 18         | FB_LDO         |                        | (when being not used, leave this pin open )                            |  |                                                 |

|                      |            |                |                        | Solar cell input pin                                                   |  |                                                 |

| 16                   | 19         | VDD            | I                      | (when being not used, leave this pin open )                            |  |                                                 |

|                      |            |                | Comparator control pin |                                                                        |  |                                                 |

| -                    | 20         | ENA_COMP       | I                      | For the pin setting, refer to "12.5 General-Purpose Comparator"        |  |                                                 |

|                      |            |                |                        |                                                                        |  | (when being not used, connect this pin to AGND) |

| 17                   | 21         | AGND           | -                      | Ground pin                                                             |  |                                                 |

| 18                   | 22         | VSTORE2        | 0                      | Storage output pin                                                     |  |                                                 |

| 19                   | 23         | VINT           | 0                      | Internal circuit storage output pin                                    |  |                                                 |

|                      |            |                |                        | Primary battery input pin                                              |  |                                                 |

| 20                   | 24         | VBAT           | I                      | (when being not used, leave this pin open )                            |  |                                                 |

#### Table 7-1 Pin Descriptions

### 8. Block Diagram

#### Figure 8-1 Block Diagram of S6AE102A

#### Figure 8-2 Block Diagram of S6AE103A

### 9. Absolute Maximum Ratings

| Parameter                                                                              | Symbol Condition |                                                                                   | Ra   | l lmit    |       |

|----------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------|------|-----------|-------|

| Parameter                                                                              |                  |                                                                                   | Min  | Max       | Unit  |

| Power supply voltage (*1)                                                              | V <sub>MAX</sub> | VDD, VBAT, VIN_LDO pin                                                            | -0.3 | +6.9      | V     |

| Signal input voltage (*1)                                                              | Vinputmax        | SET_VOUTH, SET_VOUTL, INT,<br>ENA_LDO, STBY_LDO,<br>ENA_COMP,<br>COMPP, COMPM pin | -0.3 | +6.9      | V     |

| VDD slew rate         V <sub>SLOPE</sub> Power dissipation (*1)         P <sub>D</sub> |                  | VDD pin                                                                           | -    | 0.1       | mV/µs |

|                                                                                        |                  | Ta ≤+ 25°C                                                                        | -    | 1400 (*2) | mW    |

| Storage temperature                                                                    | T <sub>STG</sub> | T <sub>STG</sub> –                                                                |      | +125      | °C    |

\*1: When AGND = 0V

\*2: θja (wind speed 0m/s): +50°C/W

#### Warning:

1. Semiconductor devices may be permanently damaged by application of stress (including, without limitation, voltage, current or temperature) in excess of absolute maximum ratings. Do not exceed any of these ratings.

### 10. Recommended Operating Conditions

| Demonster                                | 0                   | O an ditian          |      | Value |                                  | 11   |

|------------------------------------------|---------------------|----------------------|------|-------|----------------------------------|------|

| Parameter                                | Symbol              | Condition            | Min  | Тур   | Max                              | Unit |

| Power supply voltage 1 (*1)              | $V_{VDD}$           | VDD pin              | 2.0  | 3.3   | 5.5                              | V    |

| Power supply voltage 2 (*1)              | $V_{\text{VBAT}}$   | VBAT pin             | 2.0  | 3.0   | 5.5                              | V    |

| Power supply voltage 3 (*1)              | V <sub>VINLDO</sub> | VIN_LDO pin          | 2.0  | -     | 5.3                              | V    |

|                                          |                     | INT, ENA_LDO,        |      |       |                                  |      |

|                                          |                     | STBY_LDO,            |      |       | VINT pin                         |      |

| Signal input voltage (*1)                | VINPUT              | ENA_COMP,            | -    | -     | voltage                          | V    |

|                                          |                     | COMPP, COMPM         |      |       | (*2)                             |      |

|                                          |                     | pin                  |      |       |                                  |      |

| VOUT1 setting resistance                 | R <sub>VOUT</sub>   | Sum of R1, R2, R3    | 10   | -     | -                                | MΩ   |

| LDO setting resistance                   | R <sub>LDO</sub>    | Sum of R4, R5        | 100  | -     | -                                | MΩ   |

| VDD capacitance                          | $C_{\text{VDD}}$    | VDD pin              | 10   |       |                                  | μF   |

| VINT capacitance                         | CVINT               | VINT pin             | 1    | -     | -                                | μF   |

| VOUT upper limit setting voltage         | V <sub>SYSH</sub>   | VSTORE1 pin          | 1.25 | -     | - 5.2                            |      |

| VOUT lower limit setting voltage         | V <sub>SYSL</sub>   | VSTORE1 pin          | 1.1  | -     | V <sub>SYSH</sub><br>×0.9        | v    |

| General-purpose comparator input voltage | V <sub>COMP</sub>   | COMPP,<br>COMPM pins | 0.2  | -     | VINT pin<br>voltage -1.5<br>(*2) | v    |

| LDO output setting voltage               | $V_{\text{SETLD}}$  | VOUT_LDO pin         | 1.3  | -     | 5.0                              | V    |

| Timer time 0                             | Т0                  | CIN0 pin, Timer 0    | 0.1  | -     | 3600                             | s    |

| Timer time 1                             | T1                  | CIN1 pin, Timer 1    | 0.1  | -     | 3600                             | s    |

| Timer time 2                             | T2                  | CIN2 pin, Timer 2    | 0.1  | -     | 3600                             | s    |

| Operating ambient temperature            | Та                  | -                    | -40  | -     | +85                              | °C   |

\*1: When AGND = 0V

\*2: Refer to "Table 12-1 VINT Pin Voltage".

#### Warning:

- 1. The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated under these conditions.

- 2. Any use of semiconductor devices will be under their recommended operating condition.

- 3. Operation under any conditions other than these conditions may adversely affect reliability of device and could result in device failure.

- 4. No warranty is made with respect to any use, operating conditions or combinations not represented on this data sheet. If you are considering application under any conditions other than listed herein, please contact sales representatives beforehand.

### **11. Electrical Characteristics**

The following electrical characteristics are the values excluding the effect of external resistors and external capacitors.

#### Table 11-1 Electrical Characteristics (System Overall)

(Unless specified otherwise, these are the electrical characteristics under the recommended operating environment.)

| Denerration                                    | Ourseline J          | Com d'iller                                                                                                                                            |                                 | Value                       |                                 | 11   |

|------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------|---------------------------------|------|

| Parameter                                      | Symbol               | Condition                                                                                                                                              | Min                             | Тур                         | Max                             | Unit |

| Minimum Input power<br>in start-up             | W <sub>START</sub>   | VDD pin, Ta = +25°C, $V_{VOUTH}$ setting = 3V,<br>By applying 0.4 $\mu$ A to VDD, when VOUT1<br>reaches 3V×95% after the point when VDD<br>reaches 3V. | -                               | -                           | 1.2                             | μW   |

| Power detection voltage                        | V <sub>DETH</sub>    |                                                                                                                                                        | 1.30                            | 1.55                        | 2.00                            | V    |

| Power undetection voltage                      | V <sub>DETL</sub>    | VDD, VBAT ,VINT, VSTORE2 pins                                                                                                                          | 1.15                            | 1.45                        | 1.90                            | V    |

| Power detection hysteresis                     | VDETHYS              |                                                                                                                                                        | -                               | 0.1                         | -                               | V    |

| Power detection voltage 2                      | V <sub>DETH2</sub>   | VDD pin,                                                                                                                                               | 2.0                             | 2.1                         | 2.2                             | V    |

| Power undetection voltage 2                    | V <sub>DETL2</sub>   | When connecting a capacitor to VSTORE2                                                                                                                 | 1.9                             | 2.0                         | 2.1                             | V    |

| Power detection hysteresis 2                   | V <sub>DETHYS2</sub> | pin                                                                                                                                                    | _                               | 0.1                         | -                               | V    |

| VOUT upper limit voltage V <sub>VOUTH</sub>    |                      | VSTORE1 pin,<br>VOUT1 Load = 0 mA, VOUT2 Load = 0 mA                                                                                                   | -                               | V <sub>SYSH</sub>           | -                               | V    |

| Input power reconnect voltage                  | V <sub>VOUTM</sub>   | VSTORE1 pin,<br>VOUT1 Load = 0 mA, VOUT2 Load = 0 mA                                                                                                   | -                               | V <sub>voutн</sub><br>×0.95 | -                               | V    |

| VOUT lower limit voltage                       | V <sub>VOUTL</sub>   | VSTORE1 pin,<br>VOUT1 Load = 0 mA, VOUT2 Load = 0 mA                                                                                                   | -                               | V <sub>SYSL</sub>           | -                               | v    |

|                                                |                      | VSTORE2 pin, V <sub>VOUTH</sub> setting>2.4V                                                                                                           | -                               | V <sub>VOUTH</sub>          | -                               | V    |

| VSTORET2 upper limit voltage V <sub>VS</sub>   |                      | VSTORE2 pin, V <sub>VOUTH</sub> setting≤2.4V                                                                                                           | 2.3                             | 2.4                         | 2.5                             | V    |

|                                                |                      | VSTORE2 pin, V <sub>VOUTH</sub> setting>2.4V                                                                                                           | -                               | V <sub>VOUTL</sub>          | -                               | V    |

| STORET2 lower limit voltage V <sub>VST2L</sub> |                      | VSTORE2 pin, V <sub>VOUTH</sub> setting≤2.4V                                                                                                           | 2.2                             | 2.3                         | 2.4                             | V    |

| OVP detection voltage                          | V <sub>OVPH</sub>    |                                                                                                                                                        | 5.2                             | 5.4                         | 5.5                             | V    |

| OVP release voltage                            | V <sub>OVPL</sub>    | VDD pin                                                                                                                                                | 5.1                             | 5.3                         | 5.4                             | V    |

| OVP detection hysteresis                       | VOVPHYS              |                                                                                                                                                        | -                               | 0.1                         | -                               | V    |

| OVP protection current                         | I <sub>OVP</sub>     | VDD pin input current                                                                                                                                  | 6                               | -                           | -                               | mA   |

|                                                | V <sub>IH</sub>      | INT, ENA_LDO, STBY_LDO, ENA_COMP pins                                                                                                                  | 1.1                             | -                           | VINT pin<br>voltage (*1)        | V    |

| Input voltage                                  | V <sub>IL</sub>      | INT, ENA_LDO, STBY_LDO, ENA_COMP pins                                                                                                                  | 0                               | _                           | 0.3                             | V    |

|                                                | V <sub>OH</sub>      | SW_CNT/COMPOUT, SW_CNT pins,<br>Load = 2 μA                                                                                                            | 0.7×VINT<br>pin voltage<br>(*1) | -                           | VINT pin<br>voltage (*1)        | v    |

| Output voltage                                 | V <sub>OL</sub>      | SW_CNT/COMPOUT, SW_CNT pins,<br>Load = 2 μA                                                                                                            | 0                               | -                           | 0.3×VINT<br>pin voltage<br>(*1) | v    |

\*1: Refer to "Table 12-1 VINT Pin Voltage".

#### Table 11-2 Electrical Characteristics (Consumption Current)

(Unless specified otherwise, these are the electrical characteristics under the recommended operating environment.)

| Parameter             | Sympol            | Condition                                                                                                                                                                                                            |     | Unit |      |      |

|-----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| Parameter             | Symbol            | Condition                                                                                                                                                                                                            | Min | Тур  | Max  | Unit |

| Consumption current 1 | I <sub>QIN1</sub> | $ENA_LDO = GND, STBY_LDO = GND,$ $V_{VOUTH} setting = 1.25V, Ta = +25^{\circ}C,$ $SET_VOUTFB resistance>100 M\Omega,$ $VOUT1 Load = 0 mA, VOUT2 Load = 0 mA$ $Sum of I_{QIN1} and I_{INLD2} (LDO operation current)$ |     | 280  | 420  | nA   |

| Consumption current 2 | I <sub>QIN2</sub> | Sum of I <sub>QIN1</sub> and I <sub>INLD2</sub> (LDO operation current)<br>ENA_LDO = VINT (*1)                                                                                                                       | -   | 680  | 1020 | nA   |

| Consumption current 3 | I <sub>QIN3</sub> | Sum of I <sub>QIN1</sub> and comparator operation current,                                                                                                                                                           |     | 300  | 450  | nA   |

\*1: Refer to "Table 12-1 VINT Pin Voltage".

\*2: Refer to "12.2 Power Gating"

#### Table 11-3 Electrical Characteristics (Switch)

#### VDD ≥ 3V, VBAT ≥ 3V, VINT ≥ 3V, VSTORE2 ≥ 3V, V<sub>VOUTL</sub> ≥ 3V, VSTORE1 ≥ V<sub>VOUTL</sub>

(Unless specified otherwise, these are the electrical characteristics under the recommended operating environment.)

| Parameter            | Cumula al         | Condition                                         |     | Value |     |      |

|----------------------|-------------------|---------------------------------------------------|-----|-------|-----|------|

| Parameter            | Symbol            | Condition                                         | Min | Тур   | Max | Unit |

| Switch resistance 1  | R <sub>ON1</sub>  | SW1, In connection of VSTORE1 pin and VOUT1 pin   | -   | 1.5   | 2.5 | Ω    |

| Switch resistance 2  | R <sub>ON2</sub>  | SW2, In connection of VDD pin and VSTORE1 pin     | -   | 50    | 100 | Ω    |

| Switch resistance 3  | R <sub>ON3</sub>  | SW3, In connection of VSTORE2 pin and VSTORE1 pin | -   | 50    | 100 | Ω    |

| Switch resistance 4  | R <sub>ON4</sub>  | SW4, In connection of VBAT pin and VOUT1 pin      | -   | 1.5   | 2.5 | Ω    |

| Switch resistance 5  | R <sub>ON5</sub>  | SW5, In connection of VDD pin and VSTORE2 pin     | -   | 50    | 100 | Ω    |

| Switch resistance 6  | R <sub>ON6</sub>  | SW6, In connection of VSTORE1 pin and VOUT2 pin   | -   | 1.5   | 2.5 | Ω    |

| Switch resistance 10 | R <sub>ON10</sub> | SW10, In connection of VBAT pin and VOUT2 pin     | -   | 1.5   | 2.5 | Ω    |

| Discharge resistance | R <sub>DIS</sub>  | VOUT1, VOUT2 pins                                 | -   | 1     | 2   | kΩ   |

#### Table 11-4 Electrical Characteristics (LDO)

(Unless specified otherwise, these are the electrical characteristics under the recommended operating environment.)

| Demonster                                         | 0                   | Condition                                                                                                                                                       |                             | Value |                             | 11   |

|---------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------|-----------------------------|------|

| Parameter                                         | Symbol              | Condition                                                                                                                                                       |                             | Тур   | Мах                         | Unit |

| Outeutustees                                      | N                   | VOUT_LDO pin, Load = 0.01 mA                                                                                                                                    | V <sub>SETLD</sub><br>×0.95 | -     | V <sub>SETLD</sub><br>×1.05 | v    |

| Output voltage V <sub>OUTI</sub>                  |                     | VOUT_LDO pin, Ta = +25°C, VIN_LDO = $V_{OUTLD}$ +1V<br>STBY_LDO = VINT (*1) , Load = 0.01 mA                                                                    | V <sub>SETLD</sub><br>×0.98 | -     | V <sub>SETLD</sub><br>×1.02 | v    |

| Input/output voltage difference<br>(Normal mode)  | V <sub>DELLD1</sub> | Between VIN_LDO and VOUT_LDO pins,<br>STBY_LDO = VINT (*1), Load $\leq$ 1 mA                                                                                    | 0.3                         | -     | -                           | V    |

| Input/output voltage difference<br>(Standby mode) | V <sub>DELLD2</sub> | Between VIN_LDO and VOUT_LDO pins,<br>STBY_LDO = AGND, Load ≤ 0.001 mA                                                                                          | 0.3                         | -     | -                           | v    |

| Maximum output current<br>(Normal mode)           | I <sub>OUTLD1</sub> | VOUT_LDO pin, (VIN_LDO-V <sub>OUTLD</sub> ×1.05) > 0.7V<br>STBY_LDO = VINT (*1)                                                                                 | 10                          | -     | -                           | mA   |

| Maximum output current<br>(Standby mode)          | I <sub>OUTLD2</sub> | VOUT_LDO pin, (VIN_LDO-V <sub>OUTLD</sub> ×1.05) > 0.7V,<br>STBY_LDO = AGND                                                                                     |                             | -     | -                           | mA   |

| Line regulation                                   | L <sub>INELD</sub>  | VOUT_LDO pin, VIN_LDO = (V <sub>OUTLD</sub> ×1.05+0.7V) to 5.3V                                                                                                 |                             | -     | 50                          | mV   |

| Load regulation<br>(Normal mode)                  | L <sub>OADLD1</sub> | VOUT_LDO pin,<br>STBY_LDO = VINT (*1) , Load = 1 mA to 10 mA                                                                                                    |                             | -     | 50                          | mV   |

| Load regulation<br>(Standby mode)                 | L <sub>OADLD2</sub> | VOUT_LDO pin,<br>STBY_LDO = AGND, Load = 0.001 mA to 0.1 mA                                                                                                     |                             | -     | 50                          | mV   |

| OVP operation current                             | I <sub>limld</sub>  | VOUT_LDO pin,<br>STBY_LDO = VINT (*1)                                                                                                                           |                             | 50    | 100                         | mA   |

| LDO consumption current<br>(Normal mode)          | I <sub>INLD1</sub>  | Sum of VINT and VIN_LDO input current, Ta = +25°C,<br>STBY_LDO = VINT (*1), Load = 0 mA                                                                         |                             | 6     | 9                           | μA   |

| LDO consumption current 2 (Standby mode)          | I <sub>INLD2</sub>  | Sum of VINT and VIN_LDO input current, Ta = +25°C,<br>STBY_LDO = AGND, Load = 0 mA,<br>VOUT_LDO resistance > 100 M $\Omega$ , V <sub>OUTLD</sub> setting = 1.3V |                             | 400   | 600                         | nA   |

| OFF current                                       | I <sub>OFFLD</sub>  | VIN_LDO pin, Ta = +25°C,<br>ENA_LDO = AGND                                                                                                                      |                             | 60    | 120                         | nA   |

| Discharge resistance                              | R <sub>DISLD</sub>  | VOUT_LDO pin,<br>$1.35 \le V_{OUTLD} \le 5.0V$                                                                                                                  | -                           | 1     | 2                           | kΩ   |

\*1: Refer to "Table 12-1 VINT Pin Voltage".

#### Table 11-5 Electrical Characteristics (Timer)

(Unless specified otherwise, these are the electrical characteristics under the recommended operating environment.)

| Parameter           | Symbol           | Condition                             |     | Value |     |      |

|---------------------|------------------|---------------------------------------|-----|-------|-----|------|

| Farameter           | Symbol           |                                       |     | Тур   | Max | Unit |

| Accuracy            | T <sub>ATM</sub> | Ta = +25°C                            | -15 | -     | +15 | %    |

| Each timer          | 1                | Timer 0, Timer 1, Timer 2, Ta = +25°C | _   | 30    | 45  | nA   |

| consumption current | IQTM             |                                       |     | 30    | 40  | ΠA   |

### 12. Functional Description

### **12.1** Power Supply Control

This IC can operate by two input power supplies, namely, the solar cell voltage VDD and the primary battery voltage VBAT.

When a capacitor is connected to the VSTORE2 pin, the surplus power of the solar cell accumulates in this capacitor and operates as input power supply.

The input power (from solar cell or VSTORE2 capacitor) is accumulated once in the capacitor connected to the VSTORE1 pin. When the voltage of the VSTORE1 pin reaches the threshold or higher, the power gating switch connects VSTORE1 to VOUT1 and VOUT2.

The input power (from primary battery) is not accumulated in the capacitor connected to the VSTORE1 pin. When the voltage of the VBAT pin reaches the threshold or higher, the switch for power gating connects VBAT to VOUT1 and VOUT2.

The VINT pin voltage is output as shown in the table below.

| VDD Voltage<br>(Solar Cell)               | VBAT Voltage<br>(Primary Battery) | VSTORE2 Voltage                           | VSTORE1 Voltage                   | VINT Voltage<br>(Output) |

|-------------------------------------------|-----------------------------------|-------------------------------------------|-----------------------------------|--------------------------|

|                                           |                                   | $V_{\text{DETL}}  \text{or}  \text{less}$ | -                                 | -                        |

|                                           | V <sub>DETL</sub> or less         | $V_{\text{DETH}} \text{ or higher}$       | -                                 | VSTORE2                  |

| $V_{\text{DETL}}  \text{or}  \text{less}$ |                                   | $V_{\text{DETL}}  \text{or}  \text{less}$ | -                                 | VBAT                     |

|                                           | $V_{\text{DETH}}$ or higher       | V or higher                               | V <sub>VOUTL</sub> detection (*1) | VBAT                     |

|                                           |                                   | V <sub>DETH</sub> or higher               | V <sub>VOUTH</sub> detection (*2) | VSTORE2                  |

|                                           |                                   | $V_{\text{DETL}}  \text{or}  \text{less}$ | -                                 | VDD                      |

|                                           | V <sub>DETL</sub> or less         | $V_{\text{DETH}} \text{ or higher}$       | -                                 | VDD                      |

| V or higher                               |                                   |                                           | V <sub>VOUTL</sub> detection (*1) | VBAT                     |

| $V_{\text{DETH}}$ or higher               | )/ enhishen                       | $V_{DETL}$ or less                        | V <sub>VOUTH</sub> detection (*2) | VDD                      |

|                                           | V <sub>DETH</sub> or higher       | V or higher                               | V <sub>VOUTL</sub> detection (*1) | VBAT                     |

|                                           |                                   | V <sub>DETH</sub> or higher               | V <sub>VOUTH</sub> detection (*2) | VDD                      |

Table 12-1 VINT Pin Voltage

\*1: Value from when voltage at VSTORE1 pin reaches  $V_{VOUTL}$  voltage until it reaches  $V_{VOUTH}$  voltage

\*2: Value from when voltage at VSTORE1 pin reaches  $V_{VOUTH}$  voltage until it reaches  $V_{VOUTL}$  voltage

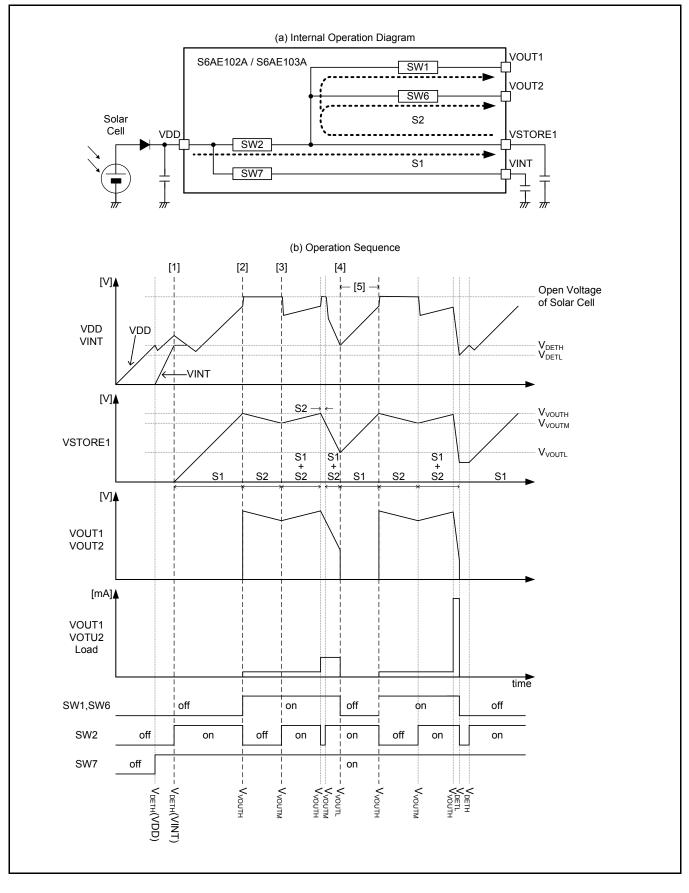

#### **VDD Input Power Operation**

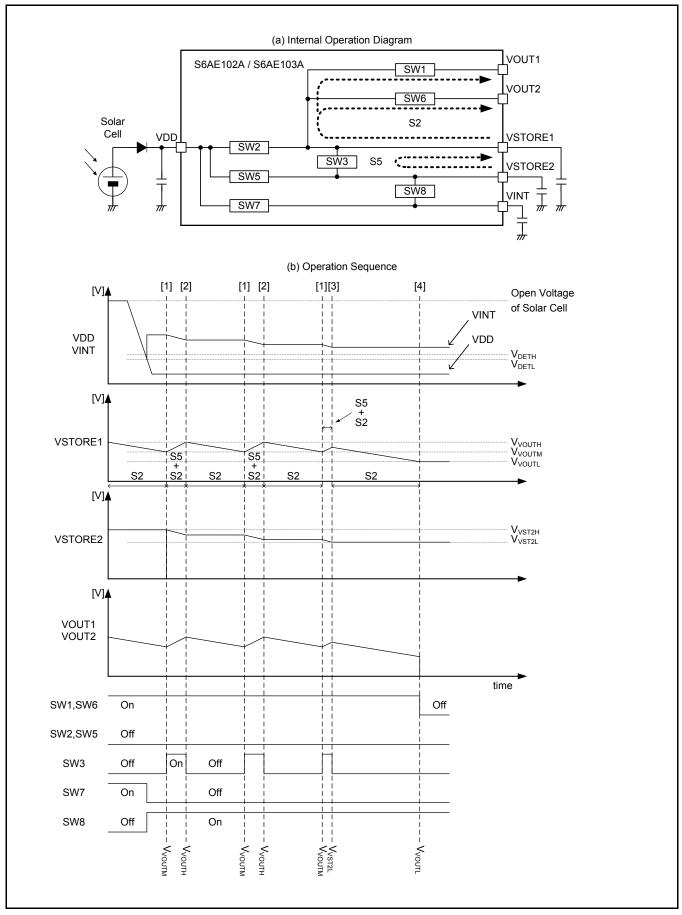

This section describes operation when the VDD pin is set as the input power (Figure 12-1).

When the voltage of the VBAT pin falls to the power undetection voltage ( $V_{DETL}$  = 1.45 V) or less, and a capacitor is not connected to the VSTORE2 pin.

- [1] When the voltage of the VDD pin reaches the power detection voltage ( $V_{DETH}$  = 1.55V) or higher, the switch (SW2) connects VDD and VSTORE1 (path S1). Also, when the voltage of the VDD pin falls to the power undetection voltage ( $V_{DETL}$  = 1.45V) or less, SW2 disconnects the path S1.

- [2] When the voltage of the VSTORE1 pin reaches the threshold value ( $V_{VOUTH}$ ) or higher that was set by the SET\_VOUTH pin, SW2 disconnects the path S1. Also, the VOUT1 switch (SW1) connects VSTORE1 and VOUT1, and the VOUT2 switch (SW6) connects VSTORE1 and VOUT2 (path S2).

- [3] When the voltage of the VSTORE1 pin falls to the input power reconnect voltage (V<sub>VOUTM</sub>) or less, SW2 connects the path S1 (path S1+S2).

- [4] In addition, when the voltage falls to the threshold value ( $V_{VOUTL}$ ) or less that was set by the SET\_VOUTL pin, SW1 and SW6 disconnect the path S2.

- [5] When SW1 and SW6 disconnects the path S2, the discharge function is activated.

#### Figure 12-1 VDD Input Power Operation

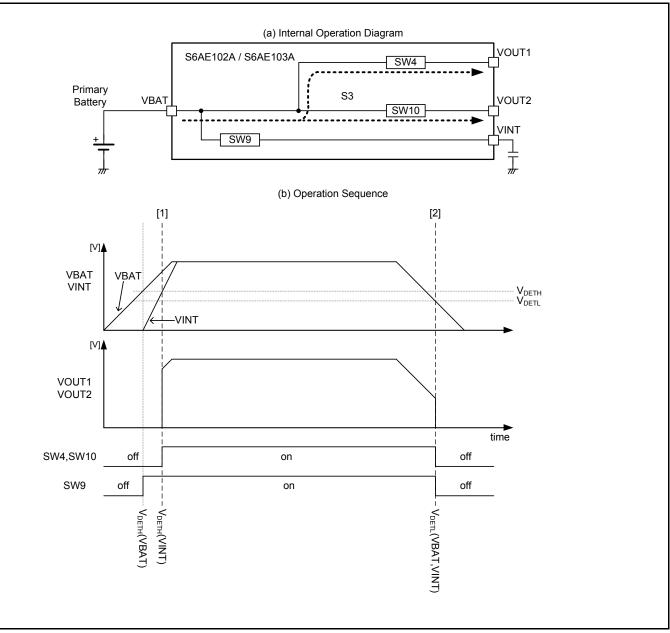

#### **VBAT Input Power Operation**

This section describes operation when the VBAT pin is set as the input power (Figure 12-2).

When the voltage of the VDD pin falls to the power undetection voltage ( $V_{DETL}$  = 1.45 V) or less, and a capacitor is not connected to the VSTORE2 pin.

[1] When the voltage of the VBAT pin reaches the power detection voltage (V<sub>DETH</sub> = 1.55V) or higher, the switch (SW4) connects VBAT and VOUT1, and the switch (SW10) connects VBAT and VOUT2 (path S3).

[2] When the voltage of the VBAT pin falls to the power undetection voltage ( $V_{DETL}$  = 1.45V) or less, SW4 and SW10 disconnects the path S3.

### Figure 12-2 VBAT Input Power Operation

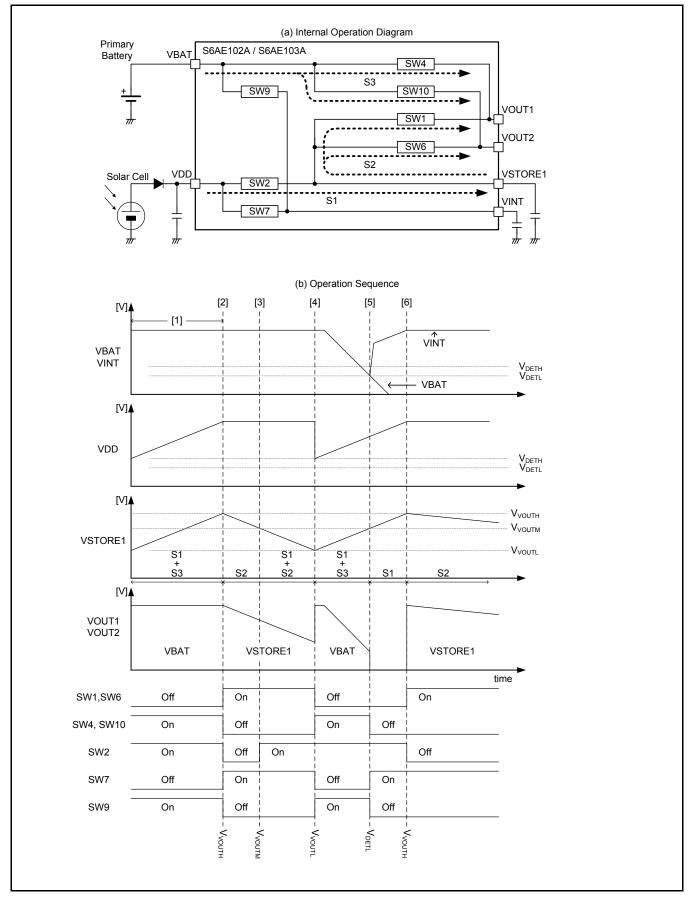

#### **VDD/VBAT Input Power Operation**

This section describes operation when the VDD and VBAT pins are set as the input power (Figure 12-3).

A capacitor is not connected to the VSTORE2 pin.

- [1] When the voltage of the VDD pin and the VBAT pin reaches the power detection voltage ( $V_{DETH}$  = 1.55 V) or higher and the voltage of the VSTORE1 pin is not detected as the VOUT upper limit voltage ( $V_{VOUTH}$ ), the VOUT1 switch (SW4) connects VBAT and VOUT1 and the VOUT2 switch (SW10) connects VBAT and VOUT2 (path S3). Also, the switch (SW2) connects VDD and VSTORE1 (path S1).

- [2] When the voltage of the VSTORE1 pin reaches the VOUT upper limit voltage (V<sub>VOUTH</sub>) or higher, SW4 and SW10 disconnect path S3.Also, the VOUT1 switch (SW1) connects VSTORE1 and VOUT1 and the VOUT2 switch (SW6) connects VSTORE1 and VOUT2 (path S2).

- [3] When the voltage of the VSTORE1 pin falls to the input power reconnect voltage (V<sub>VOUTM</sub>) or less, SW2 connects path S1 (path S1 + S2).

- [4] When the voltage of the VSTORE1 pin falls to the VOUT lower limit voltage (V<sub>VOUTL</sub>) or less, switches SW1 and SW6 disconnect path S2. Also, SW4 and SW10 connect path S3 (path S1 + S3).

- [5] When the voltage of the VBAT pin falls to the power undetection voltage (V<sub>DETL</sub> = 1.45 V) or less, switches SW4 and SW10 disconnect path S3.

- [6] When the voltage of the VSTORE1 pin reaches the VOUT upper limit voltage (V<sub>VOUTH</sub>) or higher, SW1 and SW6 connect path S2 (path S2).

#### Figure 12-3 VDD/VBAT Input Power Operation

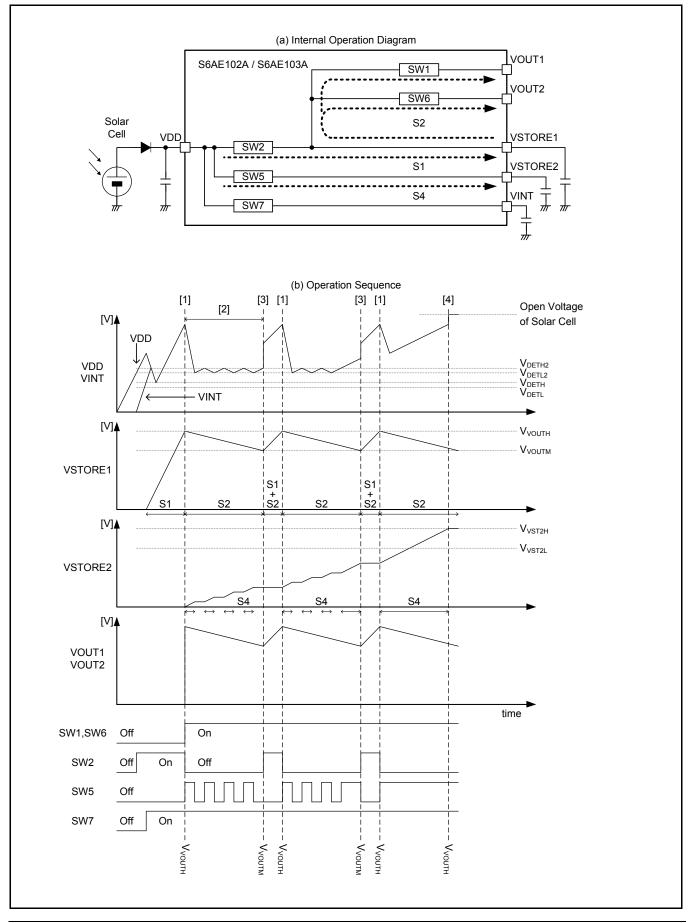

#### **VDD/VSTORE2** Input Power Operation

This section describes operation when the VDD pin is set as the input power (Figure 12-4).

A capacitor is connected to the VSTORE2 pin.

- [1] When the voltage of the VSTORE1 pin reaches the threshold value (V<sub>VOUTH</sub>) or higher that was set by the SET\_VOUTH pin, switch (SW5) connects VDD and VSTORE2 (path S4).

- [2] When the voltage of the VDD pin falls to the power undetection voltage 2 (V<sub>DETL2</sub> = 2.0 V) or less, SW5 disconnects path S4. When it reaches the power detection voltage 2 (V<sub>DETH2</sub> = 2.1 V) or higher, SW5 connects path S4.

- [3] When the voltage of the VSTORE1 pin falls to the threshold value (V<sub>VOUTM</sub>) or less that was set by the SET\_VOUTH pin, SW5 disconnects path S4.

- [4] When the voltage of the VSTORE2 pin reaches the VSTORE2 upper limit voltage (V<sub>VST2H</sub>) or higher, SW5 disconnects path S4.

#### Figure 12-4 VDD/VSTORE2 Input Power Operation

#### **VSTORE2** Input Power Operation

This section describes operation when the VSTORE2 pin is set as the input power (Figure 12-5).

A capacitor is connected to the VSTORE2 pin.

- [1] When the voltage of the VDD pin falls to the power undetection voltage (V<sub>DETL</sub> = 1.45 V) or less, and when the voltage of the VSTORE1 pin falls to the threshold value (V<sub>VOUTM</sub>) or less set by SET\_VOUTH pin, switch (SW3) connects VSTORE2 and VSTORE1 (path S5 + S2).

- [2] When the voltage of the VSTORE1 pin reaches the threshold value (V<sub>VOUTH</sub>) or higher that was set by the SET\_VOUTH pin, SW3 disconnects path S5.

- [3] When the voltage of the VSTORE2 pin falls to the VSTORE2 lower limit voltage (V<sub>VST2L</sub>) or less, SW3 disconnects path S5.

- [4] When the voltage of the VSTORE1 pin falls to the threshold value (V<sub>VOUTL</sub>) or less that was set by the SET\_VOUTL pin, the VOUT1 switch (SW1) disconnects VSTORE1 and VOUT1 and the VOUT2 switch (SW6) disconnects VSTORE1 and VOUT2.

#### Figure 12-5 VSTORE2 Input Power Operation

### 12.2 Power Gating

This IC has a power gating function for external systems.

The power gating function is to control supplying power accumulated in VSTORE1 or power from VBAT to external system loads connected to VOUT1 and VOUT2 by internal switches.

The power gating function has four operating modes.

This IC determines the power gating operation mode through the connection status of pins CIN1 and CIN2 at the power detection ( $V_{DETH}$  = 1.55 V) timing of the VINT pin.

| Table 12-2 Power Gating Operation Mode |  |

|----------------------------------------|--|

|----------------------------------------|--|

| Each Pir               | n Settings             | Operation Mode           |  |  |

|------------------------|------------------------|--------------------------|--|--|

| CIN1(*1)               | CIN2                   | Operation Mode           |  |  |

| Open                   | Open                   | Energy driven mode       |  |  |

| Open                   | Connect AGND           | Event driven mode 1      |  |  |

| Connect capacitor (*2) | Open                   | Event driven mode 2 (*1) |  |  |

| Connect capacitor (*2) | Connect capacitor (*2) | Timer driven mode (*1)   |  |  |

\*1: S6AE103A only

\*2: For the timer time setting, refer to"14.1 Setting the Operation Conditions".

#### **Energy Driven Mode**

1) VDD input power operation

Switches are controlled by monitoring VSTORE1 voltage.

Internal switches (SW1 and SW6) connect VSTORE1 and VOUT1, as well as VSTORE1 and VOUT2 from when VOUT upper limit voltage ( $V_{VOUTH}$ ) is detected until VOUT lower limit ( $V_{VOUTL}$ ) is detected.

2) VBAT input power operation

Switches are controlled by monitoring VBAT voltage.

Internal switches (SW4 and SW10) connect VBAT and VOUT1, as well as VBAT and VOUT2 from when power detection voltage ( $V_{DETH}$ ) is detected until power undetection voltage ( $V_{DETL}$ ) is detected.

#### **Event Driven Mode 1**

Switches are controlled in the same way as the energy driven mode to supply to VOUT1. The INT input controls switching to supply to VOUT2. While the timer 0 is counting, the flag output (T0TM) disables internal switching controls through INT input. The timer time (T0) is set by the capacitor connected to CIN0.

1) VDD input power operation

Internal switch (SW6) connects VSTORE1 to VOUT2 while INT is high level. Detecting upper limit voltage ( $V_{VOUTH}$ ) is a trigger to start timer 0, after the timer time reaches count (T0), it stops and is reset.

2) VBAT input power operation

Internal switch (SW10) connects VBAT to VOUT2 while INT is high level. Detecting power detection voltage ( $V_{DETH}$ ) is a trigger to start timer 0, after the timer time reaches count (T0), it stops and is reset.

#### **Event Driven Mode 2**

Switches are controlled in the same way as the energy driven mode to supply to VOUT1. The INT input and the flag output (T1TM) control switching to supply to VOUT2.

1) VDD input power operation

Detecting upper limit voltage ( $V_{VOUTH}$ ) is a trigger to start counter, after the timer time reaches count (T0), timer 0 stops and is reset. When the timer time (T0) is set by the capacitor connected to CIN0.

The highness of INT is a trigger to start counter, after the timer time reaches count (T1), timer 1 stops and is reset. When the timer time (T1) is set by the capacitor connected to CIN1.

For each timer, they are reset by detecting VOUT lower limit voltage (V<sub>VOUTL</sub>).

Internal switch (SW6) connects VSTORE1 to VOUT2 while timer 1 is counting. Disables internal switching controls through INT input while the timer 0 is counting.

2) VBAT input power operation

Detecting power detection voltage ( $V_{DETH}$ ) is a trigger to start counter, after the timer time reaches count (T0), timer 0 stops and is reset. When the timer time (T0) is set by the capacitor connected to CIN0.

The highness of INT is a trigger to start counter, after the timer time reaches count (T1), timer 1 stops and is reset. When the timer time (T1) is set by the capacitor connected to CIN1.

Each timer is reset by detecting power undetection voltage (V<sub>DETL</sub>).

Internal switch (SW10) connects VBAT to VOUT2 while timer 1 is counting. Disables internal switching controls through INT input while the timer 0 is counting.

#### **Timer Driven Mode**

The timer 0 flag output (T0TM), timer 1 flag output (T1TM), and timer 2 flag output (T2TM) control switching to supply to VOUT1 and VOUT2

1) VDD input power operation

This section describes the operation of each timer.

Detecting upper limit voltage ( $V_{VOUTH}$ ) the first time is a trigger to start counter, after the timer time reaches count (T0), timer 0 stops and is reset. From the second time onward, the completion of timer 2 is a trigger to start the count, after the timer time reaches count (T0), the timer stops and is reset. When the timer time (T0) is set by the capacitor connected to CIN0.

Detecting upper limit voltage ( $V_{VOUTH}$ ) the first time is a trigger to start counter, after the timer time reaches count (T1), timer 1 stops and is reset. From the second time onward, the completion of timer 2 is a trigger to start the count, after the timer time reaches count (T1), the timer stops and is reset. When the timer time (T1) is set by the capacitor connected to CIN1.

The completion of timer 1 is a trigger to start counter, after the timer time reaches count (T2), timer 2 stops and is reset. When the timer time (T2) is set by the capacitor connected to CIN2.

Timer 0 and 1 are reset by detecting VOUT lower limit voltage ( $V_{VOUTL}$ ). Timer 2 is reset by power undetection voltage ( $V_{DETL}$ ) of VINT.

This section describes the operation of VOUT1.

Internal switch (SW1) connects VSTORE1 to VOUT1 while timer 1 is counting. Internal switch (SW1) disconnects VSTORE1 and VOUT1 while timer 2 is counting.

This section describes the operation of VOUT2.

Internal switch (SW6) connects VSTORE1 to VOUT2 while timer 1 is counting after timer 0 ends. Internal switch (SW6) disconnects VSTORE1 and VOUT2 while timer 2 is counting.

#### 2) VBAT input power operation

This section describes the operation of each timer.

Detecting power detection voltage ( $V_{DETH}$ ) the first time is a trigger to start counter, after the timer time reaches count (T0), timer 0 stops and is reset. From the second time onward, the completion of timer 2 is a trigger to start the count, after the timer time reaches count (T0), the timer stops and is reset. When the timer time (T0) is set by the capacitor connected to CIN0.

Detecting power detection voltage ( $V_{DETH}$ ) the first time is a trigger to start counter, after the timer time reaches count (T1), timer 1 stops and is reset. From the second time onward, the completion of timer 2 is a trigger to start the count, after the timer time reaches count (T1), the timer stops and is reset. When the timer time (T1) is set by the capacitor connected to CIN1.

The completion of timer 1 is a trigger to start counter, after the timer time reaches count (T2), timer 2 stops and is reset. When the timer time (T2) is set by the capacitor connected to CIN2.

Each timer is reset by detecting power undetection voltage (V<sub>DETL</sub>).

This section describes the operation of VOUT1.

Internal switch (SW4) connects VBAT to VOUT1 while timer 1 is counting. Internal switch (SW4) disconnects VBAT and VOUT1 while timer 2 is counting.

This section describes the operation of VOUT2.

Internal switch (SW10) connects VBAT to VOUT2 while timer 1 is counting after timer 0 ends. Internal switch (SW10) disconnects VBAT and VOUT2 while timer 2 is counting.

ſ

#### Figure 12-6 Power Gating Operation (VDD Input Power)

| V:                                                                                                                   | STORE1 < V <sub>VOUTL</sub>                           | /<br>\                             |           | From          | after VSTORE1 re | eaches V <sub>VOUTH</sub> u | ntil V <sub>VOUTL</sub>                                        |       |                        | VSTORE1 < V        |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------|-----------|---------------|------------------|-----------------------------|----------------------------------------------------------------|-------|------------------------|--------------------|

| SW1                                                                                                                  | OFF                                                   | ON                                 |           |               |                  |                             |                                                                |       |                        | ON                 |

| SW6                                                                                                                  | OFF                                                   | ON                                 |           |               |                  |                             |                                                                |       |                        | OFF                |

| vent drive                                                                                                           | <b>en mode 1</b> (S64                                 | AE102A / S                         | 6AE103A)  |               |                  |                             |                                                                |       |                        |                    |

| V                                                                                                                    | STORE1 < V <sub>VOUTL</sub>                           |                                    |           | From          | after VSTORE1 re | eaches V <sub>VOUTH</sub> u | ntil V <sub>VOUTL</sub>                                        |       |                        | VSTORE1 < V        |

| INT -                                                                                                                | LH                                                    | H                                  |           | Н             |                  | н                           |                                                                |       | н                      |                    |

| тотм                                                                                                                 |                                                       |                                    | Т0        |               | STOP<br>RESET    |                             |                                                                |       |                        |                    |

| SW1                                                                                                                  | OFF                                                   | ON                                 |           |               |                  |                             |                                                                |       |                        | OFF                |

| SW6                                                                                                                  | OFF                                                   | <u>.</u>                           | OFF       |               | ×                | ON                          | o                                                              | FF    | ON                     | OFF                |

| -                                                                                                                    | STORE1 < V <sub>VOUTL</sub>                           |                                    |           | From          | after VSTORE1 re |                             | Intil V <sub>VOUTL</sub>                                       |       |                        | VSTORE1 < V        |

| V                                                                                                                    | STORE1 < V <sub>VOUTL</sub>                           |                                    |           | From          | after VSTORE1 re | eaches V <sub>VOUTH</sub> u | ntil V <sub>VOUTL</sub>                                        |       |                        | VSTORE1 < V        |

| INT -                                                                                                                | LH                                                    | START                              | Н         |               |                  | н                           |                                                                |       | н                      |                    |

| тотм _                                                                                                               |                                                       |                                    | ТО        | STOP<br>RESET |                  | CTADT                       |                                                                |       | CTADT                  |                    |

| T1TM                                                                                                                 |                                                       |                                    |           |               |                  | START                       |                                                                |       | ¥START<br>T1           | ▼<br>→ RESET       |

|                                                                                                                      |                                                       |                                    |           |               |                  |                             |                                                                |       |                        | _                  |

| SW1                                                                                                                  | OFF                                                   | C                                  | ON        |               |                  |                             |                                                                |       |                        | OFF                |

| SW1<br>SW6                                                                                                           | OFF                                                   |                                    | DN<br>DFF | *             |                  | ON                          | o                                                              | FF    | ON                     | OFF                |

| SW6                                                                                                                  |                                                       | <u> </u>                           |           | ,<br>,        |                  | ON                          | 0                                                              | FF    | ON                     | -                  |

| -<br>SW6<br>-<br>mer drive                                                                                           | OFF                                                   | <u> </u>                           |           | From          | after VSTORE1 re |                             |                                                                |       | ON                     | OFF                |

| -<br>SW6<br>-<br>mer drive                                                                                           | OFF<br>en mode (S6AE<br>STORE1 < V <sub>voutr</sub> ) | C<br>103A)<br>                     |           | From          | after VSTORE1 re | eaches V <sub>VOUTH</sub> u | Intil V <sub>VOUTL</sub><br>START<br>T0                        |       | ON                     | -                  |

| -<br>SW6<br>-<br>mer drive<br>-<br>vi<br>-                                                                           | OFF<br>en mode (S6AE<br>STORE1 < V <sub>voutr</sub> ) | 0<br>103A)<br>                     | DFF       | STOP          | г                | eaches V <sub>VOUTH</sub> u | Intil V <sub>VOUTL</sub>                                       | ∫ѕтор | <br>STOP<br>→ RESET    | OFF                |

| SW6<br>-<br>mer drive<br>-<br>-<br>-<br>-<br>TOTM<br>-                                                               | OFF<br>en mode (S6AE<br>STORE1 < V <sub>voutr</sub> ) | 0<br>103A)<br>START<br>T0<br>START | DFF       | STOP          | г                | eaches V <sub>VOUTH</sub> U | Intil V <sub>VOUTL</sub><br>START<br>T0<br>START               | ∫ѕтор | <br>                   | OFF                |

| SW6<br>-<br>mer drive<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | OFF<br>en mode (S6AE<br>STORE1 < V <sub>voutr</sub> ) | 0<br>103A)<br>START<br>T0<br>START | DFF       | STOP          | T2               | eaches V <sub>VOUTH</sub> U | Intil V <sub>VOUTL</sub><br>START<br>T0<br>START<br>T1<br>STOP | ∫ѕтор | STOP<br>RESET<br>START | OFF<br>VSTORE1 < V |

#### Figure 12-7 Power Gating Operation (VBAT Input Power)

|          | VBAT < V <sub>DETL</sub> | X                    |          | Fn                 | om after VBAT rea | aches V <sub>DETH</sub> unti | I V <sub>DETL</sub> |      |                 | VBAT < V <sub>DE</sub>  |

|----------|--------------------------|----------------------|----------|--------------------|-------------------|------------------------------|---------------------|------|-----------------|-------------------------|

| SW4      | OFF                      | ON                   |          |                    |                   |                              |                     |      |                 | ON                      |

| SW10     | OFF                      | ON                   |          |                    |                   |                              |                     |      |                 | OFF                     |

| ent driv | <b>/en mode 1</b> (S6    | AE102A / S           | 6AE103A) |                    |                   |                              |                     |      |                 |                         |

|          | VBAT < V <sub>DETL</sub> | ×                    |          | Fr                 | om after VBAT rea | aches V <sub>DETH</sub> unti | I V <sub>detl</sub> |      |                 | VBAT < VDET             |

| INT      | LH                       | Н                    |          | н                  |                   | н                            |                     |      | н               |                         |

| тотм     |                          | ↓ START              | T0       |                    | STOP<br>RESET     |                              |                     |      |                 |                         |

| SW4      | OFF                      | ON                   |          |                    |                   |                              |                     |      |                 | OFF                     |

| SW10     | OFF                      | K                    | OFF      |                    | *                 | ON                           |                     | DFF  | ON              | OFF                     |

| ent driv | <b>/en mode 2</b> (S6    | AE103A)              |          |                    |                   |                              |                     |      |                 |                         |